|

|

PDF MC33989 Data sheet ( Hoja de datos )

| Número de pieza | MC33989 | |

| Descripción | System Basis Chip with High Speed CAN Transceiver | |

| Fabricantes | Motorola Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de MC33989 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Order this document by

MOTOROLA

Rev: 4.91 Date: 10th July, 2002

SEMICONDUCTORFreescale

TECHNICAL DATA

Semiconductor,

Inc.

XC33989

Advance Information

System Basis Chip with

High Speed CAN Transceiver

The MC33989 is a monolithic integrated circuit combining many functions

frequently used by automotive ECUs. It incorporates:

- Two voltage regulators.

- Four high voltage inputs.

- 1Mbaud CAN physical interface.

SYSTEM BASIS CHIP

WITH HIGH SPEED CAN

SEMICONDUCTOR

TECHNICAL DATA

• Vdd1: Low drop voltage regulator, current limitation, over temperature

detection, monitoring and reset function

• Vdd1: Total current capability 200mA.

• V2: Tracking function of Vdd1 regulator. Control circuitry for external bipolar

ballast transistor for high flexibility in choice of peripheral voltage and current

supply.

• Four operational modes (normal, stand-by, stop and sleep mode)

• Low stand-by current consumption in stop and sleep modes

• High speed 1MBaud CAN physical interface.

• Four external high voltage wake-up inputs, associated with HS1 Vbat switch

• 150mA output current capability for HS1 Vbat switch allowing drive of external

switches pull up resistors or relays

• Vsup failure detection

• Nominal DC operating voltage from 5.5 to 27V, extended range down to 4.5V.

• 40V maximum transient voltage

• Programmable software time out and window watchdog

• Safe mode with separate outputs for Watchdog time out and Reset

• Wake up capabilities (four wake up inputs, programmable cyclic sense,

forced wake up, CAN interface, SPI and stop mode over current)

• Interface with MCU through SPI

Simplified Block Diagram

Vbat

Q1

V2CTRL

V2

DW SUFFIX

PLASTIC PACKAGE

CASE 751-F

(SO-28)

PIN CONNECTIONS

RX 1

TX 2

Vdd1 3

Reset 4

INTB 5

GND 6

GND 7

GND 8

GND 9

V2 10

V2ctrl 11

Vsup 12

HS1 13

L0 14

28 WDOGB

27 CSB

26 MOSI

25 MISO

24 SCLK

23 GND

22 GND

21 GND

20 GND

19 CANL

18 CANH

17 L3

16 L2

15 L1

Vsup

Vsup monitor

Dual Voltage Regulator

Vdd1 Monitor

5V/200mA

sCuApNply Vdd1

HS1

L0

L1

L2

L3

CAN H

Rterm

CAN L

HS1 control

Programmable

wake-up input

Mode control

Oscillator

Interrupt

Watchdog

Reset

SPI

INTB

WDOGB

Reset

MOSI

SCLK

MISO

CSB

High Speed 1Mbit/s

CAN

Physical Interface

V2

TX

RX

Gnd

ORDERING INFORMATION

Device

Operating

Temperature Range

Package

PC33989DW TA = -40 to 125°C

SO-28

For More Information On This Product,

Go to: www.freescale.com

This document contains information on a product under development. Motorola reserves the right

to change or discontinue this product without notice.

Motorola,Inc 2002

1 page

MC33989

Freescale Semiconductor, Inc.

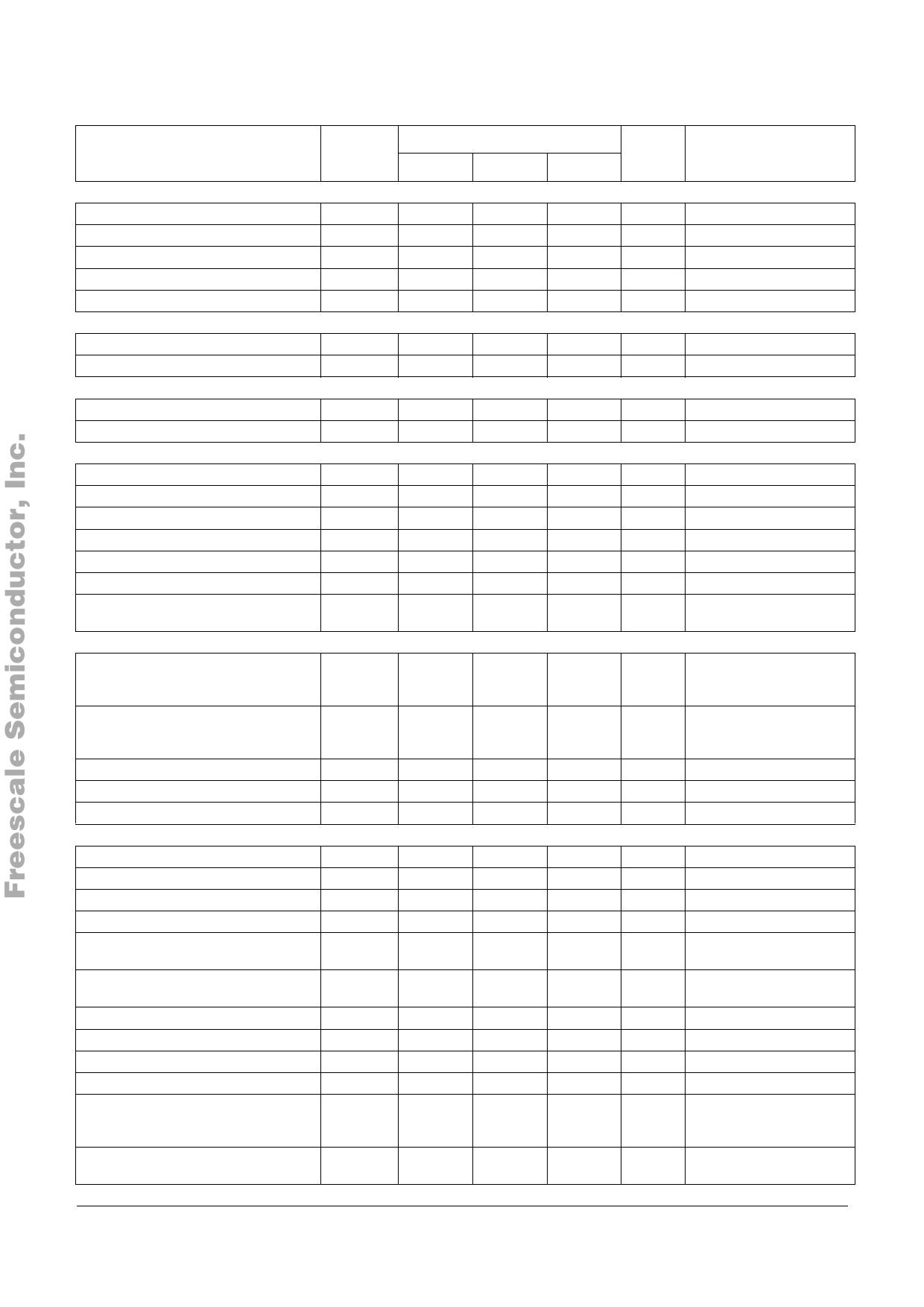

(Vsup From 5.5V to 18V and Tamb -40°C to 125°C)

For all pins except CANH, CANL, Tx and Rx which are described in the CAN module section

Description

Symbol

Characteristics

Min Typ Max

Unit

Reset Pin (output pin only, supply from Vdd1. Structure switch to gnd with pull up current source)

High Level Output current

Ioh

-300

-250

-150

uA

Low Level Output Voltage (I0=1.5mA)

Low Level Output Voltage (I0=tbd mA)

Reset pull down current

Vol

Vol

Ipdw

0

0

2.3

0.9 V

0.9 V

5 mA

Reset Duration after Vdd1 High

reset-dur

3

3.4

4 ms

Wdogb output pin (Push pull structure)

Low Level Output Voltage (I0=1.5mA)

High Level Output Voltage (I0=-250uA)

INT Pin( Push pull structure)

Vol 0

Voh Vdd1-0.9

0.9

Vdd1

V

Low Level Output Voltage (I0=1.5mA)

High Level Output Voltage (I0=-250uA)

HS1: 150mA High side output pin

Vol 0

Voh Vdd1-0.9

0.9

Vdd1

V

Rdson at Tj=25°C, and Iout -150mA

Ron25

2 2.5 Ohms

Rdson at Ta=125°C, and Iout -150mA

Ron125

4.5 Ohms

Rdson at Ta=125°C, and Iout -120mA

Ron125-2

3.5 5.5 Ohms

Output current limitation

Ilim 160

500 mA

Over temperature Shutdown

Ovt 155

190 °C

Leakage current

Ileak

10 uA

Output Clamp Voltage at Iout= -10mA

Vcl -1.5

-0.3 V

L0, L1, L2, L3 inputs

Negative Switching Threshold

Vthn

2

2.5

3

V

2.5 3 3.6

2.7 3.2 3.7

Positive Switching Threshold

Vthp

2.7

3.3

3.8

V

3 4 4.6

3.5 4.2 4.7

Hysteresis

Vhyst

0.6

1.3 V

Input current

Iin -10

10 uA

Wake up Filter Time

Twuf

8

20 38 us

DIGITAL INTERFACE TIMING

SPI operation frequency

Freq

0.25

4 MHz

SCLK Clock Period

SCLK Clock High Time

SCLK Clock Low Time

Falling Edge of CS to Rising

Edge of SCLK

tpCLK

twSCLKH

twSCLKL

tlead

250

125

125

100

N/A ns

N/A ns

N/A ns

N/A ns

Falling Edge of SCLK to Rising Edge of

CS

tlag

100

N/A ns

MOSI to Falling Edge of SCLK

Falling Edge of SCLK to MOSI

MISO Rise Time (CL = 220pF)

MISO Fall Time (CL = 220pF)

Time from Falling or Rising Edges of CS to:

- MISO Low Impedance

- MISO High Impedance

Time from Rising Edge of SCLK to MISO

Data Valid

tSISU

tSIH

trSO

tfSO

tSOEN

tSODIS

tvalid

40

40

N/A ns

N/A ns

25 50 ns

25 50 ns

50 ns

50

50 ns

MC33989

For More Information On This Product,

Go to: www.freescale.com

Conditions

0<Vout<0.7Vdd

5.5v<Vsup<27V

1v<Vsup<5.5V

V>0.9V

1v<Vsup<27V

Vsup>9V

Vsup>9V

5.5<Vsup<9V

no inductive load drive

capability

5.5V<Vsup<6V

6V<Vsup<18V

18V<Vsup<27

5.5V<Vsup<6V

6V<Vsup<18V

18V<Vsup<27

5.5V<Vsup<27

-0.2V < Vin < 40V

0.2 V1=<MISO>=0.8V1,

CL=200pF

5

5 Page

MC33989

Freescale Semiconductor, Inc.

diagram to be inserted

Figure 5. Wake up block diagram

The block diagram illustrates how the wake up signal is generated. First the CAN signal is detected by a low consumption

receiver (WU receiver). Then the signal passes through a pulse width filter which discards the undesired pulses. The pulse must

have a width bigger than 0.5us and smaller than 500us to be acepted. When a pulse is discarded the pulse counter is reseted

and no wake signal is generated, otherwise when a pulse is acepted the pulse counter is incremented and after three pulses the

wake signal is asserted.

Each one of the pulses must be spaced by no more than 500us. In that case the pulse counter is reset and no wake signal is

generated. This is accomplished by the wake time-out generator. The wake up cycle is completed (and the wake flag reset)

when the CAN interface is brought to “CAN normal” mode.

The wake up capability of the CAN can be disabled, refer to SPI interface and register section, CAN register.

MC33989

For More Information On This Product,

Go to: www.freescale.com

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet MC33989.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MC33981 | High-Frequency / High-Current / Self-Protected High-Side Switch | Motorola Semiconductors |

| MC33981B | Single High-Side Switch | Freescale Semiconductor |

| MC33982 | Single Intelligent High-Current Self-Protected Silicon High-Side Switch | Motorola Semiconductors |

| MC33982B | Single Intelligent High-Current Self-Protected Silicon High-Side Switch | Freescale Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |