|

|

PDF COPCH881C Data sheet ( Hoja de datos )

| Número de pieza | COPCH881C | |

| Descripción | Microcontrollers | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de COPCH881C (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

August 1996

COP880C

Microcontrollers

General Description

The following part numbers are pin count and tempera-

ture variations of the COP880C: COP680C/COP681C/

COP682C/COP881C

/COP882C/COP980C/

COP981C/COP982C.

The COP880C devices are members of the COP8 microcon-

troller family. They are fully static parts, fabricated using

double-metal silicon gate microCMOS technology. This low

cost microcontroller is a complete microcomputer containing

all system timing, interrupt logic, ROM, RAM, and I/O nec-

essary to implement dedicated control functions in a variety

of applications. Features include an 8-bit memory mapped

architecture, MICROWIRE/PLUS™ serial I/O, a 16-bit timer/

counter with capture register and a multi-sourced interrupt.

Each I/O pin has software selectable options to adapt the

device to the specific application. The part operates over a

voltage range of 2.5 to 6.0V. High throughput is achieved

with an efficient, regular instruction set operating at a 1

microsecond per instruction rate.

Key Features

n — 16-bit multi-function timer supporting

— PWM mode

— External event counter mode

— Input capture mode

n 4 kbytes of ROM

n 128 bytes of RAM

I/O Features

n Memory mapped I/O

n Software selectable I/O options (TRI-STATE®, Push-Pull,

Weak Pull-Up Input, High Impedance Input)

n High current outputs (8 pins)

n Schmitt trigger inputs on Port G

n MICROWIRE PLUS serial I/O

n Packages:

— 20 DIP/SO with 16 I/O pins

— 28 DIP/SO with 24 I/O pins

— 40 DIP, 36 I/O pins

— 44 PLCC, 36 I/O pins

CPU/Instruction Set Features

n 1 µs instruction cycle time

n Three multi-source interrupts servicing

— External interrupt with selectable edge

— Timer interrupt

— Software interrupt

n Versatile and easy to use instruction set

n 8-bit Stack Pointer (SP) — stack in RAM

n Two 8-bit Register Indirect Data Memory Pointers

(B and X)

Fully Static CMOS

n Low current drain (typically < 1 µA)

n Single supply operation: 2.5V to 6.0V

n Temperature ranges: 0˚C to 70˚C, −40˚C to +85˚C,

−55˚C to +125˚C.

Development Support

n Emulation and OTP devices

n Real time emulation and full program debug offered by

MetaLink’s development system

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

COPS™, HPC™, MICROWIRE™ and MICROWIRE/PLUS™ are trademarks of National Semiconductor Corporation.

iceMASTER™ is a trademark of MetaLink Corporation.

PC-XT® and PC-AT® are registered trademarks of International Business Machines Corporation.

© 2001 National Semiconductor Corporation DS010802

www.national.com

1 page

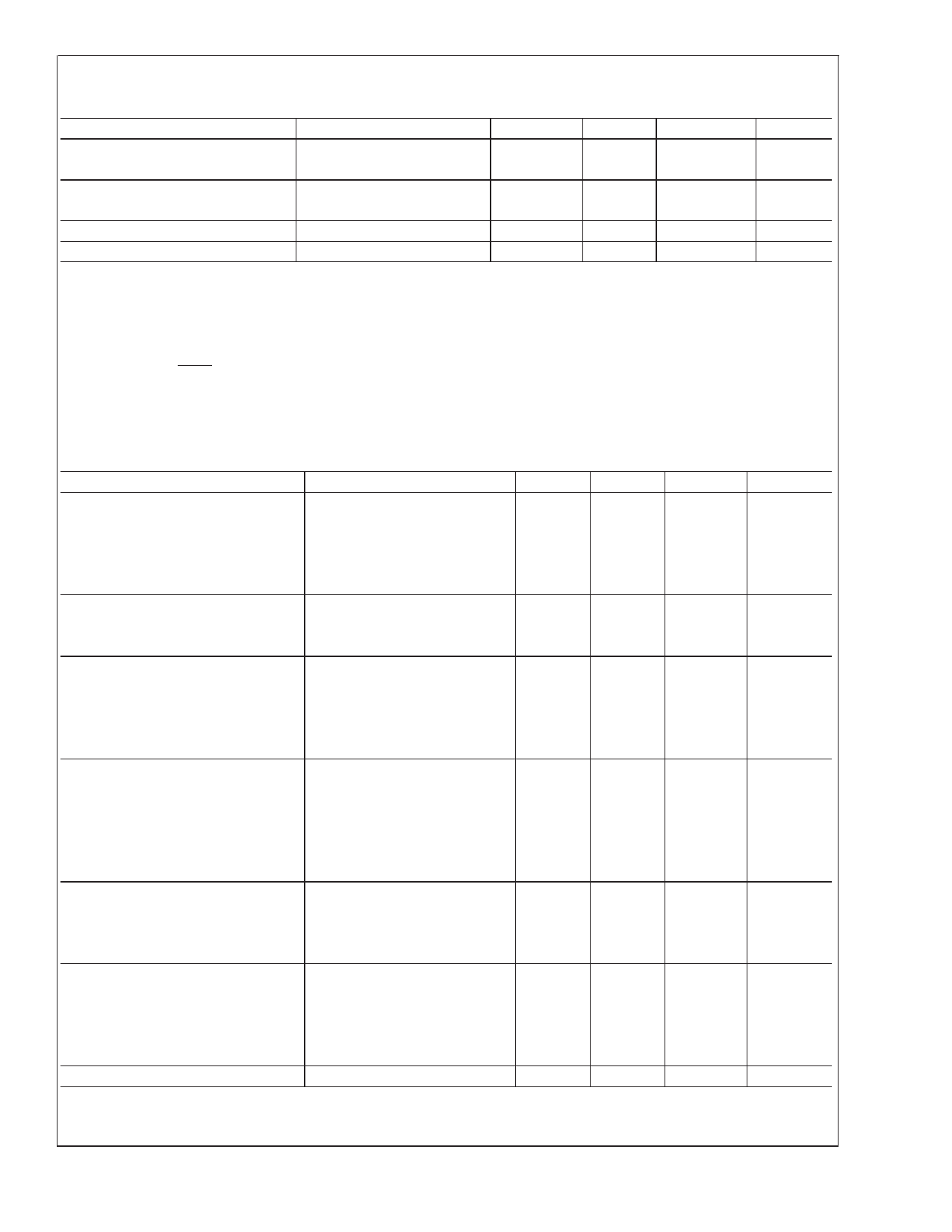

DC Electrical Characteristics (Continued)

COP98xC; 0˚C ≤ TA ≤ +70˚C unless otherwise specified

Parameter

Condition

Maximum Input Current (Note 5)

Without Latchup (Room Temp)

Room Temp

RAM Retention Voltage, Vr

500 ns Rise and

(Note 6)

Fall Time (Min)

Input Capacitance

Load Capacitance on D2

Min Typ Max Units

±100

mA

2.0 V

7 pF

1000

pF

COP980C/COP981C/COP982C

Note 2: Rate of voltage change must be less than 0.5V/ms.

Note 3: Supply current is measured after running 2000 cycles with a square wave CKI input, CKO open, inputs at rails and outputs open.

Note 4: The HALT mode will stop CKI from oscillating in the RC and the Crystal configurations. Test conditions: All inputs tied to VCC, L, C and G ports TRI-STATE

and tied to ground, all outputs low and tied to ground.

Note 5: Pins G6 and RESET are designed with a high voltage input network for factory testing. These pins allow input voltages greater than VCC and the pins will

have sink current to VCC when biased at voltages greater than VCC (the pins do not have source current when biased at a voltage below VCC). The effective

resistance to VCC is 750Ω (typ). These two pins will not latch up. The voltage at the pins must be limited to less than 14V.

Note 6: To maintain RAM integrity, the voltage must not be dropped or raised instantaneously.

AC Electrical Characteristics

0˚C ≤ TA ≤ +70˚C unless otherwise specified

Parameter

Condition

Instruction Cycle Time (tc)

Crystal/Resonator or External

(Div-by 10)

R/C Oscillator Mode

(Div-by 10)

CKI Clock Duty Cycle (Note 7)

VCC ≥ 4.0V

2.3V ≤ VCC ≤ 4.0V

VCC ≥ 4.0V

2.3V ≤ VCC ≤ 4.0V

fr = Max

Rise Time (Note 7)

fr = 10 MHz Ext Clock

Fall Time (Note 7)

fr = 10 MHz Ext Clock

Inputs

tSETUP

tHOLD

Output Propagation Delay

tPD1, tPD0

SO, SK

All Others

MICROWIRE™ Setup Time (tUWS)

MICROWIRE Hold Time (tUWH)

MICROWIRE Output

VCC ≥ 4.0V

2.3V ≤ VCC ≤ 4.0V

VCC ≥ 4.0V

2.3V ≤ VCC ≤ 4.0V

CL = 100 pF, RL = 2.2 kΩ

VCC ≥ 4.0V

2.3V ≤ VCC ≤ 4.0V

VCC ≥ 4.0V

2.3V ≤ VCC ≤ 4.0V

Propagation Delay (tUPD)

Input Pulse Width

Interrupt Input High Time

Interrupt Input Low Time

Timer Input High Time

Timer Input Low Time

Reset Pulse Width

Min Typ

1

2.5

3

7.5

40

200

500

60

150

20

56

tC

tC

tC

tC

1.0

Max

DC

DC

DC

DC

60

12

8

0.7

1.75

1

2.5

220

Units

µs

µs

µs

µs

%

ns

ns

ns

ns

ns

ns

µs

µs

µs

µs

ns

ns

ns

µs

Note 7: Parameter characterized but not production tested.

5 www.national.com

5 Page

Typical Performance Characteristics (−40˚C ≤ TA ≤ +85˚C) (Continued)

Port D Sink Current

Pin Descriptions

VCC and GND are the power supply pins.

CKI is the clock input. This can come from an external

source, a R/C generated oscillator or a crystal (in conjunc-

tion with CKO). See Oscillator description.

RESET is the master reset input. See Reset description.

PORT I is an 8-bit Hi-Z input port. The 28-pin device does not

have a full complement of Port I pins. The unavailable pins

are not terminated i.e., they are floating. A read operation for

these unterminated pins will return unpredictable values.

The user must ensure that the software takes this into ac-

count by either masking or restricting the accesses to bit

operations. The unterminated Port I pins will draw power

only when addressed.

PORT L is an 8-bit I/O port.

PORT C is a 4-bit I/O port.

Three memory locations are allocated for the L, G and C

ports, one each for data register, configuration register and

the input pins. Reading bits 4–7 of the C-Configuration reg-

ister, data register, and input pins returns undefined data.

There are two registers associated with the L and C ports: a

data register and a configuration register. Therefore, each L

and C I/O bit can be individually configured under software

control as shown below:

Con- Data

Ports L and C Setup

fig.

0 0 Hi-Z Input (TRI-STATE Output)

0 1 Input with Pull-Up (Weak One Output)

1 0 Push-Pull Zero Output

1 1 Push-Pull One Output

On the 28-pin part, it is recommended that all bits of Port C

be configured as outputs.

PORT G is an 8-bit port with 6 I/O pins (G0–G5) and 2 input

pins (G6, G7). All eight G-pins have Schmitt Triggers on the

inputs.

There are two registers associated with the G port: a data

register and a configuration register. Therefore, each G port

bit can be individually configured under software control as

shown below:

DS010802-22

Con- Data

Port G Setup

fig.

0 0 Hi-Z Input (TRI-STATE Output)

0 1 Input with Pull-Up (Weak One Output)

1 0 Push-Pull Zero Output

1 1 Push-Pull One Output

Since G6 and G7 are input only pins, any attempt by the user

to configure them as outputs by writing a one to the configu-

ration register will be disregarded. Reading the G6 and G7

configuration bits will return zeros. The device will be placed

in the HALT mode by writing to the G7 bit in the G-port data

register.

Six pins of Port G have alternate features:

G0 INTR (an external interrupt)

G3 TIO (timer/counter input/output)

G4 SO (MICROWIRE serial data output)

G5 SK (MICROWIRE clock I/O)

G6 SI (MICROWIRE serial data input)

G7 CKO crystal oscillator output (selected by mask option)

or HALT restart input (general purpose input)

Pins G1 and G2 currently do not have any alternate func-

tions.

PORT D is an 8-bit output port that is preset high when

RESET goes low. Care must be exercised with the D2 pin

operation. At RESET, the external loads on this pin must

ensure that the output voltages stay above 0.9 VCC to pre-

vent the chip from entering special modes. Also, keep the

external loading on D2 to less than 1000 pF.

Functional Description

Figure 1 shows the block diagram of the internal architec-

ture. Data paths are illustrated in simplified form to depict

how the various logic elements communicate with each

other in implementing the instruction set of the device.

ALU AND CPU REGISTERS

The ALU can do an 8-bit addition, subtraction, logical or shift

operation in one cycle time.

There are five CPU registers:

A is the 8-bit Accumulator register

PU is the upper 7 bits of the program counter (PC)

PL is the lower 8 bits of the program counter (PC)

11 www.national.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet COPCH881C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| COPCH881C | Microcontrollers | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |