|

|

PDF S5D0127X01 Data sheet ( Hoja de datos )

| Número de pieza | S5D0127X01 | |

| Descripción | Multistandard Video Decoder / Scaler | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de S5D0127X01 (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

S5D0127X01 Data Sheet

MULTISTANDARD VIDEO DECODER/SCALER

The S5D0127X01 converts analog NTSC, PAL or SECAM

video in composite, S-video, or component format to

digitized component video. Output data can be selected for

CCIR 601 or square pixel sample rates in either YCbCr or

RGB formats. The digital video can be scaled down in both

the horizontal and vertical directions. The S5D0127X01

also decodes Intercast, Teletext, Closed Caption, and WSS

data with a built-in bit data slicer. Digitized CVBS data can

be output directly during VBI for external processing.

MULTIMEDIA VIDEO

100 PQFP

FEATURES

• Accepts NTSC-M/N/4.43, PAL-M/N/B/G/H/I/D/K/L and

SECAM formats with auto detection

• 6 analog inputs: 3 S-video, 6 composite, or 1 3-wire

YCbCr component video

• 2-line luma and chroma comb filters including adaptive

luma comb for NTSC

• Programmable luma bandwidth, contrast, brightness,

and edge enhancement

• Programmable chroma bandwidth, hue, and saturation

• High quality horizontal and vertical down scaler

• Intercast, Teletext and Closed Caption decoding with

built-in bit slicer

• Direct output of digitized CVBS during VBI for Intercast

application

• Analog square pixel or CCIR 601 sample rates

• Output in 4:4:4, 4:2:2, or 4:1:1 YCbCr component, or

24-bit or 16-bit RGB formats with dithering

• YCbCr 4:2:2 output can be 8 or 16 bits wide with

embedded timing reference code support for 8-bit mode

• Simultaneous scaled and non-scaled digital output ports

outputs for 8-bit mode.

• Direct access to scaler via bi-directional digital port.

• Programmable Gamma correction table

• Programmable timing signals

• Industry standard IIC interface

ORDERING INFORMATION

Device

Package

S5D0127X01-

Q0R0

100 PQFP

Temperature Range

-20°~+70°C

• Digital Video

• Video Capture/Editing

RELATED PRODUCTS

• S5D0123X01

ENCODER

MULTISTANDARD

VIDEO

APPLICATIONS

• Multimedia

ELECTRONICS

Modified on May/04/2000

PAGE 1 OF 96

1 page

S5D0127X01 Data Sheet

MULTIMEDIA VIDEO

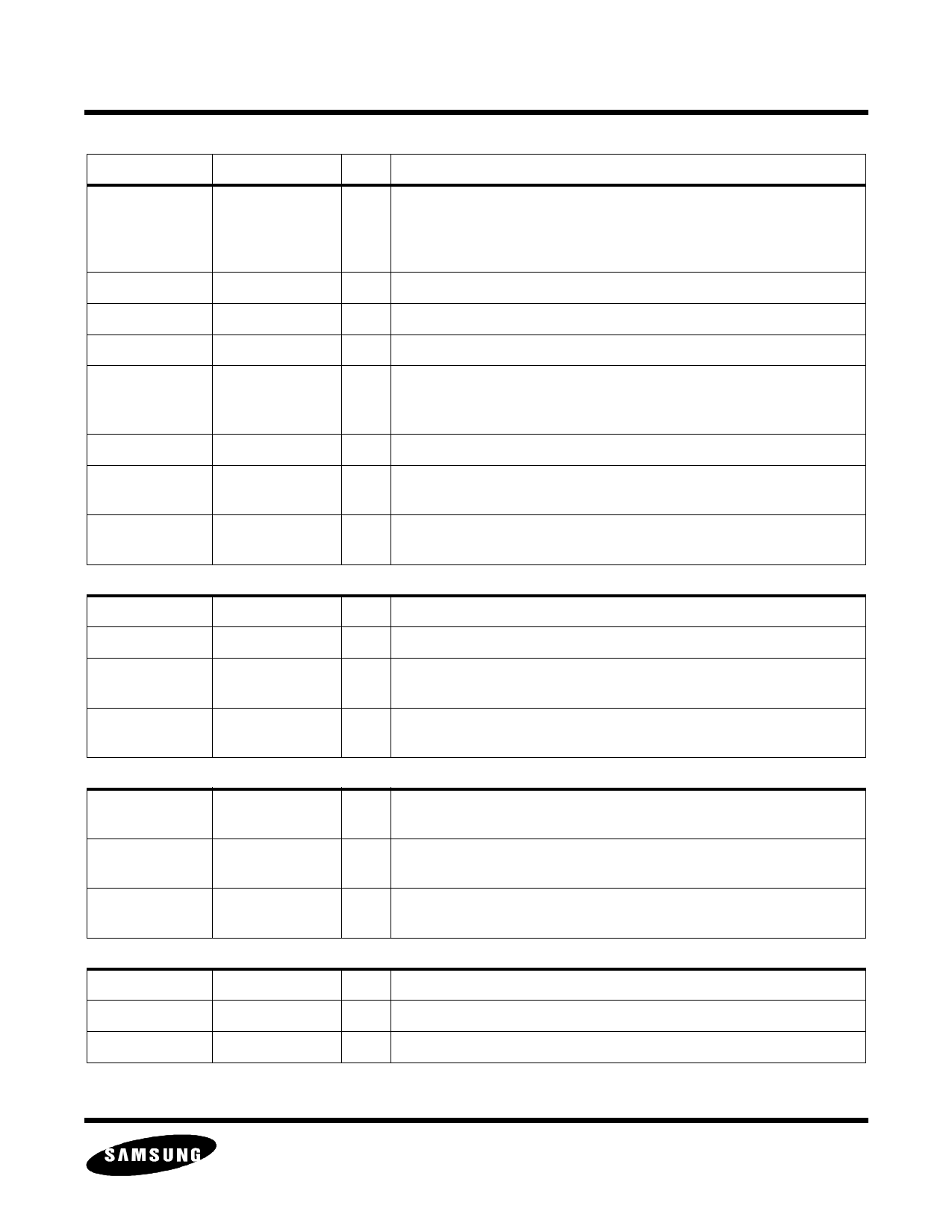

PIN DESCRIPTION (Continued)

Pin Name

Pin #

Type

Description

EVAV(OENC1) 4

I/O Valid line flag. Polarity is programmable. Active when output video

line is valid. During reset, the pin is an input and the logic state of

this pin is latched into the OENC[1]register bit. Use a 10 kΩ resistor

for pull-up or pull-down.

ODD

22

O Odd field flag. Polarity is programmable. Active for fields 1 and 3.

PID 17

O PAL ID flag. High for phase alternating line.

OEN

15

I Digital video data, timing and clock output 3-state control.

CK 18

I/O Pixel clock. In normal decoding mode, this is an output. When the

EXV port is used as an input, this can be programmed as an input

pixel clock.

CK2

21

O Pixel output clock (rate is one half of CK) aligned to HAV signal.

CCDAT

73

O Sliced VBI data output. Data can be from Closed Caption, Teletext,

Intercast, or WSS type encoded data.

CCEN

74

O When high, this pin indicates that valid VBI data is being clocked out

at the CCDAT pin or at the digital video output.

MULTI-PURPOSE I/O PORTS AND TEST ENABLE

PORTA

58

I/O Multi-purpose I/O port.

SCH(PORTB) 24

I/O Multi-purpose I/O port.

TESTEN

57

I When tied to VDD, the chip is put into the test mode. For normal use,

this pin should be connected to VSS.

TEST

96

I When tied to VDD, the chip is put into the test mode. For normal use,

this pin should be connected to VSS.

REFERENCE AND COMPENSATION

VRT

77

I/O

ADC VRT compensation (requires an external 0.1 µF capacitor

connected to VSS).

VRB

78

I/O ADC VRB compensation (requires an external 0.1 µF capacitor

connected to VSS).

COMP2

97

I/O Internal 1.3 V reference (requires an external 0.1 µF capacitor

connected to VSS).

HOST INTERFACE

SCLK

75

I Serial clock for IIC host interface.

SDAT

72

I/O Serial data for IIC host interface.

AEX0 - AEX1 69 - 70

I Device ID selection for IIC host interface.

ELECTRONICS

Modified on May/04/2000

PAGE 5 OF 96

5 Page

S5D0127X01 Data Sheet

MULTIMEDIA VIDEO

When in digital input mode, all programmable timing registers (such as HAVB,HAVE, HS2B etc.) are still functional.

If HS1 and VS are programmed as inputs, the associated output timing controls such as HS1B,E will have no

effect. An example of horizontal timing for digital input is shown in Figure 4.

HS1

Programmable, when an

output - Any input phase

is acceptable

This HS1 location can also come

From a 656 SAV code

Constant to internal counter reference

EXV[7:0]

80 10 80 10 80 10 U0 Y0 V0 Y1 U2 Y2 V2 Y3 U4 Y4 V4 Y5 U6 Y6 V6 Y7 Ux Yx Vx Yx Ux Yx Vx Yx Vx

Data group delay through chip --

Y[7:0]

Y output for OFMT=2 is

shown, any 8 or 16 bit

output format is allowed.

80 10 80 10 80 10 U0 Y0 V0 Y1 U2 Y2 V2 Y3 U4 Y4 V4 Y5 U6 Y6 V6 Y7 Ux Yx Vx Yx Ux

Fully programmable HAVB location

based on internal counter

HAV -- fully programmable,

Defines location of first, last pixel

and defines Cb,Y,Cr data location

Fully programmable

HAVE location

HAV

CK

CK2

CK can be input or output

The CK2 output clock phasing

is aligned to the HAV leading

edge

Figure 4. Horizontal Timing for EXV Port as Digital Input

1.1.5. Additional Information for Analog Component Video Input

For the S5D0127X01 to correctly set the V component phase in analog component video input mode, PID (pin 17)

and PORTA (pin 58) need to be connected together. PORTA has to be configured as input (DIRA = 0) and

connected to the internal CBG signal (DATAA[2:0] = 3).

It is also recommended that external clamp circuit be used for Cb and Cr inputs (before the coupling caps) and the

internal chroma clamp be disabled (COFFENB = 1) due to slight Cb/Cr leakage.

ELECTRONICS

Modified on May/04/2000

PAGE 11 OF 96

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet S5D0127X01.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S5D0127X01 | MULTISTANDARD VIDEO DECODER/SCALER | Samsung semiconductor |

| S5D0127X01 | Multistandard Video Decoder / Scaler | Samsung semiconductor |

| S5D0127X01-Q0R0 | MULTISTANDARD VIDEO DECODER/SCALER | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |