|

|

PDF BR24L64FJ-W Data sheet ( Hoja de datos )

| Número de pieza | BR24L64FJ-W | |

| Descripción | 8k x 8 bit electrically erasable PROM | |

| Fabricantes | ROHM Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de BR24L64FJ-W (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

Memory ICs

BR24L64-W / BR24L64F-W / BE24L64FJ-W

8k×8 bit electrically erasable PROM

BR24L64-W / BR24L64F-W / BR24L64FJ-W

The BR24L64-W series is 2-wire (I2C BUS type) serial EEPROMs which are electrically programmable.

∗ I2C BUS is a registered trademark of Philips.

zApplications

General purpose

zFeatures

1) 8k registers × 8 bits serial architecture.

2) Single power supply (1.8V to 5.5V).

3) Two wire serial interface.

4) Automatic erase.

5) 32 byte page write mode.

6) Low power consumption.

Write (5V) : 1.5mA (Typ.)

Read (5V) : 0.2mA (Typ.)

Standby (5V) : 0.1µA (Typ.)

7) DATA security

Write protect feature (WP pin) .

Inhibit to WRITE at low VCC.

8) Small package - - - DIP8 / SOP8 pin

9) High reliability EEPROM with Double-Cell structure

10) High reliability fine pattern CMOS technology.

11) Endurance : 1,000,000 erase / write cycles

12) Data retention : 40 years

13) Filtered inputs in SCL•SDA for noise suppression.

14) Initial data FFh in all address.

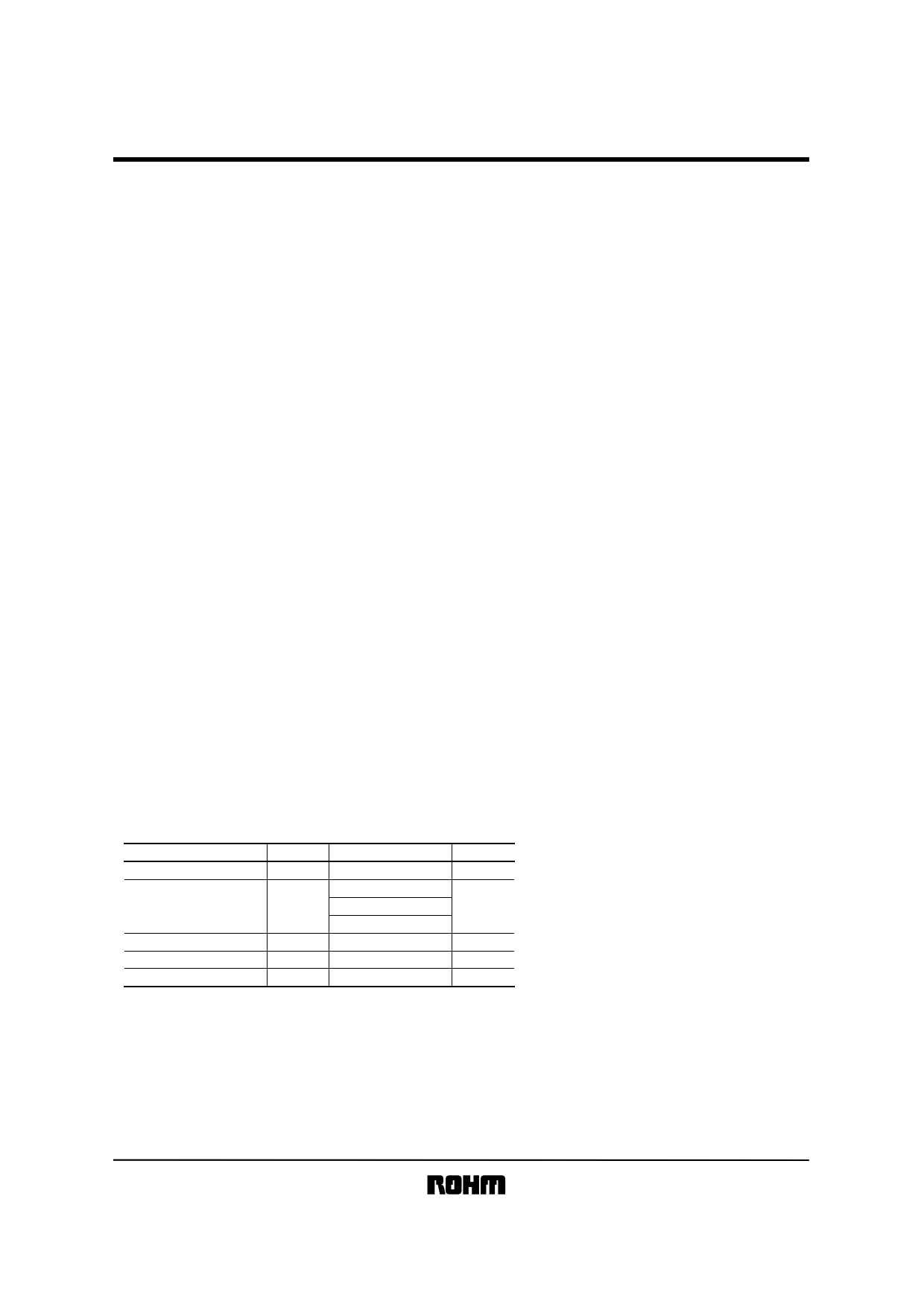

zAbsolute maximum ratings (Ta=25°C)

Parameter

Supply voltage

Symbol

VCC

Power dissipation

Pd

Storage temperature

Tstg

Operating temperature

Topr

Terminal voltage

−

∗1 Degradation is done at 8.0mW/°C for operation above 25°C.

∗2 Degradation is done at 4.5mW/°C for operation above 25°C.

Limits

−0.3~+6.5

800(DIP8) ∗1

450(SOP8) ∗2

450(SSOP-J8) ∗2

−65~+125

−40~+85

−0.3~VCC+0.3

Unit

V

mW

°C

°C

V

1/25

1 page

Memory ICs

BR24L64-W / BR24L64F-W / BE24L64FJ-W

zAC operating characteristics (Unless otherwise specified Ta=−40 to 85°C, VCC=1.8 to 5.5V)

Parameter

Clock frequency

Data clock "HIGH" period

Data clock "LOW" period

SDA and SCL rise time ∗1

SDA and SCL fall time ∗1

Start condition hold time

Start condition setup time

Input data hold time

Input data setup time

Output data delay time

Output data hold time

Stop condition setup time

Bus free time

Write cycle time

Noise spike width (SDA and SCL)

WP hold time

WP setup time

WP high period

∗1 Not 100% tested.

Symbol

fSCL

tHIGH

tLOW

tR

tF

tHD:STA

tSU:STA

tHD:DAT

tSU:DAT

tPD

tDH

tSU:STO

tBUF

tWR

tl

tHD:WP

tSU:WP

tHIGH:WP

Fast-mode

2.5V ≤ Vcc ≤ 5.5V

Min. Typ. Max.

− − 400

0.6 −

−

1.2 −

−

− − 0.3

− − 0.3

0.6 −

−

0.6 −

−

0−−

100 −

−

0.1 − 0.9

0.1 −

−

0.6 −

−

1.2 −

−

−−5

− − 0.1

0−−

0.1 −

−

1.0 −

−

Standard-mode

1.8V ≤ Vcc ≤ 5.5V

Min. Typ. Max.

− − 100

4.0 −

−

4.7 −

−

− − 1.0

− − 0.3

4.0 −

−

4.7 −

−

0−−

250 −

−

0.2 − 3.5

0.2 −

−

4.7 −

−

4.7 −

−

−−5

− − 0.1

0−−

0.1 −

−

1.0 −

−

Unit

kHz

µs

µs

µs

µs

µs

µs

ns

ns

µs

µs

µs

µs

ms

µs

ns

µs

µs

5/25

5 Page

Memory ICs

BR24L64-W / BR24L64F-W / BE24L64FJ-W

zCurrent read

S

TR

AE

R SLAVE A

T

ADDRESS

D

DATA

S

T

O

P

SDA

LINE

1 0 1 0 A2 A1 A0

D7

D0

RA

/C

WK

A

C

K

Fig.10 CURRENT READ CYCLE TIMING

• In case that the previous operation is Random or Current Read (which includes Sequential Read respectively), the

internal address counter is increased by one from the last accessed address (n).

Thus Current Read outputs the data of the next word address (n+1).

If the last command is Byte or Page Write, the internal address counter stays at the last address (n).

Thus Current Read outputs the data of the word address (n).

• If an Acknowledge is detected, and no STOP condition is generated by the master (µ-COM), the device will continue

to transmit the data. [ It can transmit all data (64kbit 8,192word) ]

• If an Acknowledge is not detected, the device will terminate further data transmissions and await a STOP condition

before returning to the standby mode.

Note) If an Acknowledge is detected with “Low” level, not “High” level, command will become Sequential Read.

So the device transmits the next data, Read is not terminated. In the case of terminating Read, input

Acknowledge with “High” always, then input stop condition.

zRandom read

S

T

A

R SLAVE

T ADDRESS

W

R

I

T

E

1st WORD

ADDRESS(n)

SDA

LINE

1 0 1 0 A2A1A0

∗

∗

∗

WA

12

S

TR

AE

2nd WORD R SLAVE A

ADDRESS(n) T ADDRESS D

DATA(n)

S

T

O

P

WA

0

1 0 1 0 A2A1A0

D7

D0

RA A A RA A

/C C C /C C

WK K K WK K

Fig.11 RANDOM READ CYCLE TIMING

∗Don't care

• Random read operation allows the master to access any memory location indicated word address.

• If an Acknowledge is detected, and no STOP condition is generated by the master (µ-COM), the device will continue to

transmit the data. [ It can transmit all data (64kbit 8,192word) ]

• If an Acknowledge is not detected, the device will terminate further data transmissions and await a STOP condition

before returning to the standby mode.

Note) If an Acknowledge is detected with “Low” level, not “High” level, command will become Sequential Read.

So the device transmits the next data, Read is not terminated. In the case of terminating Read, input

Acknowledge with “High” always, then input stop condition.

11/25

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet BR24L64FJ-W.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| BR24L64FJ-W | 8k x 8 bit electrically erasable PROM | ROHM Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |