|

|

PDF SY100EP195V Data sheet ( Hoja de datos )

| Número de pieza | SY100EP195V | |

| Descripción | 3.3V/5V 2.5GHz PROGRAMMABLE DELAY | |

| Fabricantes | Micrel Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SY100EP195V (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

Micrel, Inc.

3.3V/5V 2.5GHz

PROGRAMMABLE DELAY

ECL Pro®

ESCYL100PErPo1®95V

SY100EP195V

FEATURES

■ Pin-for-pin, plug-in compatible to the ON

Semiconductor MC100EP195

■ Maximum frequency > 2.5GHz

■ Programmable range: 2.2ns to 12.2ns

■ 10ps increments

■ PECL mode operating range: VCC = 3.0V to 5.5V

with VEE = 0V

■ NECL mode operating range: VCC = 0V

with VEE = –3.0V to –5.5V

■ Open input default state

■ Safety clamp on inputs

■ A logic high on the /EN pin will force Q to logic low

■ D[0:10] can accept either ECL, CMOS, or TTL inputs

■ VBB output reference voltage

■ Available in a 32-pin TQFP package

ECL Pro®

DESCRIPTION

The SY100EP195V is a programmable delay line, varying

the time a logic signal takes to traverse from IN to Q. This

delay can vary from about 2.2ns to about 12.2ns. The input

can be PECL, LVPECL, NECL, or LVNECL.

The delay varies in discrete steps based on a control

word presented to SY100EP195V. The 10-bit width of this

latched control register allows for delay increments of

approximately 10ps.

An eleventh control bit allows the cascading of multiple

SY100EP195V devices, for a wider delay range. Each

additional SY100EP195V effectively doubles the delay range

available.

For maximum flexibility, the control register interface

accepts CMOS or TTL level signals, as well as the input

level at the IN± pins.

All support documentation can be found on Micrel’s web

site at: www.micrel.com.

APPLICATIONS

■ Clock de-skewing

■ Timing adjustment

■ Aperture centering

CROSS REFERENCE TABLE

Micrel Semiconductor

SY100EP195VTI

SY100EP195VTITR

ON Semiconductor

MC100EP195FA

MC100EP195FAR2

TYPICAL APPLICATIONS CIRCUIT

Data Signal

of Unknown Phase

CLOCK+

CLOCK–

SY100EP195V

IN Q

/IN /Q

D[9:0]

CONTROL

LOGIC

D Q+

Flip-Flop

CK Q–

ECL Pro is a registered trademark of Micrel, Inc.

M9999-120505

[email protected] or (408) 955-1690

TYPICAL PERFORMANCE

12000

Delay vs. Tap

10000

8000

6000

4000

2000

0

0 200 400 600 800 1000 1200

TAP (DIGITAL WORD)

Rev.: D Amendment: /0

1 Issue Date: December 2005

1 page

Micrel, Inc.

ECL Pro®

SY100EP195V

LVPECL DC ELECTRICAL CHARACTERISTICS (100kEP)

VCC = 3.3V, VEE = 0V; TA = –40°C to +85°C.(5, 6)

Symbol

Parameter

Condition

VOH Output HIGH Voltage

VOL Output LOW Voltage

VIH Input HIGH Voltage

PECL

CMOS

TTL

Figures 2, 3, 6

Figures 2, 3, 6

Figures 1, 4

VIL Input LOW Voltage

PECL

CMOS

TTL

Figures 1, 4

VBB

VCF

VEF

VIHCMR

Output Voltage Reference

Input Select Voltage

Mode Connection

Input HIGH Voltage Common

Mode Range(7)

Figure 5

IIH Input HIGH Current

IIL Input LOW Current

IN

/IN

Min

2155

1355

Typ

2280

1480

Max

2405

1605

Units

mV

mV

2075

1815

2000

2420

mV

mV

mV

1355

1775

1610

1900

2.0

1875

1720

2000

1675

1485

800

1975

1825

2100

3.3

mV

mV

mV

mV

mV

mV

V

150 µA

0.5

–150

µA

µA

Notes:

5. Device is guaranteed to meet the DC specifications, shown in the table below, after thermal equilibrium has been established. The device is tested in

a socket such that transverse airflow of ≥ 500lfpm is maintained.

6. Input and output parameters vary 1:1 with VCC. VEE can vary +0.3V to –2.2V.

7. VIHCMR maximum varies 1:1 with VCC. The VIHCMR range is referenced to the most positive side of the differential input signal.

M9999-120505

[email protected] or (408) 955-1690

5

5 Page

Micrel, Inc.

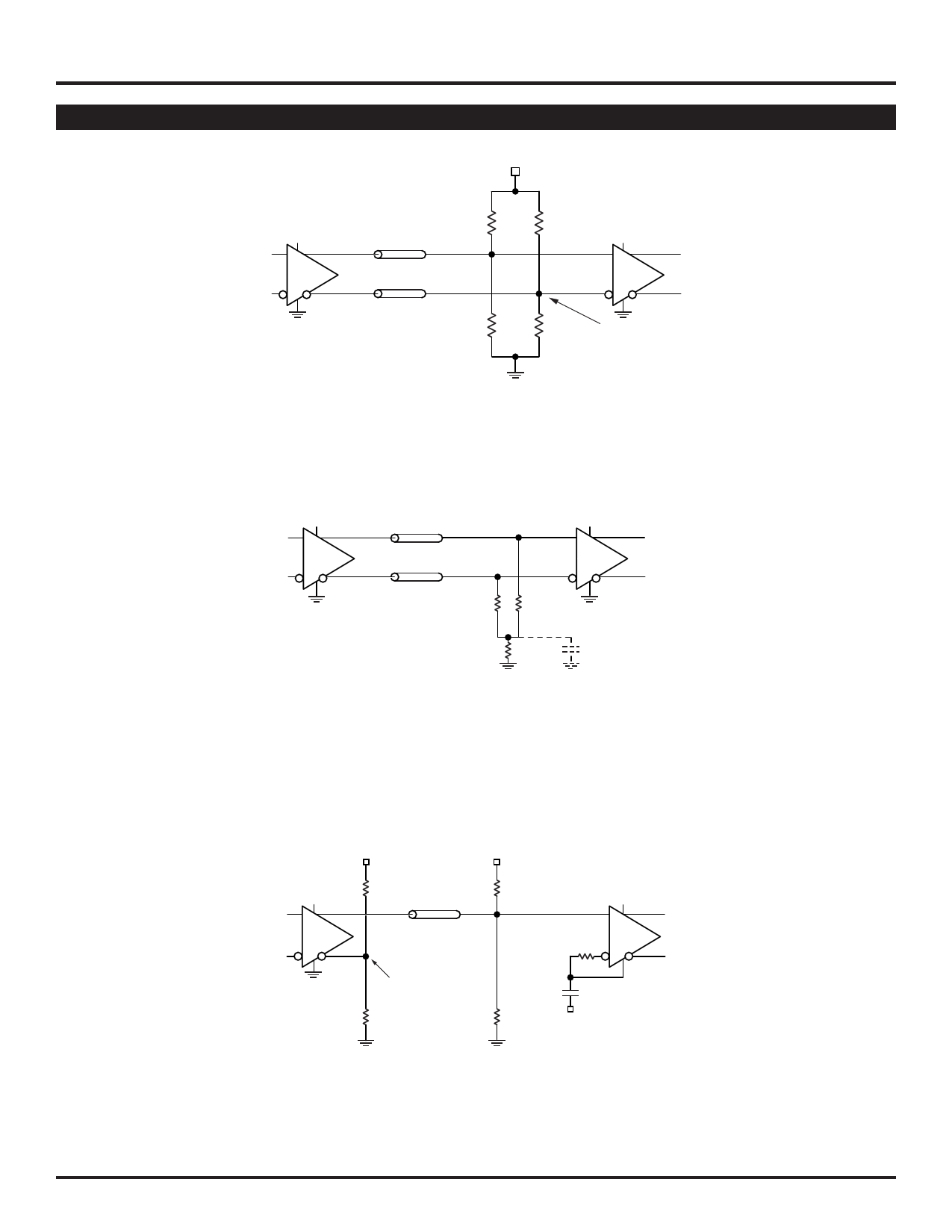

TERMINATING PECL

+3.3V

+3.3V

R1

ZO = 50Ω 130Ω

ZO = 50Ω

R2

82Ω

R1

130Ω +3.3V

R2

82Ω Vt = VCC –2V

ECL Pro®

SY100EP195V

Figure 6a. Parallel Termination—Thevenin Equivalent

Note:

1. For +5.0V systems: R1 = 82Ω, R2 = 130Ω.

+3.3V

Z = 50Ω

Z = 50Ω

+3.3V

“Source”

50Ω

50Ω

50Ω

“Destination”

Rb

C1 (optional)

0.01µF

Figure 6b. Three-Resistor “Y-Termination”

Notes:

1. Power-saving alternative to Thevenin termination.

2. Place termination resistors as close to destination inputs as possible.

3. Rb resistor sets the DC bias voltage, equal to Vt. For +3.3V systems Rb = 46Ω to 50Ω. For +5V systems, Rb = 110Ω.

+3.3V

+3.3V

+3.3V

Q

R1

130Ω

ZO = 50Ω

/Q

Vt = VCC –2V

R2

82Ω

R1

130Ω

+3.3V

50Ω

VBB

0.01µF

R2

82Ω

+3.3V

Figure 6c. Terminating Unused I/O

Notes:

1. Unused output (/Q) must be terminated to balance the output.

2. Micrel's differential I/O logic devices include a VBB reference pin .

3. Connect unused input through 50Ω to VBB. Bypass with a 0.01µF capacitor to VCC, not GND, as PECL is referenced to VCC.

M9999-120505

[email protected] or (408) 955-1690

11

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet SY100EP195V.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SY100EP195V | 3.3V/5V 2.5GHz PROGRAMMABLE DELAY | Micrel Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |