|

|

PDF MTV312M64 Data sheet ( Hoja de datos )

| Número de pieza | MTV312M64 | |

| Descripción | 8051 Embedded Monitor Controller Flash Type with ISP | |

| Fabricantes | Myson | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MTV312M64 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

MYSON

TECHNOLOGY

MTV312M64

(Rev 0.95)

8051 Embedded Monitor Controller

Flash Type with ISP

FEATURES

• 8051 core, 12MHz operating frequency with double CPU clock option.

• 0.35uM process; 5V/3.3V power supply and I/O; 3.3V core operating.

• 1024-byte RAM; 64K-byte program Flash-ROM support In System Programming (ISP).

• Maximum 14 channels of PWM DAC.

• Maximum 31 I/O pins.

• SYNC processor for composite separation/insertion, H/V polarity/frequency check and polarity adjustment.

• Built-in low power reset circuit.

• Built-in self-test pattern generator with four free-running timings.

• Compliant with VESA DDC1/2B/2Bi/2B+ standard.

• Dual slave IIC addresses; H/W auto transfer DDC1/DDC2x data.

• Single master IIC interface for internal device communication.

• Maximum 4-channel 6-bit ADC.

• Watchdog timer with programmable interval.

• 40-pin DIP, 42-pin SDIP or 44-pin PLCC package.

GENERAL DESCRIPTIONS

The MTV312M micro-controller is an 8051 CPU core embedded device especially tailored to CRT/LCD

Monitor applications. It includes an 8051 CPU core, 1024-byte SRAM, 14 built-in PWM DACs, VESA DDC

interface, 4-channel A/D converter, and a 64K-byte internal program Flash-ROM.

BLOCK DIAGRAM

P1.0-7

P3.0-2

P3.4-5

P0.0-7

P2.0-3

8051

CORE

RD

WR

ALE

INT1

RST

X1

X2

P6.0-7

P5.0-6

P4.0-2

AUX

I/O

P0.0-7

P2.0-3

RD

WR

ALE

INT1

XFR

AD0-3 ADC

PWM DAC

DA0-13

AUXRAM &

DDCRAM

H/VSYNC

CONTROL

HSYNC

VSYNC

HBLANK

VBLANK

DDC & IIC

INTERFACE

ISCL

ISDA

HSCL

HSDA

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification without

notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

Revision 0.95

-1-

2001/07/03

1 page

MYSON

TECHNOLOGY

MTV312M64

(Rev 0.95)

FUNCTIONAL DESCRIPTIONS

1. 8051 CPU Core

The CPU core of MTV312M is compatible with the industry standard 8051, which includes 256 bytes RAM,

Special Function Registers (SFR), two timers, five interrupt sources and serial interface. The CPU core

fetches its program code from the 64K bytes Flash in MTV312M. It uses Port0 and Port2 to access the

“external special function register” (XFR) and external auxiliary RAM (AUXRAM).

The CPU core can run at double rate when FclkE is set. Once the bit is set, the CPU runs as if a 24MHz

X’tal is applied on MTV312M, but the peripherals (IIC, DDC, H/V processor) still run at the original frequency.

Note: All registers listed in this document reside in 8051’s external RAM area (XFR). For internal RAM

memory map please refer to 8051 spec.

2. Memory Allocation

2.1 Internal Special Function Registers (SFR)

The SFR is a group of registers that are the same as standard 8051.

2.2 Internal RAM

There is a total of 256 bytes internal RAM in MTV312M, the same as standard 8052.

2.3 External Special Function Registers (XFR)

The XFR is a group of registers allocated in the 8051 external RAM area F00h - FFFh. These registers are

used for special functions. Programs can use "MOVX" instruction to access these registers.

2.4 Auxiliary RAM (AUXRAM)

There is a total of 512 bytes auxiliary RAM allocated in the 8051 external RAM area 800h - 9FFh. Programs

can use "MOVX" instruction to access the AUXRAM.

2.5 Dual Port RAM (DDCRAM)

There are 256 bytes Dual Port RAM allocated in the 8051 external RAM area E00h - EFFh. Program can

use "MOVX" instruction to access the RAM. The external DDC1/2 Host can access the RAM as if a 24LC02

EEPROM is connected on the interface.

FFh Internal RAM

SFR

Accessible by

indirect

addressing only

(Using

MOV A,@Ri

instruction)

80h

7Fh Internal RAM

Accessible by

direct addressing

Accessible by

direct and indirect

addressing

00h

FFFh

XFR

Accessible by

indirect external

RAM addressing

(Using MOVX

instruction)

F00h

EFFh DDCRAM

Accessible by

indirect external

RAM addressing

(Using MOVX

instruction)

E00h

9FFh

AUXRAM

Accessible by

indirect external

RAM addressing

(Using MOVX

instruction

800h

Revision 0.95

-5-

2001/07/03

5 Page

MYSON

TECHNOLOGY

MTV312M64

(Rev 0.95)

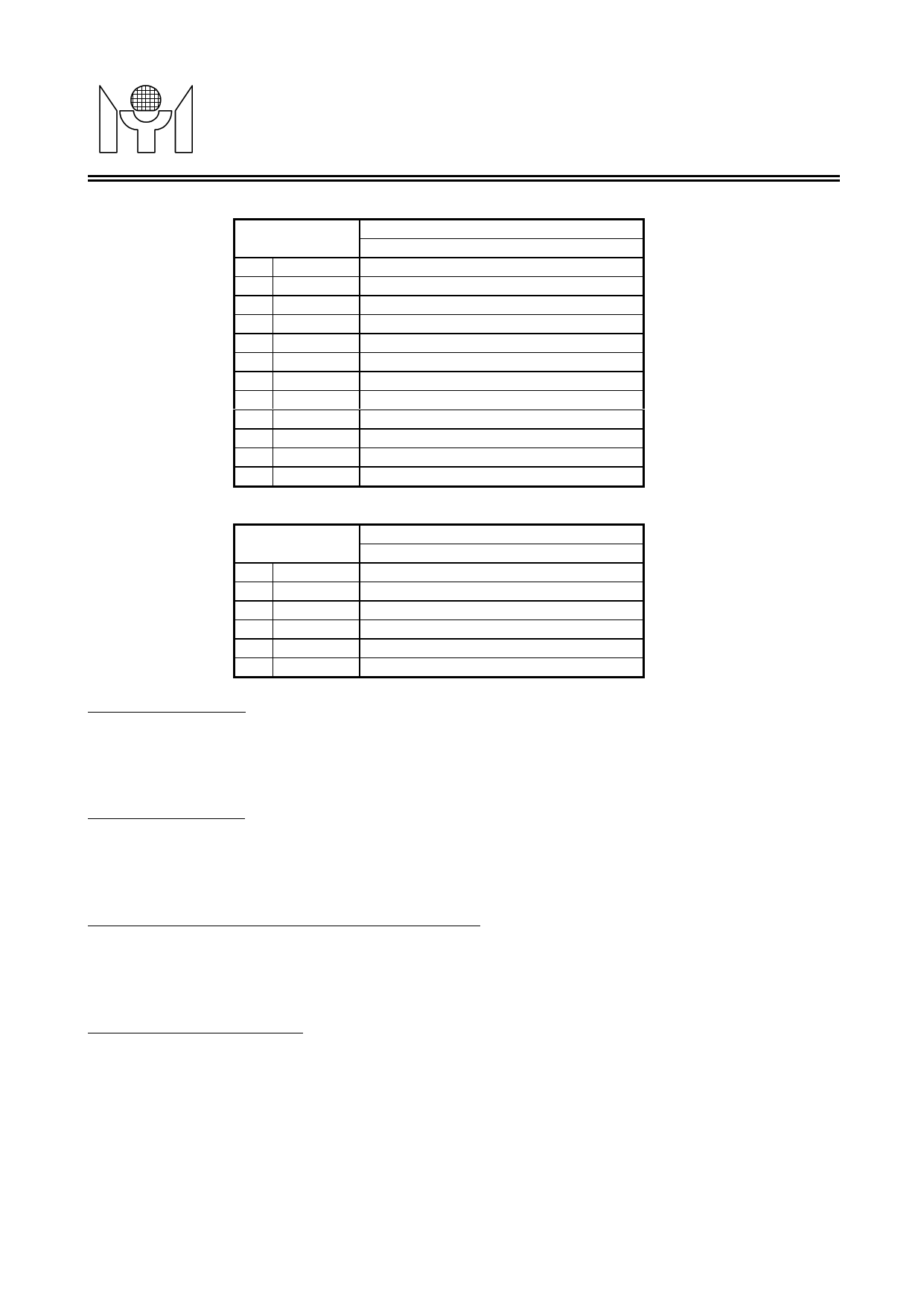

6.2.1 H-Freq Table

H-Freq(KHZ)

1 31.5

2 37.5

3 43.3

4 46.9

5 53.7

6 60.0

7 68.7

8 75.0

9 80.0

10 85.9

11 93.8

12 106.3

Output Value (14 bits)

12MHz OSC (hex / dec)

0FDEh / 4062

0D54h / 3412

0B8Bh / 2955

0AA8h / 2728

094Fh / 2383

0854h / 2132

0746h / 1862

06AAh / 1706

063Fh / 1599

05D1h / 1489

0554h / 1364

04B3h / 1203

6.2.2 V-Freq Table

V-Freq(Hz)

1 56

2 60

3 70

4 72

5 75

6 85

Output value (12bits)

12MHz OSC (hex / dec)

45Ch / 1116

411h / 1041

37Ch / 892

364h / 868

341h / 833

2DFh / 735

6.3 H/V Present Check

The Hpresent function checks the input HSYNC pulse, Hpre flag is set when HSYNC is over 10KHz or

cleared when HSYNC is under 10Hz. The Vpresent function checks the input VSYNC pulse, the Vpre flag is

set when VSYNC is over 40Hz or cleared when VSYNC is under 10Hz. The HPRchg interrupt is set when

the Hpre value changes. The VPRchg interrupt is set when the Vpre/CVpre value change.

6.4 H/V Polarity Detect

The polarity functions detect the input HSYNC/VSYNC high and low pulse duty cycle. If the high pulse

duration is longer than that of the low pulse, the negative polarity is asserted; otherwise, positive polarity is

asserted. The HPLchg interrupt is set when the Hpol value changes. The VPLchg interrupt is set when the

Vpol value changes.

6.5 Output HBLANK/VBLANK Control and Polarity Adjust

The HBLANK is the mux output of HSYNC, composite Hpulse and self-test horizontal pattern. The VBLANK

is the mux output of VSYNC, CVSYNC and self-test vertical pattern. The mux selection and output polarity

are S/W controllable. The VBLANK output is cut off when VSYNC frequency is over 250Hz. The

HBLANK/VBLANK shares the output pin with P4.1/ P4.0.

6.6 Self Test Pattern Generator

For testing purposes, this generator can generate 4 display patterns, which are positive cross-hatch,

negative cross-hatch, full white, and full black (shown as figures below). The HBLANK output frequency of

the pattern can be chosen to 95.2KHz, 63.5KHz, 47.6KHz and 31.75KHz. The VBLANK output frequency of

the pattern is 72Hz or 60Hz. It is originally designed to support monitor manufacturer to do burn-in test, or

offer end-user a reference to check the monitor. The output STOUT of the generator shares the output pin

with P4.2.

Revision 0.95

- 11 -

2001/07/03

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet MTV312M64.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MTV312M64 | 8051 Embedded Monitor Controller Flash Type with ISP | Myson |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |