|

|

PDF VT6304 Data sheet ( Hoja de datos )

| Número de pieza | VT6304 | |

| Descripción | 1394.A 4 PORT PHYSICAL LAYER CHIP | |

| Fabricantes | VIA | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de VT6304 (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

VIA Technologies, Inc.

Preliminary VT6304

VT6304

1394.A 4 PORT PHYSICAL LAYER CHIP

DATA SHEET

(Preliminary)

DATE :

June 1, 1999

VIA TECHNOLOGIES, INC.

1

1 page

VIA Technologies, Inc.

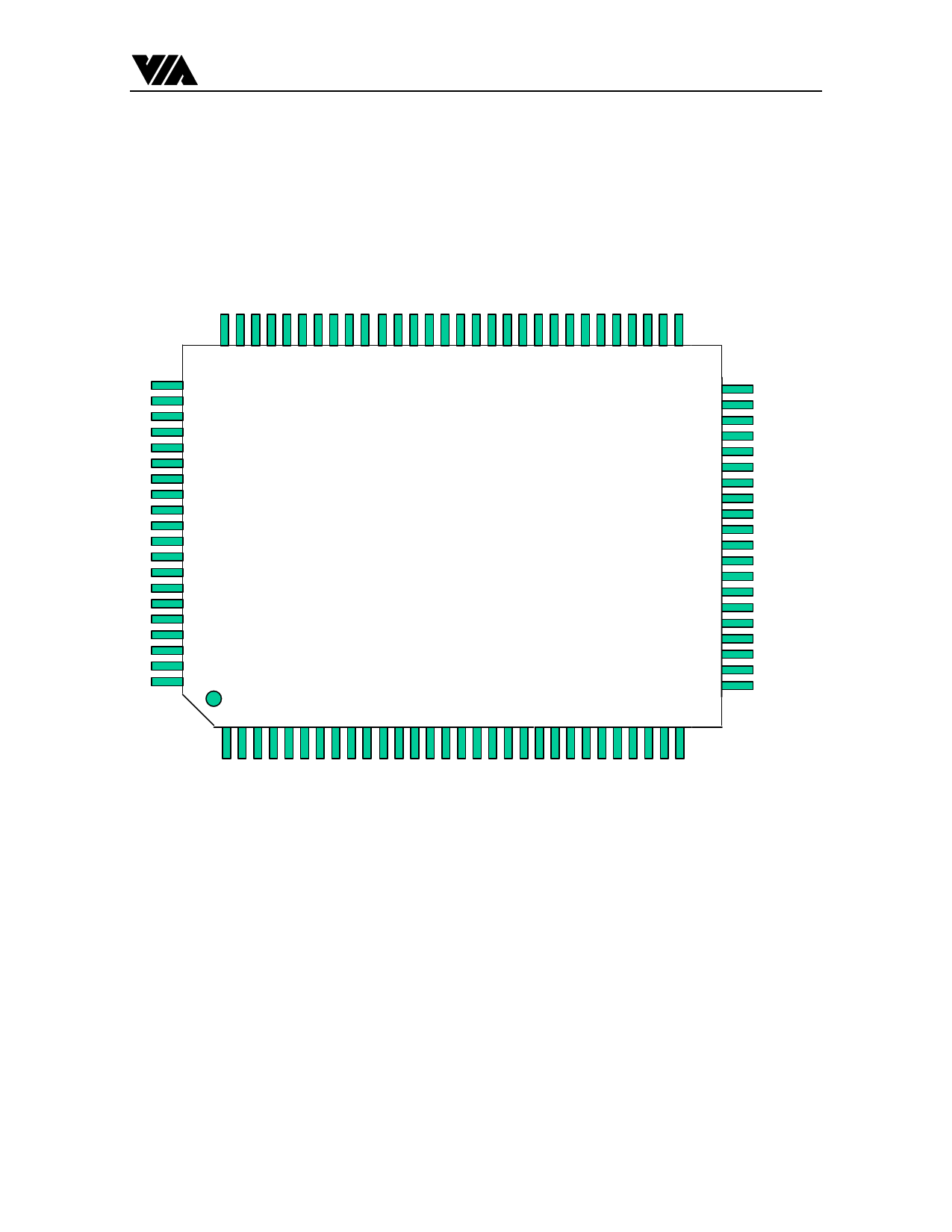

Pin Diagram

Preliminary VT6304

GNDD5

LINKON

LPS

CMC

VDDDC2

GNDDC2

XCPS

VDDARX0

GNDARX0

XTPB0M

XTPB0P

XTPA0M

XTPA0P

XTPBIAS0

VDDATX0

GNDATX0

GNDATX1

VDDATX1

VDDARX1

GNDARX1

80 79 78 77 76 75 74 73 72 7170 69 68 6766 65 64 63 62 6160 59 58 57 5655 54 53 52 51

81

82

83

84

85

86

87

88

89

VT6304

90

91

92

93 01/07/99 updated

94

95

96

97

98

99

100

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 1718 19 20 21 22 2324 25 26 27 28 29 30

CNA

RESET_

ONCT

TSI

GNDD1

VDDD1

PC0

PC1

PC2

TSO

VDDDC1

GNDDC1

XO

XI

XREXT

GNDAREXT

GNDARX3

VDDARX3

VDDATX3

GNDATX4

5

5 Page

VIA Technologies, Inc.

Preliminary VT6304

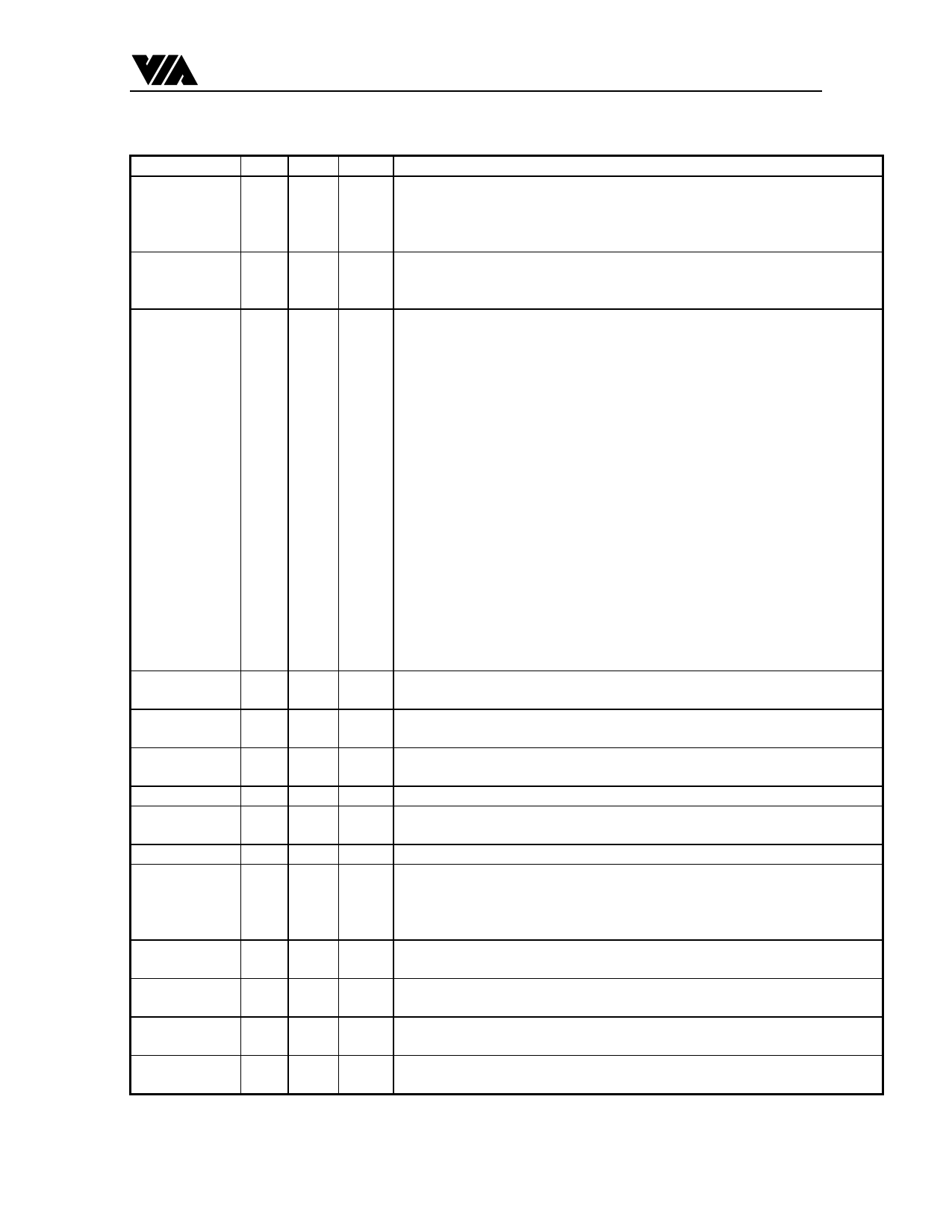

Delay

Link_active

4

1

Contender

1

Pwr_class

3

Jitter

Resume_int

ISBR

Loop

Pwr_fail

Timeout

Port_event

3

1

1

1

1

1

1

Enab_accel

Enab_multi

Page_select

Port_select

1

1

3

4

R0

Worse case repeater delay, expressed as 144+(delay*20)ns.

rw 1

Link enabled. Default value of one subsequent to a power reset. Otherwise

cleared or set by software to control the value of the L bit transmitted in the

self-ID packet. The transmitted L bit shall be the logical AND of this bit and

the LPS signal.

rw Pin Contender. Cleared or set by software to control the value of the C bit

C/LKO transmitted in the self-ID packet.

N

rw Pin Power class. Controls the value of the pwr field transmitted in the self-ID

PC0- packet.

PC2

000 - Node does not need power and does not repeat power

001 - Node is self-powered and provides a minimum of 15 W to the

bus

010 - Node is self-powered and provides a minimum of 30 W to the

bus.

011 - Node is self-powered and provides a minimum of 45 W to the

bus

100 - Node may be powered from the bus and is using up to 1 W.

101 - Node is powered from the bus and is using up to 1 W. An

additional 2 W is needed to enable the link and higher layers.

110 - Node is powered form the bus and is using up to 1 W. An

additional 5 W is needed to enable the link and higher layers.

111 - Node is powered from the bus and is using up to 1 W. An

additional 9 W is needed to enable the link and higher layers.

R0

The difference between the fastest and slowest repeater data delay, expressed

as (jitter+1)*20ns

Rw 0

Resume interrupt enable. When set to one, the PHY shall set port_event to

one if resume operations commence for any port.

rw 0

Initiate short (arbitrated) bus reset. A write of one to this bit instructs the

PHY to arbitrate and issue a short bus reset. This bit is self-clearing.

rw 0

Loop detect. A write of one to this bit clears it to zero.

rw 0

Cable power failure detect. Set to one when the PS bit changes from one to

zero. A write of one to this bit clears it to zero.

rw 0

Arbitration state machine timeout. A write of one to this bit clears it to zero.

rw 0

Port event detect. The PHY sets this bit to one if any of connected, Bias,

Disabled or Fault change for a port whose Int_enable bit is one. The PHY

also sets this bit to one if resume operations commence for any port and

Resume_int is one. A write of one to this bit clears it to zero.

rw 0

Enable arbitration acceleration. When set to one, the PHY shall use the

enhancements specification in P1394A.

rw 0

Enable multi-speed packet concatenation. When set to one, the Link shall

signal the speed of all packets to the PHY.

rw 000 Selects which of eight possible PHY register pages are accessible through

the window at PHY register address 1000b through 1111b, inclusive.

rw 0000 If the page selected by Page_select presents per port information, this field

selects which port’s registers are accessible through the window at PHY

11

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet VT6304.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| VT6304 | 1394.A 4 PORT PHYSICAL LAYER CHIP | VIA |

| VT6305 | PCI 1394 Host Controller | ETC |

| VT6306 | PCI 1394a Integrated Host Controller | VIA |

| VT6307 | IEEE 1394a 2000 / IEEE 1394-1995 OHCI Link Layer Controller | VIA |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |