|

|

PDF ADSP2192M Data sheet ( Hoja de datos )

| Número de pieza | ADSP2192M | |

| Descripción | DSP Microcomputer | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADSP2192M (archivo pdf) en la parte inferior de esta página. Total 40 Páginas | ||

|

No Preview Available !

ataSheet4U.com DSP MADicSrPo-c2o1m9p2uMterADSP-2192M DUAL CORE DSP FEATURES

320 MIPS ADSP-219x DSP in a 144-Lead LQFP Package

awith PCI, USB, Sub-ISA, and CardBus Interfaces

.D3.3 V/5.0 V PCI 2.2 Compliant 33 MHz/32-bit Interface

wwith Bus Mastering over Four DMA Channels with

Scatter-Gather Support

w Integrated USB 1.1 Compliant Interface

w Sub-ISA Interface

mAC’97 Revision 2.1 Compliant Interface for External

Audio, Modem, and Handset Codecs with DMA

oCapability

Dual ADSP-219x Core Processors (P0 and P1) on Each

.cADSP-2192M DSP Chip

132K Words of Memory Includes 4K ؋ 16-Bit Shared

Data Memory

80K Words of On-Chip RAM on P0, Configured as

64K Words On-Chip 16-Bit RAM for Data Memory and

16K Words On-Chip 24-Bit RAM for Program Memory

48K Words of On-Chip RAM on P1, Configured as

32K Words On-Chip 16-Bit RAM for Data Memory and

16K Words On-Chip 24-Bit RAM for Program Memory

4K Words of Additional On-Chip RAM Shared by Both

Cores, Configured as 4K Words On-Chip 16-Bit RAM

Flexible Power Management with Selectable Power-

Down and Idle Modes

Programmable PLL Supports Frequency Multiplication,

Enabling Full Speed Operation from Low Speed

Input Clocks

2.5 V Internal Operation Supports 3.3 V/5.0 V

Compliant I/O

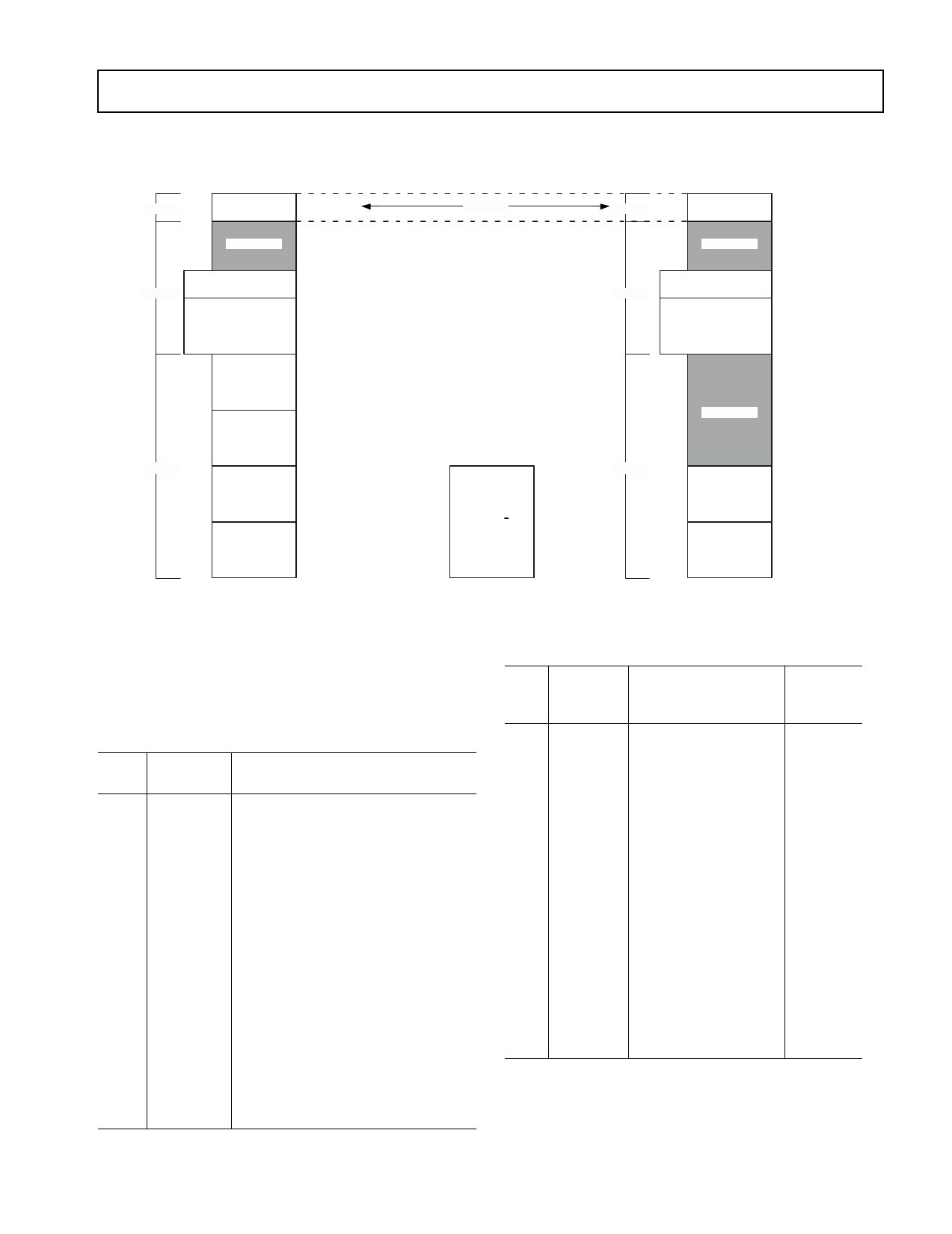

heet4UADSP-219x

SDSP CORE

FUNCTIONAL BLOCK DIAGRAM

P0

MEMORY

16K؋24 PM

64K؋16 DM

BOOT ROM

ADDR DATA

SHARED

MEMORY

4K؋16 DM

ADDR DATA

P1

MEMORY

16K؋24 PM

32K؋16 DM

BOOT ROM

ADDR DATA

ADSP-219x

DSP CORE

ta(SEE FIGURE 1

ON PAGE 3)

.DaCORE

INTERFACE

PROCESSOR P0

ADDR DATA

P0 DMA

w CONTROLLER

w FIFOS

ADDR DATA

SHARED DSP

I/O MAPPED

REGISTERS

(SEE FIGURE 1

ON PAGE 3)

CORE

INTERFACE

ADDR DATA

PROCESSOR P1

P1 DMA

CONTROLLER

FIFOS

w t4U.comGP I/O PINS

(AND

eOPTIONAL

SERIAL

eEEPROM)

SERIAL PORT

AC'97

COMPLIANT

HOST PORT

PCI 2.2

OR

USB 1.1

JTAG

EMULATION

PORT

ataShREV. 0

.DInformation furnished by Analog Devices is believed to be accurate and

wreliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

wmay result from its use. No license is granted by implication or otherwise

wunder any patent or patent rights of Analog Devices. Trademarks and

One Technology Way, P.O.Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel:781/329-4700

www.analog.com

registered trademarks are the property of their respective companies.

Fax:781/326-8703

© 2002 Analog Devices, Inc. All rights reserved.

1 page

ADSP-2192M

PAGE 2

PAGE 1

PAGE 0

DSP P0

MEMORY MAP

ADDRESS

SHARED RAM

(16 ؋ 4K)

0x02 0FFF

0x02 0000

0x01 FFFF

RESE RVED

PROGRAM ROM

24 ؋ 4K

0x01 5000

0x01 4FFF

0x01 4000

PROGRAM RAM

(24 ؋ 16K)

0x01 3FFF

0x01 0000

DATA RAM

BLO CK3

(16 ؋ 16K)

0x00 FFFF

0x00 C000

DATA RAM

BLO CK2

(16 ؋ 16K)

0x00 BFFF

0x00 8000

DATA RAM

BLO CK1

(16 ؋ 16K)

0x00 7FFF

0x00 4000

DATA RAM

BLO CK0

(16 ؋ 16K)

0x00 3FFF

0x00 0000

SAME

PAGE 2

PAGE 1

SHARED

DSP I/O

MAPPED

REGISTERS

ADDRE SS

0xFF FF

PAGE 0

PAGES 0 255

(16 ؋ 256)

0x00 00

DSP P1

MEMORY MAP

ADDRESS

SHARED RAM

(16 ؋ 4K)

0x02 0FF F

0x02 0000

0x01 FFFF

RES ERVED

PROGRAM ROM

24 ؋ 4K

0x01 5000

0x01 4FF F

0x01 4000

PROGRAM RAM

(24 ؋ 16K)

0x01 3FF F

0x01 0000

0x00 FFFF

RES ERVED

DATA RAM

BLO CK1

(16 ؋ 16K)

DATA RAM

BLO CK0

(16 ؋ 16K)

0x00 8000

0x00 7FF F

0x00 4000

0x00 3FF F

0x00 0000

Figure 2. ADSP-2192M Internal/External Memory, Boot Memory, and I/O Memory Maps

Table 2 shows the interrupt vector and DSP-to-DSP semaphores

at reset of each of the peripheral interrupts. The peripheral inter-

rupt’s position in the IMASK and IRPTL register and its vector

address depend on its priority level, as shown in Table 2.

Table 1. DSP-to-DSP Semaphores Register Table

Flag

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Direction

Output

Output

Output

Output

Input

Input

Input

Input

Input

Input

Input

Input

Function

DSP–DSP Semaphore 0

DSP–DSP Semaphore 1

DSP–DSP Interrupt

Reserved

Reserved

Reserved

Reserved

Register Bus Lock

DSP–DSP Semaphore 0

DSP–DSP Semaphore 1

DSP–DSP Interrupt

Reserved

AC’97 Register–PDC Bus Access

Status

PDC Interface Busy Status (write

from DSP pending)

Reserved

Register Bus Lock Status

Table 2. Vector Table

Bit Priority Interrupt

Vector

Address

Offset1

01

12

23

34

45

56

67

78

89

9 10

10 11

11 12

12 13

13 14

14 15

15 16

Reset (non-maskable)

Power-Down (non-

maskable)

Kernel interrupt

(single step)

Stack Status

Mailbox

Timer

GPIO

PCI Bus Master

DSP–DSP

FIFO0 Transmit

FIFO0 Receive

FIFO1 Transmit

FIFO1 Receive

Reserved

Reserved

AC’97 Frame

0x00

0x04

0x08

0x0C

0x10

0x14

0x18

0x1C

0x20

0x24

0x28

0x2C

0x30

0x34

0x38

0x3C

1The interrupt vector address values are represented as offsets from

address 0x01 0000. This address corresponds to the start of Program

Memory in DSP P0 and P1.

REV. 0

–5–

5 Page

ADSP-2192M

PCI DWORD

BYTE3 IS

ALWAYS

UNUSED

PCI BYTE ADDRESS

BYTE0 IS UNUSED

BY 16-BIT MEMORY

LOCATIONS

0x0 0000

ALLOWED BYTE

ENABLES:

CBE = 1100

CBE = 0011

0x0 FFFC

0x1 0000

0x1 FFFC

BYTE3

UNUSED

BYTE2

BYTE1

16K ؋ 24-BIT BLOCK

16K ؋ 16-BIT BLOCK

BYTE0

DSP WORD ADDRESS

0x0000

UNUSED

0x3FFF

0x4000

0x7FFF

Figure 3. PCI Addressing for 24-Bit and 16-Bit Memory Blocks in 24-Bit Access (BAR2) Mode

PCI DWORD

PCI BYTE ADDRESS

BYTE3

BYTE2

DATA WORD N + 1

BYTE1

BYTE0

DATA WORD N

DSP WORD ADDRESS

0x0 0000

ALL BYTES ARE USED.

ALLOWED BYTE

ENABLES:

CBE = 1100

CBE = 0011

CBE = 0000

0x0 7FFE

0x0 8000

0x0 FFFE

DATA WORD N

DATA WORD N + 1

16K ؋ 24-BIT BLOCK

16K ؋ 16-BIT BLOCK

UNUSED

UNUSED

0x0000

0x3FFF

0x4000

0x7FFF

Figure 4. PCI Addressing for 24-Bit and 16-Bit Memory Blocks in 16-Bit Access (BAR3) Mode

24-Bit PCI DSP Memory Map (BAR2)

The complete PCI address footprint for the ADSP-2192M DSP

Memory Spaces in 24-bit (BAR2) Mode is shown in Table 8.

Table 8. 24-Bit PCI DSP Memory Map (BAR2 Mode)1

Block

DSP P0 Data RAM

Block 0

DSP P0 Data RAM

Block 1

DSP P0 Data RAM

Block 2

DSP P0 Data RAM

Block 3

DSP P0 Program RAM

Block

Byte3

UNUSED

UNUSED

...

UNUSED

UNUSED

UNUSED

...

UNUSED

UNUSED

UNUSED

...

UNUSED

UNUSED

UNUSED

...

UNUSED

UNUSED

UNUSED

...

UNUSED

Byte2

D[15:8]

D[15:8]

...

D[15:8]

D[15:8]

D[15:8]

...

D[15:8]

D[15:8]

D[15:8]

...

D[15:8]

D[15:8]

D[15:8]

...

D[15:8]

D[23:16]

D[23:16]

...

D[23:16]

Byte1

D[7:0]

D[7:0]

...

D[7:0]

D[7:0]

D[7:0]

...

D[7:0]

D[7:0]

D[7:0]

...

D[7:0]

D[7:0]

D[7:0]

...

D[7:0]

D[15:8]

D[15:8]

...

D[15:8]

Byte0

UNUSED

UNUSED

...

UNUSED

UNUSED

UNUSED

...

UNUSED

UNUSED

UNUSED

...

UNUSED

UNUSED

UNUSED

...

UNUSED

D[7:0]

D[7:0]

...

D[7:0]

Offset

0x0000 0000

0x0000 0004

...

0x0000 FFFC

0x0001 0000

0x0001 0004

...

0x0001 FFFC

0x0002 0000

0x0002 0004

...

0x0002 FFFC

0x0003 0000

0x0003 0004

...

0x0003 FFFC

0x0004 0000

0x0004 0004

...

0x0004 FFFC

REV. 0

–11–

11 Page | ||

| Páginas | Total 40 Páginas | |

| PDF Descargar | [ Datasheet ADSP2192M.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADSP2192M | DSP Microcomputer | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |