|

|

PDF S71PL032J Data sheet ( Hoja de datos )

| Número de pieza | S71PL032J | |

| Descripción | (S71PLxxx) STACKED MULTI CHIP PRODUCT FLASH MEMORY AND RAM | |

| Fabricantes | SPANSION | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de S71PL032J (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

S71PL254/127/064/032J based MCPs

Stacked Multi-Chip Product (MCP) Flash Memory and RAM

256M/128/64/32 Megabit (16/8/4/2M x 16-bit) CMOS 3.0 Volt-only

Simultaneous Operation Page Mode Flash Memory and

64/32/16/8/4 Megabit (4M/2M/1M/512K/256K x 16-bit) Static

RAM/Pseudo Static RAM

Datasheet

ADVANCE

Distinctive Characteristics

MCP Features

Power supply voltage of 2.7 to 3.1 volt

High performance

— 55 ns

— 65 ns (65 ns Flash, 70ns pSRAM)

Packages

— 7 x 9 x 1.2mm 56 ball FBGA

— 8 x 11.6 x 1.2mm 64 ball FBGA

— 8 x 11.6 x 1.4mm 84 ball FBGA

Operating Temperature

— –25°C to +85°C

— –40°C to +85°C

General Description

The S71PL series is a product line of stacked Multi-Chip Product (MCP) packages

and consists of:

One or more S29PL (Simultaneous Read/Write) Flash memory die

pSRAM or SRAM

The 256Mb Flash memory consists of two S29PL127J devices. In this case, CE#f2

is used to access the second Flash and no extra address lines are required.

The products covered by this document are listed in the table below:

pSRAM

Density

4Mb

8Mb

16Mb

32Mb

64Mb

32Mb

S71PL032J40

S71PL032J80

S71PL032JA0

Flash Memory Density

64Mb

128Mb

S71PL064J80

S71PL064JA0

S71PL064JB0

S71PL127JA0

S71PL127JB0

S71PL127JC0

256Mb

S71PL254JB0

S71PL254JC0

SRAM Density (Note)

Flash Memory Density

32Mb

64Mb

4Mb S71PL032J04

8Mb

S71PL032J08

S71PL064J08

Note: Not recommended for new designs; use pSRAM based MCPs instead.

www.DataSheet4U.com

Publication Number S71PL254/127/064/032J_00 Revision A Amendment 6 Issue Date November 22, 2004

www.DataSheet4U.com

1 page

Advance Information

Figure 6. Data# Polling Algorithm......................................... 76

RY/BY#: Ready/Busy# .......................................................................................76

DQ6: Toggle Bit I ................................................................................................76

Figure 7. Toggle Bit Algorithm.............................................. 78

DQ2: Toggle Bit II .............................................................................................. 78

Reading Toggle Bits DQ6/DQ2 ..................................................................... 78

DQ5: Exceeded Timing Limits ........................................................................79

DQ3: Sector Erase Timer .................................................................................79

Table 19. Write Operation Status ......................................... 80

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . 81

Figure 8. Maximum Overshoot Waveforms............................. 81

Operating Ranges . . . . . . . . . . . . . . . . . . . . . . . . . .82

Industrial (I) Devices ......................................................................................... 82

Wireless Devices ............................................................................................... 82

Supply Voltages ................................................................................................... 82

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . .83

Table 20. CMOS Compatible ................................................ 83

AC Characteristic . . . . . . . . . . . . . . . . . . . . . . . . . .84

Test Conditions .................................................................................................. 84

Figure 9. Test Setups......................................................... 84

Table 21. Test Specifications ............................................... 84

Switching Waveforms ....................................................................................... 85

Table 22. Key to Switching Waveforms ................................. 85

Figure 10. Input Waveforms and Measurement Levels............. 85

VCC RampRate .................................................................................................. 85

Read Operations ................................................................................................ 86

Table 23. Read-Only Operations .......................................... 86

Figure 11. Read Operation Timings ....................................... 86

Figure 12. Page Read Operation Timings ............................... 87

Reset ...................................................................................................................... 87

Table 24. Hardware Reset (RESET#) .................................... 87

Figure 13. Reset Timings..................................................... 88

Erase/Program Operations ............................................................................. 89

Table 25. Erase and Program Operations .............................. 89

Timing Diagrams ................................................................................................. 90

Figure 14. Program Operation Timings .................................. 90

Figure 15. Accelerated Program Timing Diagram .................... 90

Figure 16. Chip/Sector Erase Operation Timings ..................... 91

Figure 17. Back-to-back Read/Write Cycle Timings ................. 91

Figure 18. Data# Polling Timings

(During Embedded Algorithms) ............................................ 92

Figure 19. Toggle Bit Timings (During Embedded Algorithms) .. 92

Figure 20. DQ2 vs. DQ6 ...................................................... 93

Protect/Unprotect . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 26. Temporary Sector Unprotect ................................. 93

Figure 21. Temporary Sector Unprotect Timing Diagram.......... 93

Figure 22. Sector/Sector Block Protect and Unprotect Timing

Diagram............................................................................ 94

Controlled Erase Operations ..........................................................................95

Table 27. Alternate CE# Controlled Erase and

Program Operations ........................................................... 95

Table 28. Alternate CE# Controlled Write (Erase/Program)

Operation Timings ............................................................. 96

Table 29. Erase And Programming Performance .................... 97

BGA Pin Capacitance . . . . . . . . . . . . . . . . . . . . . . 97

Type 2 pSRAM

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Product Information . . . . . . . . . . . . . . . . . . . . . . . 98

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Power Up Sequence . . . . . . . . . . . . . . . . . . . . . . . 99

November 22, 2004 S71PL254/127/064/032J_00_A6

Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . 99

Power Up ..............................................................................................................99

Figure 23. Power Up 1 (CS1# Controlled) ............................. 99

Figure 24. Power Up 2 (CS2 Controlled)................................ 99

Functional Description . . . . . . . . . . . . . . . . . . . . . 100

Absolute Maximum Ratings . . . . . . . . . . . . . . . . 100

DC Recommended Operating Conditions . . . . . 100

DC and Operating Characteristics . . . . . . . . . . . 101

Common ...............................................................................................................101

16M pSRAM ..........................................................................................................102

32M pSRAM .........................................................................................................102

64M pSRAM .........................................................................................................103

AC Operating Conditions . . . . . . . . . . . . . . . . . . 103

Test Conditions (Test Load and Test Input/Output Reference) ........103

Figure 25. Output Load .................................................... 103

ACC Characteristics (Ta = -40°C to 85°C, VCC = 2.7 to 3.1 V) ........104

Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . 105

Read Timings .......................................................................................................105

Figure 26. Timing Waveform of Read Cycle(1) ..................... 105

Figure 27. Timing Waveform of Read Cycle(2) ..................... 105

Figure 28. Timing Waveform of Read Cycle(2) ..................... 105

Write Timings .....................................................................................................106

Figure 29. Write Cycle #1 (WE# Controlled)........................ 106

Figure 30. Write Cycle #2 (CS1# Controlled) ...................... 106

Figure 31. Timing Waveform of Write Cycle(3)

(CS2 Controlled) ............................................................. 107

Figure 32. Timing Waveform of Write Cycle(4) (UB#, LB#

Controlled) ..................................................................... 107

pSRAM Type 3

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Operation Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 109

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 30. DC Recommended Operating Conditions ............... 109

Table 31. DC Characteristics (TA = -25°C to 85°C, VDD = 2.6 to

3.3V) ............................................................................. 110

AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 32. AC Characteristics and Operating Conditions (TA = -25°C

to 85°C, VDD = 2.6 to 3.3V) .............................................. 110

Table 33. AC Test Conditions ............................................. 111

Figure 33. AC Test Loads .................................................. 111

Figure 34. State Diagram ................................................. 112

Table 34. Standby Mode Characteristics .............................. 112

Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . 112

Figure 35. Read Cycle 1—Addressed Controlled ................... 112

Figure 36. Read Cycle 2—CS1# Controlled.......................... 113

Figure 37. Write Cycle 1—WE# Controlled .......................... 113

Figure 38. Write Cycle 2—CS1# Controlled ......................... 114

Figure 39. Write Cycle3—UB#, LB# Controlled .................... 114

Figure 40. Deep Power-down Mode .................................... 115

Figure 41. Power-up Mode ................................................ 115

Figure 42. Abnormal Timing .............................................. 115

pSRAM Type 4

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Functional Description . . . . . . . . . . . . . . . . . . . . . 116

Product Portfolio ................................................................................................116

Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . 117

5

5 Page

Advance Information

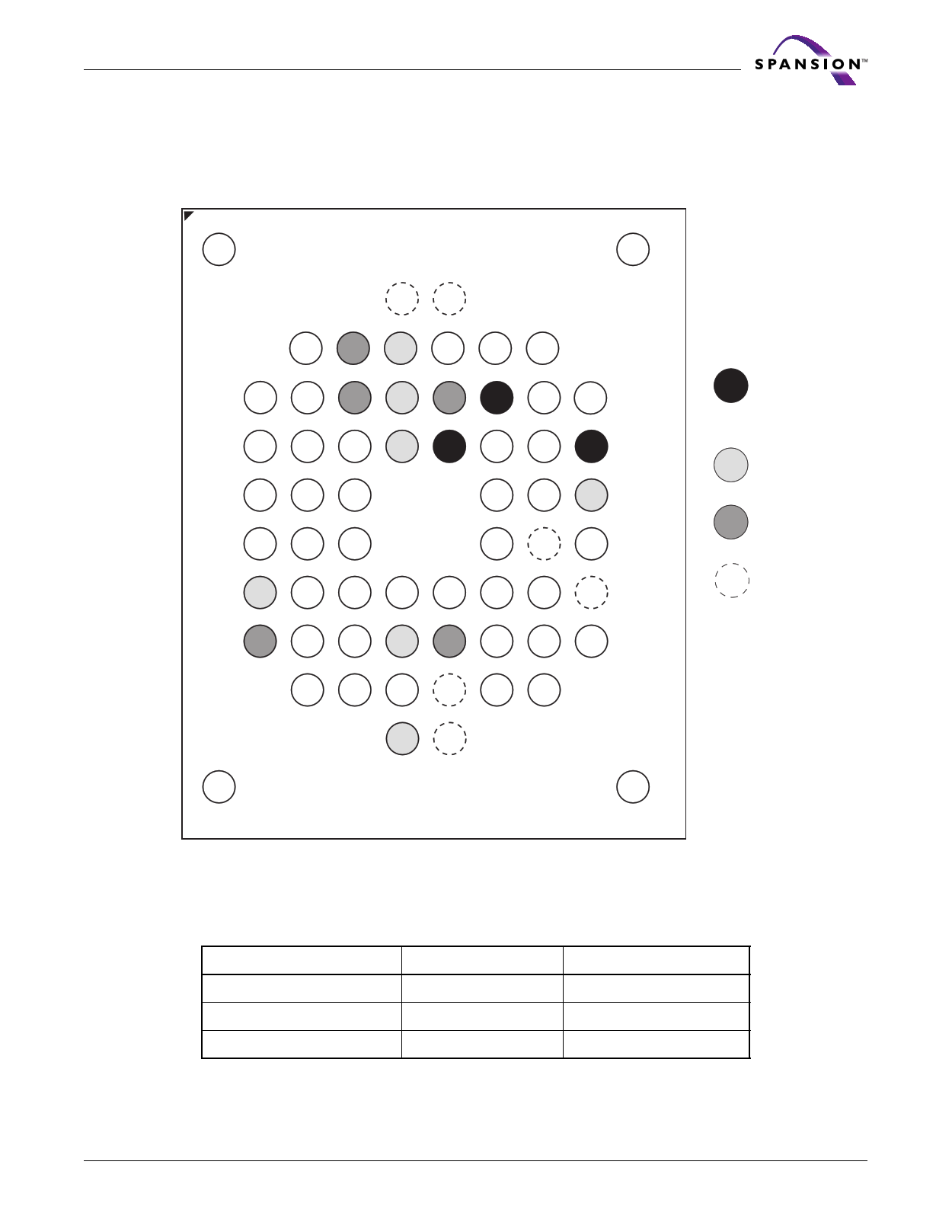

Connection Diagram (S71PL127J)

64-ball Fine-Pitch Ball Grid Array

(Top View, Balls Facing Down)

A1

NC

D2

A3

E2

A2

F2

A1

G2

A0

H2

CE#f

J2

CE1#s

C3

A7

D3

A6

E3

A5

F3

A4

G3

VSS

H3

OE#

J3

DQ0

K3

DQ8

M1

NC

B5 B6

RFU

RFU

C4 C5 C6

LB# WP/ACC WE#

D4 D5 D6

UB# RST#f CE2s

E4 E5 E6

A18 RY/BY# A20

F4

A17

G4

DQ1

H4 H5 H6

DQ9

J4

DQ3

J5

DQ4

J6

DQ10 VCCf VCCs

K4 K5 K6

DQ2 DQ11 RFU

L5 L6

RFU*

RFU

*See notes below

C7

A8

D7

A19

E7

A9

F7

A10

G7

DQ6

H7

DQ13

J7

DQ12

K7

DQ5

C8

A11

D8

A12

E8

A13

F8

A14

G8

RFU

H8

DQ15

J8

DQ7

K8

DQ14

D9

A15

E9

A21

F9

A22

G9

A16

H9

RFU

J9

VSS

A10

NC

M10

NC

Legend

Shared

(Note 1)

Flash only

RAM only

Reserved for

Future Use

Notes:

1. May be shared depending on density.

— A21 is shared for the 64M pSRAM configuration.

— A20 is shared for the 32M pSRAM and above configurations.

1. A19 is shared for the 16M pSRAM and above configurations.

MCP

Flash-only Addresses

Shared Addresses

S71PL127JC0

S71PL127JB0

S71PL127JA0

A22

A22-A21

A22-A20

A21-A0

A20-A0

A19-A0

2. Connecting all Vcc & Vss balls to Vcc & Vss is recommended.

3. Ball L5 will be Vccf in the 84-ball density upgrades. Do not connect to Vss or any other signal.

November 22, 2004 S71PL254/127/064/032J_00_A6

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S71PL032J.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S71PL032J | (S71PLxxx) STACKED MULTI CHIP PRODUCT FLASH MEMORY AND RAM | SPANSION |

| S71PL032J | Based MCPs | SPANSION |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |