|

|

PDF GVT71256ZB36 Data sheet ( Hoja de datos )

| Número de pieza | GVT71256ZB36 | |

| Descripción | (GVT7xxxx) 256K x 36 / 512K x 18 Flow Thru SRAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de GVT71256ZB36 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

( DataSheet : www.DataSheet4U.com )

1CY7C1357A

CY7C1355A/GVT71256ZB36

PRELIMINARY CY7C1357A/GVT71512ZB18

256Kx36/512Kx18 Flow-Thru SRAM with NoBL™ Architecture

Features

• Zero Bus Latency, no dead cycles between write and

read cycles

• Fast clock speed: 133, 117, and 100 MHz

• Fast access time: 6.5, 7.0, 7.5, and 8.0 ns

• Internally synchronized registered outputs eliminate

the need to control OE

• Single 3.3V –5% and +5% power supply VCC

• Separate VCCQ for 3.3V or 2.5V I/O

• Single R/W (READ/WRITE) control pin

• Positive clock-edge triggered, address, data, and con-

trol signal registers for fully pipelined applications

• Interleaved or linear 4-word burst capability

• Individual byte write (BWa–BWd) control (may be tied

LOW)

• CKE pin to enable clock and suspend operations

• Three chip enables for simple depth expansion

• SNOOZE MODE for low power standby

• JTAG boundary scan

• Low profile 119-bump, 14-mm x 22-mm BGA (Ball Grid

Array) and 100-pin TQFP packages

Functional Description

The CY7C1355A/GVT71256ZB36 and CY7C1357A/

GVT71512ZB18 SRAMs are designed to eliminate dead cy-

cles when transitions from READ to WRITE or vice versa.

These SRAMs are optimized for 100 percent bus utilization

and achieves Zero Bus Latency (ZBL)/No Bus Latency (No-

BL). They integrate 262,144x36 and 524,288x18 SRAM cells,

respectively, with advanced synchronous peripheral circuitry

and a 2-bit counter for internal burst operation. These employ

high-speed, low power CMOS designs using advanced triple-

layer polysilicon, double-layer metal technology. Each memory

cell consists of four transistors and two high valued resistors.

All synchronous inputs are gated by registers controlled by a

positive-edge-triggered Clock Input (CLK). The synchronous

inputs include all addresses, all data inputs, depth-expansion

Chip Enables (CE, CE2, and CE2), Cycle Start Input (ADV/LD),

Clock Enable (CKE), Byte Write Enables (BWa, BWb, BWc,

and BWd), and read-write control (R/W). BWc and BWd apply

to CY7C1355A/GVT71256ZB36 only.

Address and control signals are applied to the SRAM during

one clock cycle, and one cycle later, its associated data oc-

curs, either read or write.

A Clock Enable (CKE) pin allows operation of the

CY7C1355A/CY7C1357A/GVT71256ZB36/GVT71512ZB18

to be suspended as long as necessary. All synchronous inputs

are ignored when (CKE) is HIGH and the internal device reg-

isters will hold their previous values.

There are three Chip Enable pins (CE, CE2, CE2) that allow

the user to deselect the device when desired. If any one of

these three are not active when ADV/LD is LOW, no new mem-

ory operation can be initiated and any burst cycle in progress

is stopped. However, any pending data transfers (read or write)

will be completed. The data bus will be in high-impedance

state one cycle after chip is deselected or a write cycle is initi-

ated.

The CY7C1355A/GVT71256ZB36 and CY7C1357A/

GVT71512ZB18 have an on-chip 2-bit burst counter. In the

burst mode, the CY7C1355A/GVT71256ZB36 and

CY7C1357A/GVT71512ZB18 provide four cycles of data for a

single address presented to the SRAM. The order of the burst

sequence is defined by the MODE input pin. The MODE pin

selects between linear and interleaved burst sequence. The

ADV/LD signal is used to load a new external address

(ADV/LD=LOW) or increment the internal burst counter

(ADV/LD=HIGH)

Output Enable (OE), Snooze Enable (ZZ) and burst sequence

select (MODE) are the asynchronous signals. OE can be used

to disable the outputs at any given time. ZZ may be tied to LOW

if it is not used.

Four pins are used to implement JTAG test capabilities. The

JTAG circuitry is used to serially shift data to and from the

device. JTAG inputs use LVTTL/LVCMOS levels to shift data

during this testing mode of operation.

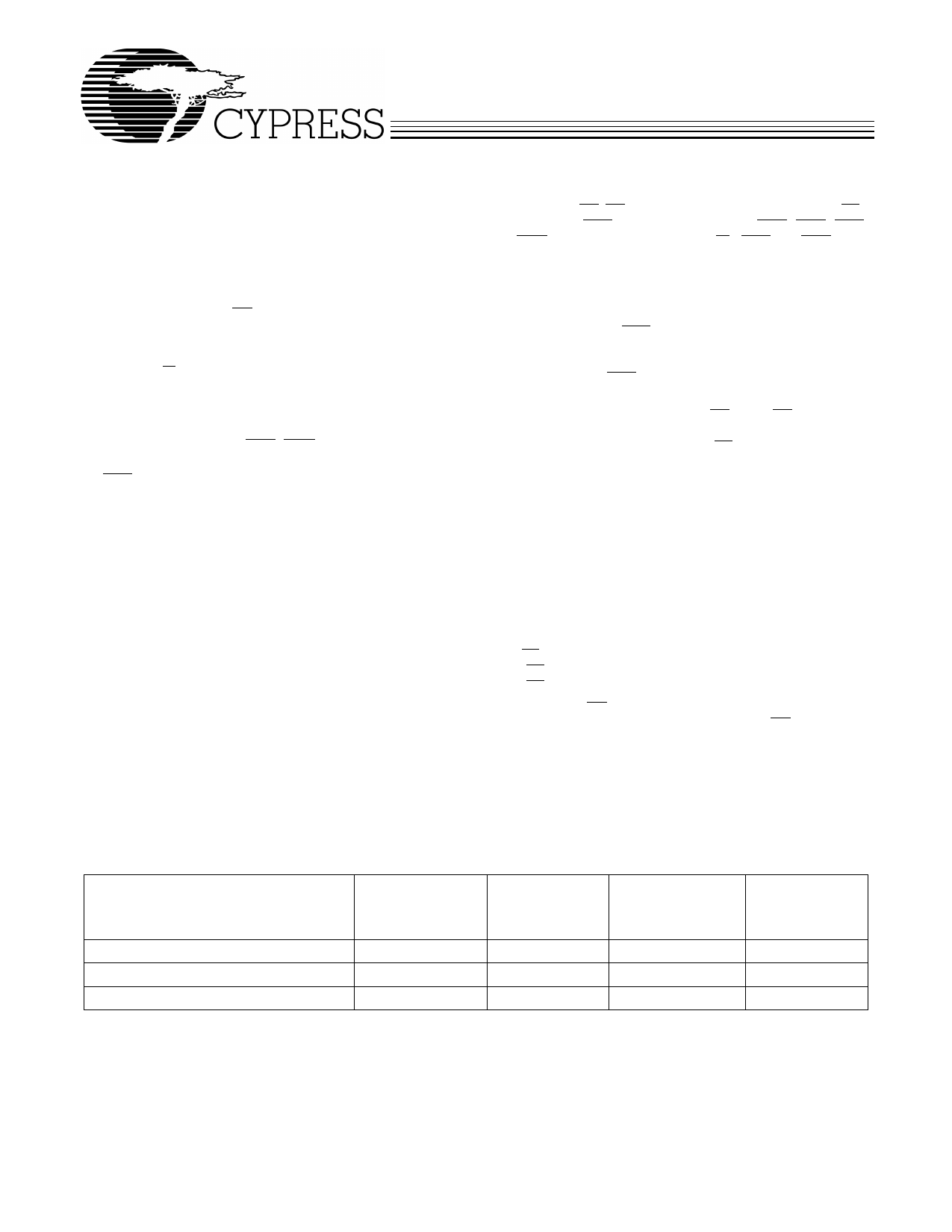

Selection Guide

7C1355A-133/

71256ZB36-6.5

7C1357A-133/

71512ZB18-6.5

Maximum Access Time (ns)

6.5

Maximum Operating Current (mA)

410

Maximum CMOS Standby Current (mA)

30

No Bus Latency and NoBL are trademarks of Cypress Semiconductor Corporation.

7C1355A-117/

71256ZB36-7

7C1357A-117/

71512ZB18-7

7

385

30

7C1355A-100/

71256ZB36-7.5

7C1357A-100/

71512ZB18-7.5

7.5

350

30

7C1355A1-100/

71256ZB36-8

7C1357A1-100/

71512ZB18-8

8

350

30

www.DataSheet4U.com

wwwC.yDparteaSshseSete4mU.iccoomnductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

May 24, 2001

1 page

PRELIMINARY

CY7C1355A/GVT71256ZB36

CY7C1357A/GVT71512ZB18

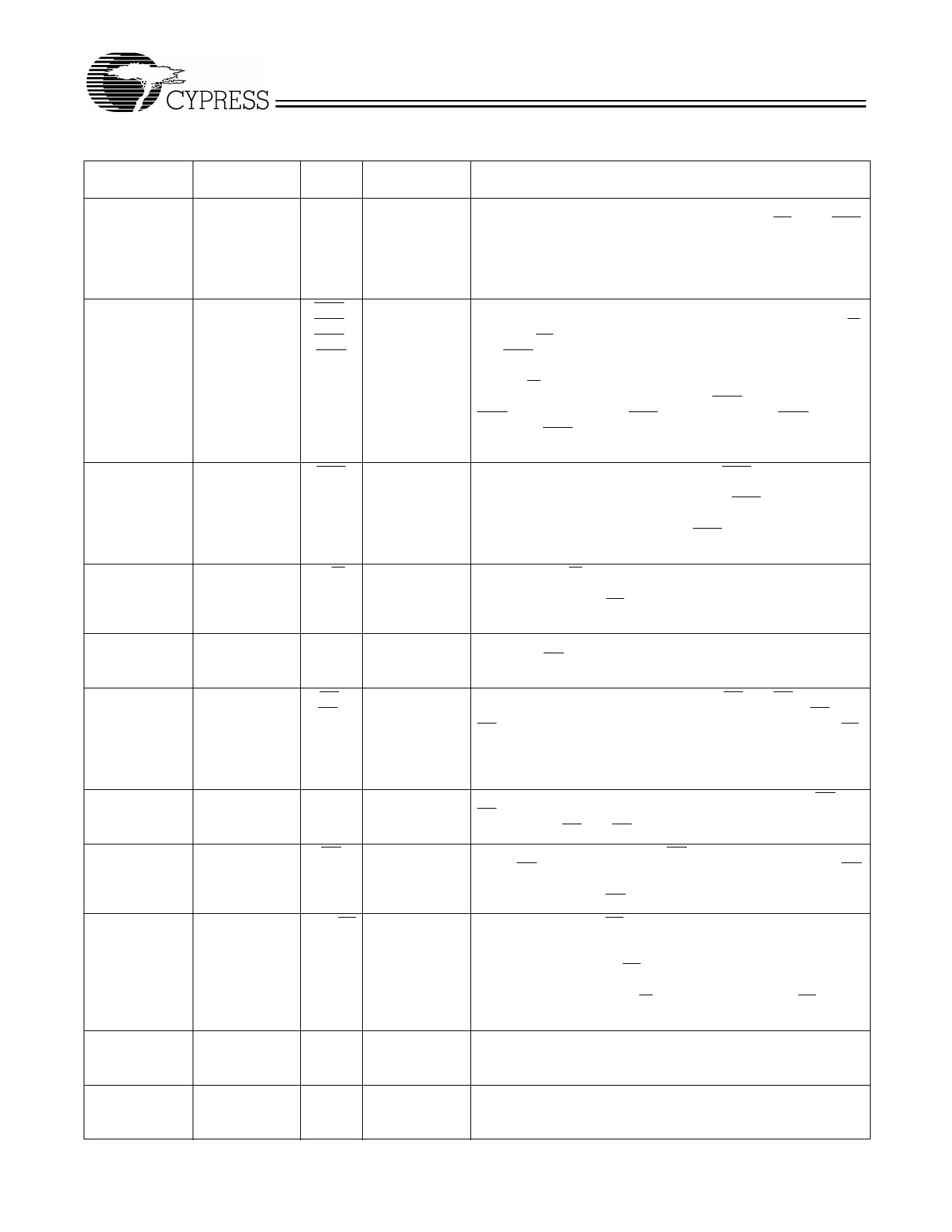

Pin Descriptions (CY7C1355A/GVT71256ZB36)

256Kx36

TQFP Pins

37,

36,

32, 33, 34, 35,

44, 45, 46, 47,

48, 49, 50, 81,

82, 83, 99, 100

93,

94,

95,

96

87

88

89

98, 92

97

86

85

31

64

256Kx36

PBGA Pins

4P

4N

2A, 3A, 5A, 6A,

3B, 5B, 2C, 3C,

5C, 6C, 4G, 2R,

6R, 3T, 4T, 5T

5L

5G

3G

3L

4M

4H

4K

4E, 6B

2B

4F

4B

3R

7T

Name

SA0,

SA1,

SA

BWa,

BWb,

BWc,

BWd

CKE

R/W

CLK

CE,

CE2

CE2

OE

ADV/LD

MODE

ZZ

Type

Input-

Synchronous

Input-

Synchronous

Input-

Synchronous

Input-

Synchronous

Input-

Synchronous

Input-

Synchronous

Input-

Synchronous

Input

Input-

Synchronous

Input-

Static

Input-

Asynchronous

Description

Synchronous Address Inputs: The address register is triggered

by a combination of the rising edge of CLK, ADV/LD LOW, CKE

LOW and true chip enables. SA0 and SA1 are the two least

significant bits of the address field and set the internal burst

counter if burst cycle is initiated.

Synchronous Byte Write Enables: Each 9-bit byte has its own

active LOW byte write enable. On load write cycles (when R/W

and ADV/LD are sampled LOW), the appropriate byte write sig-

nal (BWx) must be valid. The byte write signal must also be valid

on each cycle of a burst write. Byte write signals are ignored

when R/W is sampled HIGH. The appropriate byte(s) of data are

written into the device one cycle later. BWa controls DQa pins;

BWb controls DQb pins; BWc controls DQc pins; BWd controls

DQd pins. BWx can all be tied LOW if always doing a write to

the entire 36-bit word.

Synchronous Clock Enable Input: When CKE is sampled HIGH,

all other synchronous inputs, including clock are ignored and

outputs remain unchanged. The effect of CKE sampled HIGH

on the device outputs is as if the LOW-to-HIGH clock transition

did not occur. For normal operation, CKE must be sampled LOW

at rising edge of clock.

Read Write: R/W signal is a synchronous input that identifies

whether the current loaded cycle and the subsequent burst cy-

cles initiated by ADV/LD is a Read or Write operation. The data

bus activity for the current cycle takes place one clock cycle later.

Clock: This is the clock input to CY7C1355A/GVT71256ZB36.

Except for OE, ZZ, and MODE, all timing references for the de-

vice are made with respect to the rising edge of CLK.

Synchronous Active LOW Chip Enable: CE and CE2 are used

with CE2 to enable the CY7C1355A/GVT71256ZB36. CE or

CE2 sampled HIGH or CE2 sampled LOW, along with ADV/LD

LOW at the rising edge of clock, initiates a deselect cycle. The

data bus will be High-Z one clock cycle after chip deselect is

initiated.

Synchronous Active High Chip enable: CE2 is used with CE and

CE2 to enable the chip. CE2 has inverted polarity but otherwise

is identical to CE and CE2.

Asynchronous Output Enable: OE must be LOW to read data.

When OE is HIGH, the I/O pins are in high-impedance state. OE

does not need to be actively controlled for read and write cycles.

In normal operation, OE can be tied LOW.

Advance/Load: ADV/LD is a synchronous input that is used to

load the internal registers with new address and control signals

when it is sampled LOW at the rising edge of clock with the chip

is selected. When ADV/LD is sampled HIGH, then the internal

burst counter is advanced for any burst that was in progress. The

external addresses and R/W are ignored when ADV/LD is sam-

pled HIGH.

Burst Mode: When MODE is HIGH or NC, the interleaved burst

sequence is selected. When MODE is LOW, the linear burst

sequence is selected. MODE is a static DC input.

Snooze Enable: This active HIGH input puts the device in low

power consumption standby mode. For normal operation, this

input has to be either LOW or NC.

5

5 Page

PRELIMINARY

CY7C1355A/GVT71256ZB36

CY7C1357A/GVT71512ZB18

Identification (ID) Register

The ID Register is a 32-bit register that is loaded with a device

and vendor specific 32-bit code when the controller is put in

Capture-DR state with the IDCODE command loaded in the

instruction register. The register is then placed between the

TDI and TDO pins when the controller is moved into Shift-DR

state. Bit 0 in the register is the LSB and the first to reach TDO

when shifting begins. The code is loaded from a 32-bit on-chip

ROM. It describes various attributes of the device as described

in the Identification Register Definitions table.

TAP Controller Instruction Set

Overview

There are two classes of instructions defined in the IEEE Stan-

dard 1149.1-1990; the standard (public) instructions and de-

vice specific (private) instructions. Some public instructions

are mandatory for IEEE 1149.1 compliance. Optional public

instructions must be implemented in prescribed ways.

Although the TAP controller in this device follows the IEEE

1149.1 conventions, it is not IEEE 1149.1 compliant because

some of the mandatory instructions are not fully implemented.

The TAP on this device may be used to monitor all input and

I/O pads, but can not be used to load address, data, or control

signals into the device or to preload the I/O buffers. In other

words, the device will not perform IEEE 1149.1 EXTEST, IN-

TEST, or the preload portion of the SAMPLE/PRELOAD com-

mand.

When the TAP controller is placed in Capture-IR state, the two

least significant bits of the instruction register are loaded with

01. When the controller is moved to the Shift-IR state the in-

struction is serially loaded through the TDI input (while the

previous contents are shifted out at TDO). For all instructions,

the TAP executes newly loaded instructions only when the con-

troller is moved to Update-IR state. The TAP instruction sets

for this device are listed in the following tables.

EXTEST

EXTEST is an IEEE 1149.1 mandatory public instruction. It is

to be executed whenever the instruction register is loaded with

all 0s. EXTEST is not implemented in this device.

The TAP controller does recognize an all-0 instruction. When

an EXTEST instruction is loaded into the instruction register,

the device responds as if a SAMPLE/PRELOAD instruction

has been loaded. There is one difference between two instruc-

tions. Unlike SAMPLE/PRELOAD instruction, EXTEST places

the device outputs in a High-Z state.

IDCODE

The IDCODE instruction causes a vendor-specific, 32-bit code

to be loaded into the ID register when the controller is in Cap-

ture-DR mode and places the ID register between the TDI and

TDO pins in Shift-DR mode. The IDCODE instruction is the

default instruction loaded in the instruction upon power-up and

at any time the TAP controller is placed in the test-logic reset

state.

SAMPLE-Z

If the High-Z instruction is loaded in the instruction register, all

output pins are forced to a High-Z state and the boundary scan

register is connected between TDI and TDO pins when the

TAP controller is in a Shift-DR state.

SAMPLE/PRELOAD

SAMPLE/PRELOAD is an IEEE 1149.1 mandatory instruction.

The PRELOAD portion of the command is not implemented in

this device, so the device TAP controller is not fully IEEE

1149.1-compliant.

When the SAMPLE/PRELOAD instruction is loaded in the in-

struction register and the TAP controller is in the Capture-DR

state, a snap shot of the data in the device’s input and I/O

buffers is loaded into the boundary scan register. Because the

device system clock(s) are independent from the TAP Clock

(TCK), it is possible for the TAP to attempt to capture the input

and I/O ring contents while the buffers are in transition (i.e., in

a metastable state). Although allowing the TAP to sample

metastable inputs will not harm the device, repeatable results

can not be expected. To guarantee that the boundary scan

register will capture the correct value of a signal, the device

input signals must be stabilized long enough to meet the TAP

controller’s capture set up plus hold time (tCS plus tCH). The

device clock input(s) need not be paused for any other TAP

operation except capturing the input and I/O ring contents into

the boundary scan register.

Moving the controller to Shift-DR state then places the bound-

ary scan register between the TDI and TDO pins. Because the

PRELOAD portion of the command is not implemented in this

device, moving the controller to the Update-DR state with the

SAMPLE/PRELOAD instruction loaded in the instruction reg-

ister has the same effect as the Pause-DR command.

BYPASS

When the BYPASS instruction is loaded in the instruction reg-

ister and the TAP controller is in the Shift-DR state, the bypass

register is placed between TDI and TDO. This allows the board

level scan path to be shortened to facilitate testing of other

devices in the scan path.

Reserved

Do not use these instructions. They are reserved for future

use.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet GVT71256ZB36.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GVT71256ZB36 | (GVT7xxxx) 256K x 36 / 512K x 18 Flow Thru SRAM | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |