|

|

PDF ISPPAC-POWR1220AT8 Data sheet ( Hoja de datos )

| Número de pieza | ISPPAC-POWR1220AT8 | |

| Descripción | In-System Programmable Power Supply | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ISPPAC-POWR1220AT8 (archivo pdf) en la parte inferior de esta página. Total 48 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

ispPAC-® POWR1220AT8

October 2005

In-System Programmable Power Supply

Monitoring, Sequencing and Margining Controller

Preliminary Data Sheet

Features

Application Block Diagram

■ Monitor, Control, and Margin Multiple

Power Supplies

• Simultaneously monitors up to 12 power

Primary

Supply

3.3V

supplies

• Provides up to 20 output control signals

• Provides up to eight analog outputs for

margining/trimming power supply voltages

• Programmable digital and analog circuitry

Primary

Supply

Primary

Supply

2.5V

1.8V

■ Power Supply Margin and Trim Functions

• Trim and margin up to eight power supplies

• Dynamic voltage control through I2C

Primary

Supply

POL#1

• Four hardware selectable voltage profiles

• Independent Digital Closed-Loop Trim function

for each output

■ Embedded PLD for Sequence Control

• 48-macrocell CPLD implements both state

machines and combinatorial logic functions

Primary

Supply

POL#N

8 Analog

Trim

Outputs

Other Control/Supervisory

Signals

16 Digital

Outputs

4 MOSFET

Drivers

■ Embedded Programmable Timers

• Four independent timers

DataSheet4U.com

• 32µs to 2 second intervals for timing sequences

Power Supply

Margin/Trim

Control Block

ADC

■ Analog Input Monitoring

• 12 independent analog monitor inputs

4 Timers

ispPAC-POWR1220AT8

CPLD

48 Macrocells

83 Inputs

6 Digital

Inputs

I2C

Interface

I2C

Bus

CPU

• Differential inputs for remote ground sense

• Two programmable threshold comparators per

analog input

• Hardware window comparison

• 10-bit ADC for I2C monitoring

■ High-Voltage FET Drivers

• Power supply ramp up/down control

• Programmable current and voltage output

• Independently configurable for FET control or

digital output

■ 2-Wire (I2C/SMBus™ Compatible) Interface

Description

Lattice’s Power Manager II ispPAC-POWR1220AT8 is a

general-purpose power-supply monitor, sequence and

margin controller, incorporating both in-system pro-

grammable logic and in-system programmable analog

functions implemented in non-volatile E2CMOS® tech-

nology. The ispPAC-POWR1220AT8 device provides 12

independent analog input channels to monitor up to 12

power supply test points. Each of these input channels

offers a differential input to support remote ground

• Comparator status monitor

sensing, and has two independently programmable

• ADC readout

comparators to support both high/low and in-bounds/

• Direct control of inputs and outputs

out-of-bounds (window-compare) monitor functions. Six

• Power sequence control

general-purpose digital inputs are also provided for mis-

• Dynamic trimming/margining control

cellaneous control functions.

■ 3.3V Operation, Wide Supply Range 2.8V to

3.96V

• In-system programmable through JTAG

• Industrial temperature range: -40°C to +85°C

• 100-pin TQFP package, lead-free option

The ispPAC-POWR1220AT8 provides 20 open-drain

digital outputs that can be used for controlling DC-DC

converters, low-drop-out regulators (LDOs) and opto-

couplers, as well as for supervisory and general-pur-

pose logic interface functions. Four of these outputs

DataShee

© 2005 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other

DataSheet4Ubra.cndoomr product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without

notice.

www.latticesemi.com

1

1220at8_01.0

DataSheet4 U .com

DataSheet4U.com

1 page

www.DataSheet4U.com

Lattice Semiconductor

ispPAC-POWR1220AT8 Data Sheet

et4U.com

Pin Descriptions (Cont.)

Number

Name

Pin Type

Voltage Range

Description

73 TRIM8

Analog Output

-320mV to +320mV

from Programmable

DAC Offset

Trim DAC Output 8

91 RESETb9 Digital I/O

Device Reset (Active Low)

95 PLDCLK Digital Output

250kHz PLD Clock Output (Tristate), CMOS

Output

96 MCLK

Digital I/O

8MHz Clock I/O (Tristate), CMOS Drive

34 TDO

Digital Output

JTAG Test Data Out

37 TCK

Digital Input

JTAG Test Clock Input

28 TMS

Digital Input

JTAG Test Mode Select

31 TDI

Digital Input

JTAG Test Data In, TDISEL pin = 1

30 ATDI

Digital Input

JTAG Test Data In (Alternate), TDISEL Pin = 0

32 TDISEL

Digital Input

Select TDI/ATDI Input

92 SCL

Digital Input

I2C Serial Clock Input

93 SDA

Digital I/O

I2C Serial Data, Bi-directional Pin

44, 59 RESERVED

Reserved - Do Not Connect

26, 27, 29,

35, 41, 49,

76, 77, 78,

NC

81, 99, 100

No Internal Connection

1. [IN1...IN6] are inputs to the PLD. The thresholds for these pins are referenced by the voltage on VCCINP.

2. IN1 pin can also be controlled through JTAG interface.

3. [IN2..IN6] can also be controlled through I2C/SMBus inteDrfaactea.Sheet4U.com

4. The VMON inputs can be biased independently from VCCA.

5. The VMONGS inputs are the ground sense line for each given VMON pin. The VMON input pins along with the VMONGS ground sense

pins implement a differential pair for each voltage monitor to allow remote sense at the load. VMONGS lines must be connected and are

not to exceed -0.2V - +0.3V in reference to the GNDA pin.

6. Open-drain outputs require an external pull-up resistor to a supply.

7. VCCD and VCCA pins must be connected together on the circuit board.

8. GNDA and GNDD pins must be connected together on the circuit board.

9. The RESETb pin should only be used for cascading two or more ispPAC-POWR1220AT8 devices.

DataShee

DataSheet4U.com

DataSheet4 U .com

5

DataSheet4U.com

5 Page

www.DataSheet4U.com

Lattice Semiconductor

ispPAC-POWR1220AT8 Data Sheet

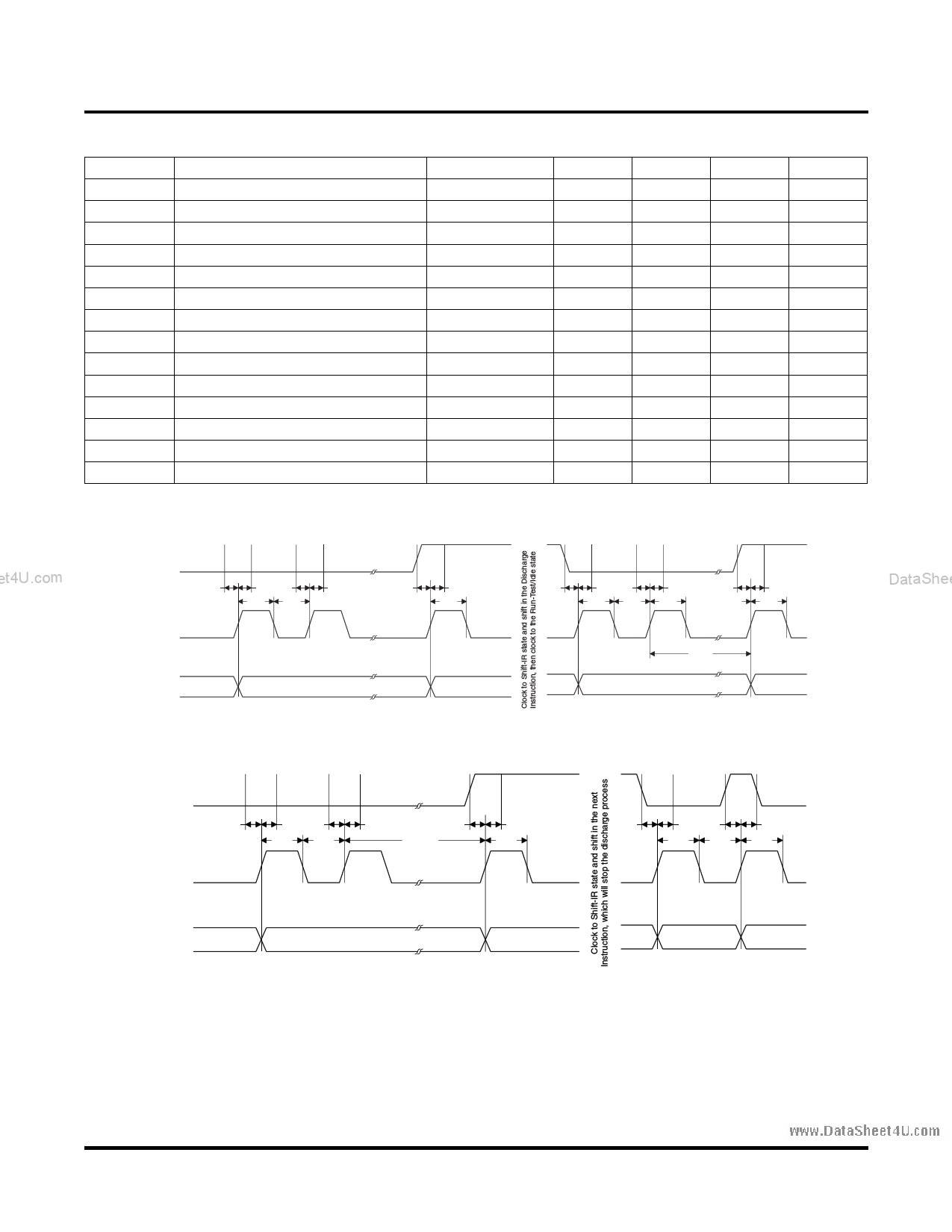

Timing for JTAG Operations

Symbol

tISPEN

tISPDIS

tHVDIS

tHVDIS

tCEN

tCDIS

tSU1

tH

tCKH

tCKL

fMAX

tCO

tPWV

tPWP

Parameter

Program enable delay time

Program disable delay time

High voltage discharge time, program

High voltage discharge time, erase

Falling edge of TCK to TDO active

Falling edge of TCK to TDO disable

Setup time

Hold time

TCK clock pulse width, high

TCK clock pulse width, low

Maximum TCK clock frequency

Falling edge of TCK to valid output

Verify pulse width

Programming pulse width

Conditions

Min.

10

30

30

200

—

—

5

10

20

20

—

—

30

20

Typ.

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Max.

—

—

—

—

15

15

—

—

—

—

25

15

—

—

Figure 2. Erase (User Erase or Erase All) Timing Diagram

et4U.com

VIH

TMS

VIL

VIH

TCK

VIL

tSU1

tH

tCKH

tSU1

tGKL

tH

tSU1

tH

tSU1

tCKH

DataSheet4U.com

State Update-IR

Run-Test/Idle (Erase)

Select-DR Scan

tH

tCKH

tSU1

tGKL

tH

tCKH

tSU1

tH

tCKH

tSU2

Specified by the Data Sheet

Run-Test/Idle (Discharge)

Units

µs

µs

µs

µs

ns

ns

ns

ns

ns

ns

MHz

ns

µs

ms

DataShee

Figure 3. Programming Timing Diagram

VIH

TMS

VIL

VIH

TCK

VI L

tSU1

tH

tCKH

tSU1

tCKL

tH

tPWP

tSU1

tH

tCKH

tSU1

tH

tCKH

tSU1

tCKL

tH

tCKH

State

Update-IR

Run-Test/Idle (Program)

Select-DR Scan

Update-IR

DataSheet4U.com

DataSheet4 U .com

11

DataSheet4U.com

11 Page | ||

| Páginas | Total 48 Páginas | |

| PDF Descargar | [ Datasheet ISPPAC-POWR1220AT8.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISPPAC-POWR1220AT8 | In-System Programmable Power Supply | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |