|

|

PDF NT5DS128M4BT Data sheet ( Hoja de datos )

| Número de pieza | NT5DS128M4BT | |

| Descripción | (NT5DSxxMxBx) 512Mb DDR SDRAM | |

| Fabricantes | Nanya Techology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NT5DS128M4BT (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

NT5DS128M4BF / NT5DS128M4BT/ NT5DS128M4BG (Green) / NT5DS128M4BS (Green)

NT5DS64M8BF / NT5DS64M8BT/ NT5DS64M8BG (Green) / NT5DS64M8BS (Green)

NT5DS32M16BF / NT5DS32M16BT / NT5DS32M16BG (Green) / NT5DS32M16BS (Green)

512Mb DDR SDRAM

Features

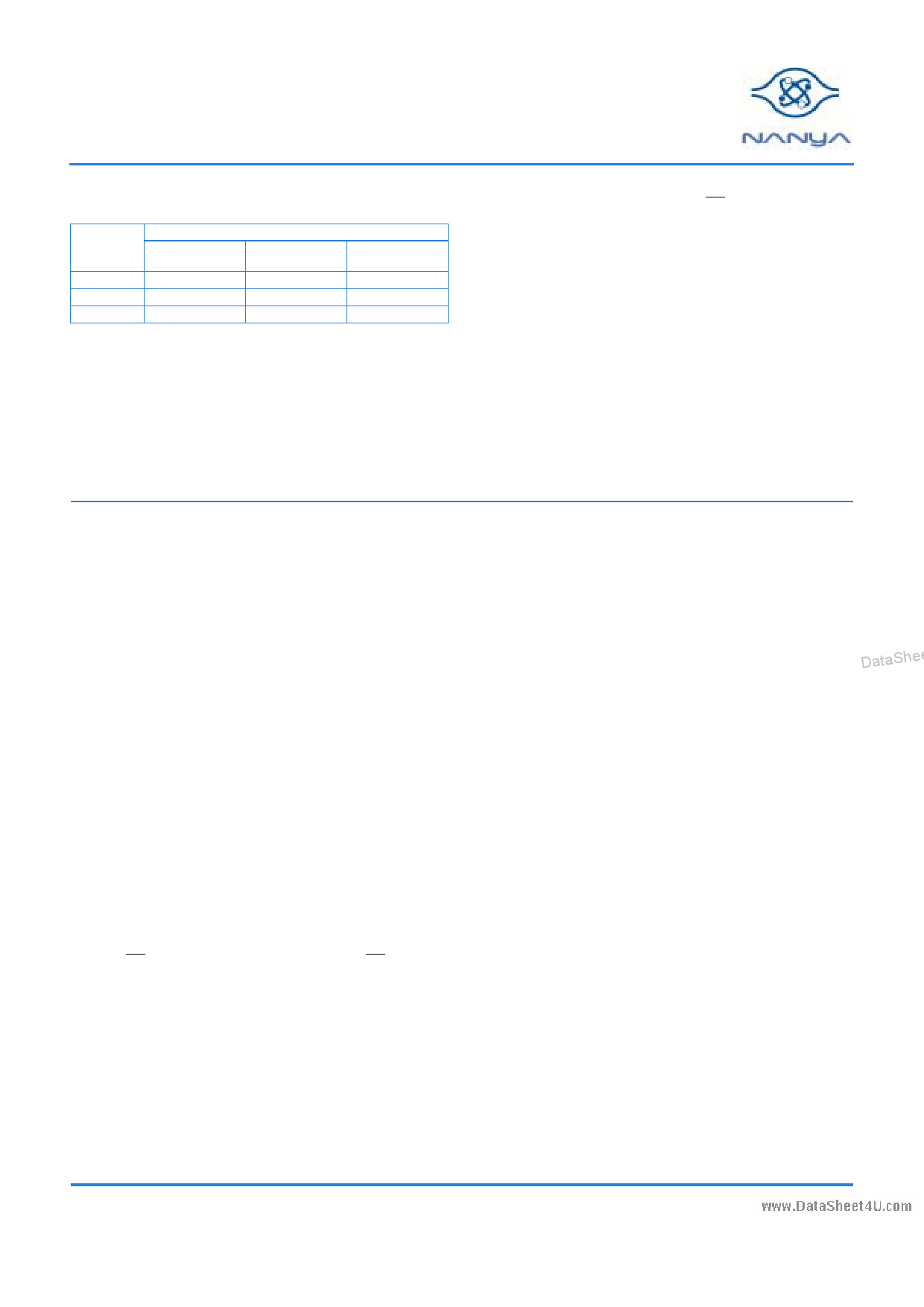

CAS Latency and Frequency

CAS

Latency

Maximum Operating Frequency (MHz)

DDR400

(5T)

DDR333

(6K)

DDR266B

(75B)

2-

133 100

2.5 166 166 133

3 200

-

-

• DDR 512M bit, die B, based on 110nm design rules

• Double data rate architecture: two data transfers per

clock cycle

• Bidirectional data strobe (DQS) is transmitted and

received with data, to be used in capturing data at the

receiver

• DQS is edge-aligned with data for reads and is center-

aligned with data for writes

• Differential clock inputs (CK and CK)

• Four internal banks for concurrent operation

• Data mask (DM) for write data

• DLL aligns DQ and DQS transitions with CK transitions

• Commands entered on each positive CK edge; data and

data mask referenced to both edges of DQS

• Burst lengths: 2, 4, or 8

• CAS Latency: 2 / 2.5 (6K & 75B), 2.5 / 3 (5T)

• Auto Precharge option for each burst access

• Auto Refresh and Self Refresh Modes

• 7.8µs Maximum Average Periodic Refresh Interval

• 2.5V (SSTL_2 compatible) I/O

• VDD = VDDQ = 2.5V ± 0.2V (6K & 75B)

• VDD = VDDQ = 2.6V ± 0.1V (5T)

Description

NT5DS128M4BF, NT5DS128M4BT, NT5DS64M8BF,

accessed. The address bits registered coincident with the

NT5DS64M8BT, NT5DS32M16BF and NT5DS32M16BT are Read or Write command are used to select the bank and the

die B of 512Mb SDRAM devices based using DDR interface. starting column location for the burst access.

They are all based on Nanya’s 110 nm design process.

The DDR SDRAM provides for programmable Read or Write

The 512Mb DDR SDRAM is a high-speed CMOS, dynamic

burst lengths of 2, 4, or 8 locations. An Auto Precharge func-

random-access memory containing 536,870,912

internally configured as a quad-bank DRAM.

bits.DItaistaSheet4tthiUoan.tcmiosmainyitbiaeteednaabt ltehde

to provide a self-timed row

end of the burst access.

precharge

DataShee

The 512Mb DDR SDRAM uses a double-data-rate architec-

ture to achieve high-speed operation. The double data rate

architecture is essentially a 2n prefetch architecture with an

interface designed to transfer two data words per clock cycle

at the I/O pins. A single read or write access for the 512Mb

DDR SDRAM effectively consists of a single 2n-bit wide, one

clock cycle data transfer at the internal DRAM core and two

corresponding n-bit wide, one-half-clock-cycle data transfers

at the I/O pins.

As with standard SDRAMs, the pipelined, multibank architec-

ture of DDR SDRAMs allows for concurrent operation,

thereby providing high effective bandwidth by hiding row pre-

charge and activation time.

An auto refresh mode is provided along with a power-saving

Power Down mode. All inputs are compatible with the JEDEC

Standard for SSTL_2. All outputs are SSTL_2, Class II com-

patible.

A bidirectional data strobe (DQS) is transmitted externally,

along with data, for use in data capture at the receiver. DQS

is a strobe transmitted by the DDR SDRAM during Reads

and by the memory controller during Writes. DQS is edge-

aligned with data for Reads and center-aligned with data for

Writes.

The functionality described and the timing specifications

included in this data sheet are for the DLL Enabled mode of

operation.

The 512Mb DDR SDRAM operates from a differential clock

(CK and CK; the crossing of CK going high and CK going

LOW is referred to as the positive edge of CK). Commands

(address and control signals) are registered at every positive

edge of CK. Input data is registered on both edges of DQS,

and output data is referenced to both edges of DQS, as well

as to both edges of CK.

Read and write accesses to the DDR SDRAM are burst ori-

ented; accesses start at a selected location and continue for

a programmed number of locations in a programmed

sequence. Accesses begin with the registration of an Active

command, which is then followed by a Read or Write com-

mand. The address bits registered coincident with the Active

command are used to select the bank and row to be

DataSheetR4UE.Vco1m.3

15 Feb 2006

1

© NANYA TECHNOLOGY CORP. All rights reserved.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

DataSheet4 U .com

1 page

www.DataSheet4U.com

NT5DS128M4BF / NT5DS128M4BT / NT5DS128M4BG (Green) / NT5DS128M4BS (Green)

NT5DS64M8BF / NT5DS64M8BT/ NT5DS64M8BG (Green) / NT5DS64M8BS (Green)

NT5DS32M16BF / NT5DS32M16BT / NT5DS32M16BG (Green) / NT5DS32M16BS (Green)

512Mb DDR SDRAM

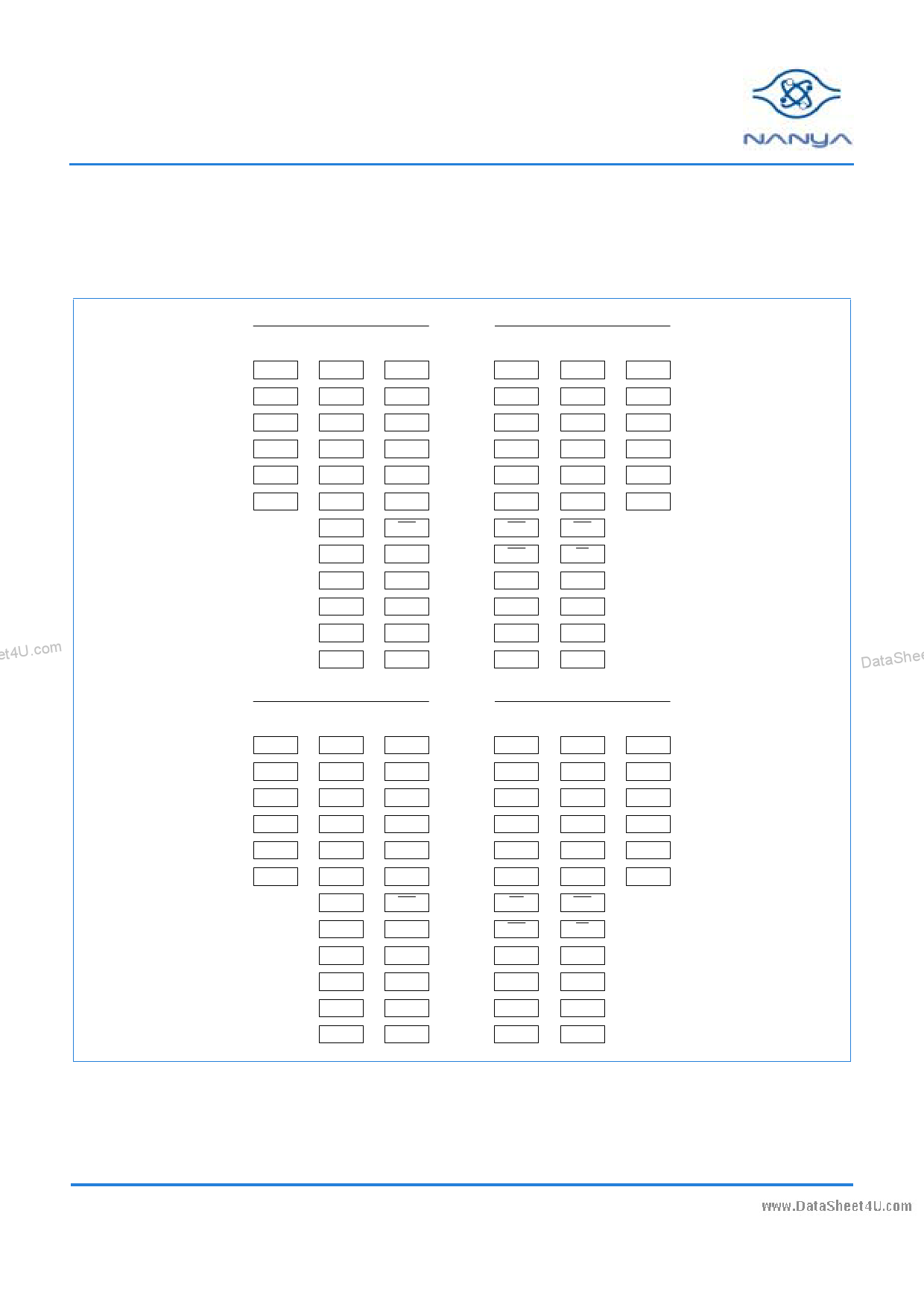

Pin Configuration - 60 balls 0.8mmx1.0mm Pitch CSP Package

<Top View >

See the balls through the package.

et4U.com

1

VSSQ

NC

NC

NC

NC

VREF

2

NC

VCCQ

VSSQ

VDDQ

VSSQ

VSS

CLK

A12

A11

A8

A6

A4

1

VSSQ

NC

NC

NC

NC

VREF

2

DQ7

VDDQ

VSSQ

VDDQ

VSSQ

VSS

CLK

A12

A11

A8

A6

A4

3

VSS

128 X 4

A

7

VDD

DQ3 B DQ0

NC C NC

DQ2 D DQ1

DQS

E

NC

DQM

F

NC

CLK G WE

CKE H RAS

A9 J BA1

A7 K A0

A5 L A2

VDSaS taSheMet4U.coVDmD

3

VSS

DQ6

DQ5

DQ4

DQS

DQM

CLK

CKE

A9

A7

A5

VSS

64 X 8

A

B

C

D

E

F

G

H

J

K

L

M

7

VDD

DQ1

DQ2

DQ3

NC

NC

WE

RAS

BA1

A0

A2

VDD

8

NC

VSSQ

VDDQ

VSSQ

VDDQ

VDD

CAS

CS

BA0

A10/

AP

A1

A3

9

VDDQ

NC

NC

NC

NC

NC

8

DQ0

VSSQ

VDDQ

VSSQ

VDDQ

VDD

CAS

CS

BA0

A10/

AP

A1

A3

9

VDDQ

NC

NC

NC

NC

NC

DataShee

DataSheetR4UE.Vco1m.3

15 Feb 2006

DataSheet4 U .com

5

© NANYA TECHNOLOGY CORP. All rights reserved.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

5 Page

www.DataSheet4U.com

NT5DS128M4BF / NT5DS128M4BT / NT5DS128M4BG (Green) / NT5DS128M4BS (Green)

NT5DS64M8BF / NT5DS64M8BT/ NT5DS64M8BG (Green) / NT5DS64M8BS (Green)

NT5DS32M16BF / NT5DS32M16BT / NT5DS32M16BG (Green) / NT5DS32M16BS (Green)

512Mb DDR SDRAM

Functional Description

The 512Mb DDR SDRAM is a high-speed CMOS, dynamic random-access memory containing 536,870,912 bits. The 512Mb

DDR SDRAM is internally configured as a quad-bank DRAM.

The 512Mb DDR SDRAM uses a double-data-rate architecture to achieve high-speed operation. The double-data-rate architec-

ture is essentially a 2n prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O

pins. A single read or write access for the 512Mb DDR SDRAM consists of a single 2n-bit wide, one clock cycle data transfer at

the internal DRAM core and two corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.

Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a pro-

grammed number of locations in a programmed sequence. Accesses begin with the registration of an Active command, which is

then followed by a Read or Write command. The address bits registered coincident with the Active command are used to select

the bank and row to be accessed (BA0, BA1 select the bank; A0-A12 select the row). The address bits registered coincident

with the Read or Write command are used to select the starting column location for the burst access.

Prior to normal operation, the DDR SDRAM must be initialized. The following sections provide detailed information covering

device initialization, register definition, command descriptions and device operation.

Initialization

Only one of the following two conditions must be met.

• No power sequencing is specified during power up or power down given the following criteria:

VDD and VDDQ are driven from a single power converter output

VTT meets the specification

et4U.com

A minimum resistance of 42 ohms limits the input current from the VTT supply into any pin and

VREF tracks VDDQ /2

DataSheet4U.com

or

• The following relationships must be followed:

VDDQ is driven after or with VDD such that VDDQ < VDD + 0.3V

VTT is driven after or with VDDQ such that VTT < VDDQ + 0.3V

VREF is driven after or with VDDQ such that VREF < VDDQ + 0.3V

DataShee

The DQ and DQS outputs are in the High-Z state, where they remain until driven in normal operation (by a read access). After

all power supply and reference voltages are stable, and the clock is stable, the DDR SDRAM requires a 200µs delay prior to

applying an executable command.

Once the 200µs delay has been satisfied, a Deselect or NOP command should be applied, and CKE must be brought HIGH.

Following the NOP command, a Precharge ALL command must be applied. Next a Mode Register Set command must be

issued for the Extended Mode Register, to enable the DLL, then a Mode Register Set command must be issued for the Mode

Register, to reset the DLL, and to program the operating parameters. 200 clock cycles are required between the DLL reset and

any read command. A Precharge ALL command should be applied, placing the device in the “all banks idle” state

Once in the idle state, two auto refresh cycles must be performed. Additionally, a Mode Register Set command for the Mode

Register, with the reset DLL bit deactivated (i.e. to program operating parameters without resetting the DLL) must be performed.

Following these cycles, the DDR SDRAM is ready for normal operation.

DDR SDRAM’s may be reinitialized at any time during normal operation by asserting a valid MRS command to either the base

or extended mode registers without affecting the contents of the memory array. The contents of either the mode register or

extended mode register can be modified at any valid time during device operation without affecting the state of the internal

address refresh counters used for device refresh.

DataSheetR4UE.Vco1m.3

15 Feb 2006

DataSheet4 U .com

11

© NANYA TECHNOLOGY CORP. All rights reserved.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet NT5DS128M4BT.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NT5DS128M4BF | (NT5DSxxMxBx) 512Mb DDR SDRAM | Nanya Techology |

| NT5DS128M4BG | (NT5DSxxMxBx) 512Mb DDR SDRAM | Nanya Techology |

| NT5DS128M4BS | (NT5DSxxMxBx) 512Mb DDR SDRAM | Nanya Techology |

| NT5DS128M4BT | (NT5DSxxMxBx) 512Mb DDR SDRAM | Nanya Techology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |