|

|

PDF M393T2953BG Data sheet ( Hoja de datos )

| Número de pieza | M393T2953BG | |

| Descripción | (M393Txx5xBG) Registered SDRAM MODULE 240pin Registered Module based | |

| Fabricantes | SAMSUNG | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M393T2953BG (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

512MB, 1GB, 2GB Registered DIMMs

DDR2 SDRAM

DDR2 Registered SDRAM MODULE

240pin Registered Module based on 512Mb B-die

72-bit ECC

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,

AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL

INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar

applications where Product failure couldresult in loss of life or personal or physical harm, or any military or

defense application, or any governmental procurement to which special terms or provisions may apply.

* Samsung Electronics reserves the right to change products or specification without notice.

Rev. 1.3 Aug. 2005

DataSheet4 U .com

1 page

www.DataSheet4U.com

512MB, 1GB, 2GB Registered DIMMs

DDR2 SDRAM

Functional Block Diagram: 512MB, 64Mx72 Module(populated as 1 rank of x8 DDR2 SDRAMs)

M393T6553BG(Z)3 / M393T6553BG(Z)0

RS0

DQS0

DQS0

DM0/DQS9

NC/DQS9

DQS1

DQS1

DM1/DQS10

NC/DQS10

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQS2

DQS2

DM2/DQS11

NC/DQS11

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQS3

DQS3

DM3/DQS12

NC/DQS12

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQS8

DQS8

DM8/DQS17

NC/DQS17

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

S0*

BA0-BA1

A0-A13

RAS

CAS

WE

CKE0

ODT0

RESET

PCK7

PCK7

DM/ NU/ CS DQS DQS

RDQS RDQS

I/O 0

I/O 1 D0

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/ NU/ CS DQS DQS

RDQS RDQS

I/O 0

I/O 1

I/O 2

D1

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/ NU/ CS DQS DQS

RDQS RDQS

I/O 0

I/O 1 D2

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/ NU/ CS DQS DQS

RDQS RDQS

I/O 0

I/O 1 D3

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQS4

DQS4

DM4/DQS13

NC/DQS13

DQS5

DQS5

DM5/DQS14

NC/DQS14

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQS6

DQS6

DM6/DQS15

NC/DQS15

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQS7

DQS7

DM7/DQS16

NC/DQS16

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DM/ NU/ CS DQS DQS

RDQS RDQS

I/O 0

I/O 1 D4

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/ NU/ CS DQS DQS

RDQS RDQS

I/O 0

I/O 1

I/O 2

D5

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/ NU/ CS DQS DQS

RDQS RDQS

I/O 0

I/O 1 D6

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/ NU/ CS DQS DQS

RDQS RDQS

I/O 0

I/O 1 D7

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

Serial PD

VDDSPD

Serial PD

SCL

SDA

VDD/VDDQ

D0 - D8

DM/ NU/ CS DQS DQS

RDQS RDQS

I/O 0

I/O 1 D8

I/O 2

I/O 3

WP A0 A1 A2

SA0 SA1 SA2

VREF

VSS

D0 - D8

D0 - D8

I/O 4

I/O 5

I/O 6

I/O 7

CK0

PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D8

P

CK0

L

L

PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D8

RESET

OE

PCK7 -> CK : Register

PCK7 -> CK : Register

1:1

R RSO-> CS : DDR2 SDRAMs D0-D8

E RBA0-RBA1 -> BA0-BA1 : DDR2 SDRAMs D0-D8

G

I

S

T

RA0-RA13 -> A0-A13 : DDR2 SDRAMs D0-D8

RRAS -> RAS : DDR2 SDRAMs D0-D8

RCAS -> CAS : DDR2 SDRAMs D0-D8

RWE -> WE : DDR2 SDRAMs D0-D8

Notes :

1. DQ-to-I/O wiring may be changed within a byte.

2. DQ/DQS/DM/CKE/S relationships must be maintained as shown.

E RCKE0 -> CKE : DDR2 SDRAMs D0-D8

3. Unless otherwise noted, resister values are 22 Ohms

R RODT0 -> ODT0 : DDR2 SDRAMs D0-D8

RST * S0 connects to DCS and VDD connects to CSR on the register.

DataSheet4 U .com

Rev. 1.3 Aug. 2005

5 Page

www.DataSheet4U.com

512MB, 1GB, 2GB Registered DIMMs

DDR2 SDRAM

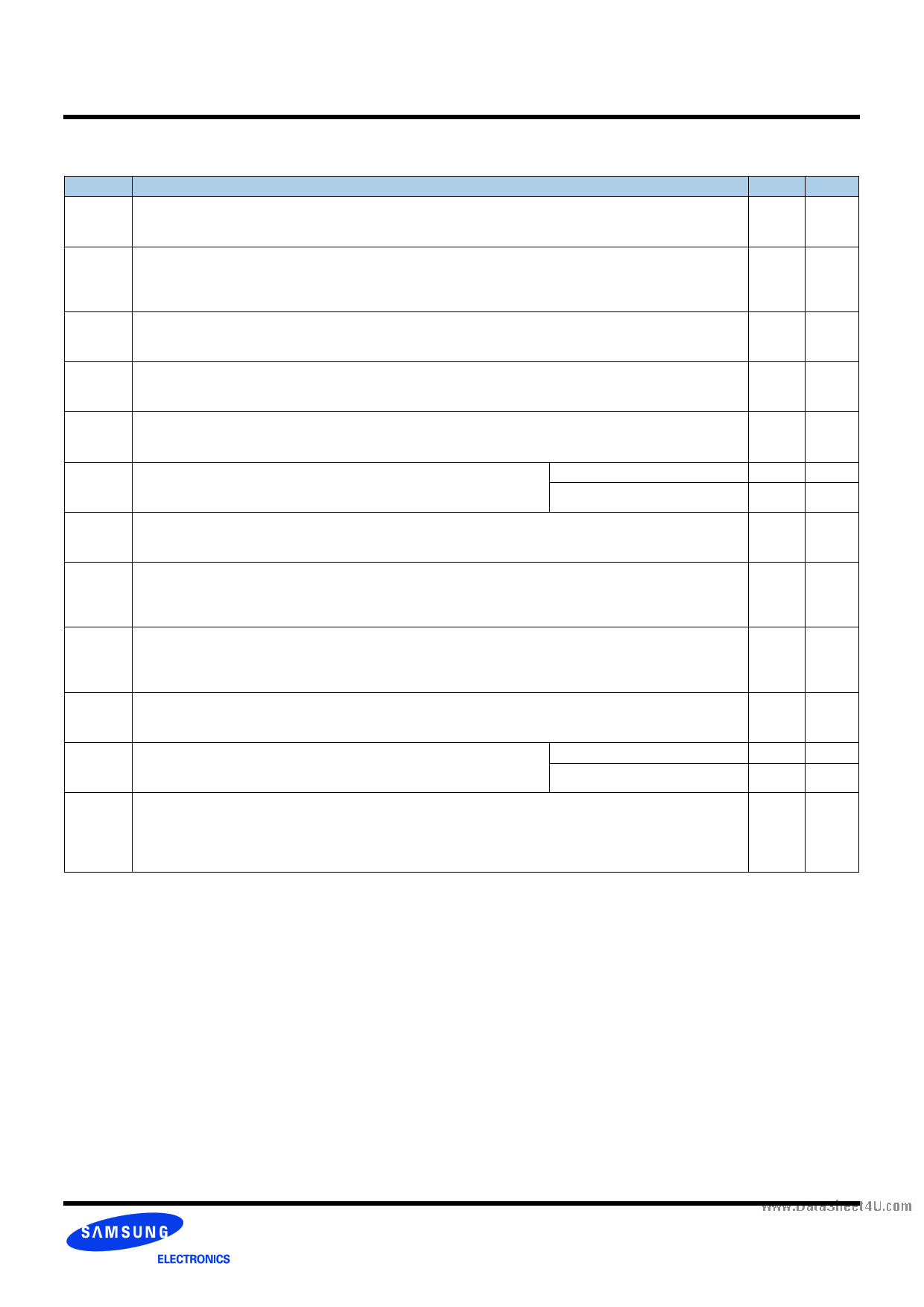

IDD Specification Parameters Definition

(IDD values are for full operating range of Voltage and Temperature)

Symbol

IDD0

IDD1

IDD2P

IDD2Q

IDD2N

IDD3P

IDD3N

IDD4W

IDD4R

IDD5B

IDD6

IDD7

Proposed Conditions

Operating one bank active-precharge current;

tCK = tCK(IDD), tRC = tRC(IDD), tRAS = tRASmin(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Ad-

dress bus inputs are SWITCHING; Data bus inputs are SWITCHING

Operating one bank active-read-precharge current;

IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRC = tRC (IDD), tRAS = tRASmin(IDD), tRCD =

tRCD(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data pattern

is same as IDD4W

Precharge power-down current;

All banks idle; tCK = tCK(IDD); CKE is LOW; Other control and address bus inputs are STABLE; Data bus inputs are

FLOATING

Precharge quiet standby current;

All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are STABLE; Data

bus inputs are FLOATING

Precharge standby current;

All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are SWITCHING;

Data bus inputs are SWITCHING

Active power-down current;

All banks open; tCK = tCK(IDD); CKE is LOW; Other control and address bus

inputs are STABLE; Data bus inputs are FLOATING

Fast PDN Exit MRS(12) = 0mA

Slow PDN Exit MRS(12) = 1mA

Active standby current;

All banks open; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid

commands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING

Operating burst write current;

All banks open, Continuous burst writes; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP

= tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data bus in-

puts are SWITCHING

Operating burst read current;

All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRAS-

max(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING;

Data pattern is same as IDD4W

Burst auto refresh current;

tCK = tCK(IDD); Refresh command at every tRFC(IDD) interval; CKE is HIGH, CS\ is HIGH between valid commands;

Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING

Self refresh current;

CK and CK\ at 0V; CKE ≤ 0.2V; Other control and address bus inputs are

FLOATING; Data bus inputs are FLOATING

Normal

Low Power

Operating bank interleave read current;

All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = tRCD(IDD)-1*tCK(IDD); tCK = tCK(IDD), tRC =

tRC(IDD), tRRD = tRRD(IDD), tFAW = tFAW(IDD), tRCD = 1*tCK(IDD); CKE is HIGH, CS\ is HIGH between valid com-

mands; Address bus inputs are STABLE during DESELECTs; Data pattern is same as IDD4R; Refer to the following

page for detailed timing conditions

Units

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

Notes

DataSheet4 U .com

Rev. 1.3 Aug. 2005

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet M393T2953BG.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M393T2953BG | (M393Txx5xBG) Registered SDRAM MODULE 240pin Registered Module based | SAMSUNG |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |