|

|

PDF TZA3046 Data sheet ( Hoja de datos )

| Número de pieza | TZA3046 | |

| Descripción | Fiber Channel / Gigabit Ethernet Transimpedance Amplifier | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TZA3046 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

TZA3046

Fiber Channel/Gigabit Ethernet transimpedance amplifier

Rev. 01 — 19 May 2006

Product data sheet

1. General description

The TZA3046 is a transimpedance amplifier with Automatic Gain Control (AGC), designed

to be used in Fiber Channel/Gigabit Ethernet (FC/GE) fiber optic links. It amplifies the

current generated by a photo detector (PIN diode or avalanche photodiode) and converts

it to a differential output voltage. It offers a current mirror of average photo current for

RSSI monitoring to be used in SFF-8472 compliant modules.

The low noise characteristics makes it suitable for FC/GE applications, but also for

FTTx applications.

CAUTION

This device is sensitive to ElectroStatic Discharge (ESD). Therefore care should be taken

during transport and handling.

2. Features

I Low equivalent input noise current, typically 126 nA (RMS)

I Wide dynamic range, typically 2.5 µA to 1.7 mA (p-p)

I Differential transimpedance of 7.5 kΩ (typical)

I Bandwidth from DC to 1050 MHz (typical)

I Differential outputs

I On-chip AGC with possibility of external control

I Single supply voltage 3.3 V, range 2.97 V to 3.6 V

I Bias voltage for PIN diode

I On-chip current mirror of average photo current for RSSI monitoring

I Identical ports available on both sides of die for easy bond layout and RF polarity

selection

3. Applications

I Digital fiber optic receiver modules in telecommunications transmission systems, in

high-speed data networks or in FTTx systems.

DataSheet4 U .com

1 page

www.DataSheet4U.com

Philips Semiconductors

TZA3046

Fiber Channel/Gigabit Ethernet transimpedance amplifier

The parasitic capacitance can be minimized through:

1. Reducing the capacitance of the PIN diode. This is achieved by proper choice of PIN

diode and typically a high reverse voltage.

2. Reducing the parasitics around the input pad. This is achieved by placing the PIN

diode as close as possible to the TIA.

The PIN diode can be biased with a positive or a negative voltage. Figure 3 shows the PIN

diode biased positively, using the on-chip bias pad DREF. The voltage at DREF is derived

from VCC by a low-pass filter comprising internal resistor RDREF and external capacitor C2

which decouples any supply voltage noise. The value of external capacitor C2 affects the

value of PSRR and should have a minimum value of 470 pF. Increasing this value

improves the value of PSRR. The current through RDREF is measured and sourced at pad

IDREF_MON, see Section 7.3.

If the biasing for the PIN diode is done external to the IC, pad DREF can be left

unconnected. If a negative bias voltage is used, the configuration shown in Figure 4 can

be used. In this configuration, the direction of the signal current is reversed to that shown

in Figure 3. It is essential that in these applications, the PIN diode bias voltage is filtered to

achieve the best sensitivity.

For maximum freedom on bonding location, 2 outputs are available for DREF (pads 1

and 3). These are internally connected. Both outputs can be used if necessary. If only one

is used, the other can be left open.

C2

470 pF

VCC

DREF 1 or 3 RDREF

IPIN

290 Ω

4 or 17

IPHOTO 2

TZA3046

001aae513

Fig 3. The PIN diode connected between

the input and pad DREF

VCC

DREF 1 or 3 RDREF

290 Ω

4 or 17

IPHOTO 2

IPIN

negative

bias voltage

TZA3046

001aae514

Fig 4. The PIN diode connected between

the input and a negative supply

voltage

TZA3046_1

Product data sheet

DataSheet4 U .com

Rev. 01 — 19 May 2006

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

5 of 15

5 Page

xxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx x xxxxxxxxxxxxxx xxxxxxxxxx xxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxx

xxxxx xxxxxx xx xxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxx xxxxxxx xxxxxxxxxxxxxxxxxxx

xxxxxxxxxxxxxxxx xxxxxxxxxxxxxx xxxxxx xx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxx xxxxx x x

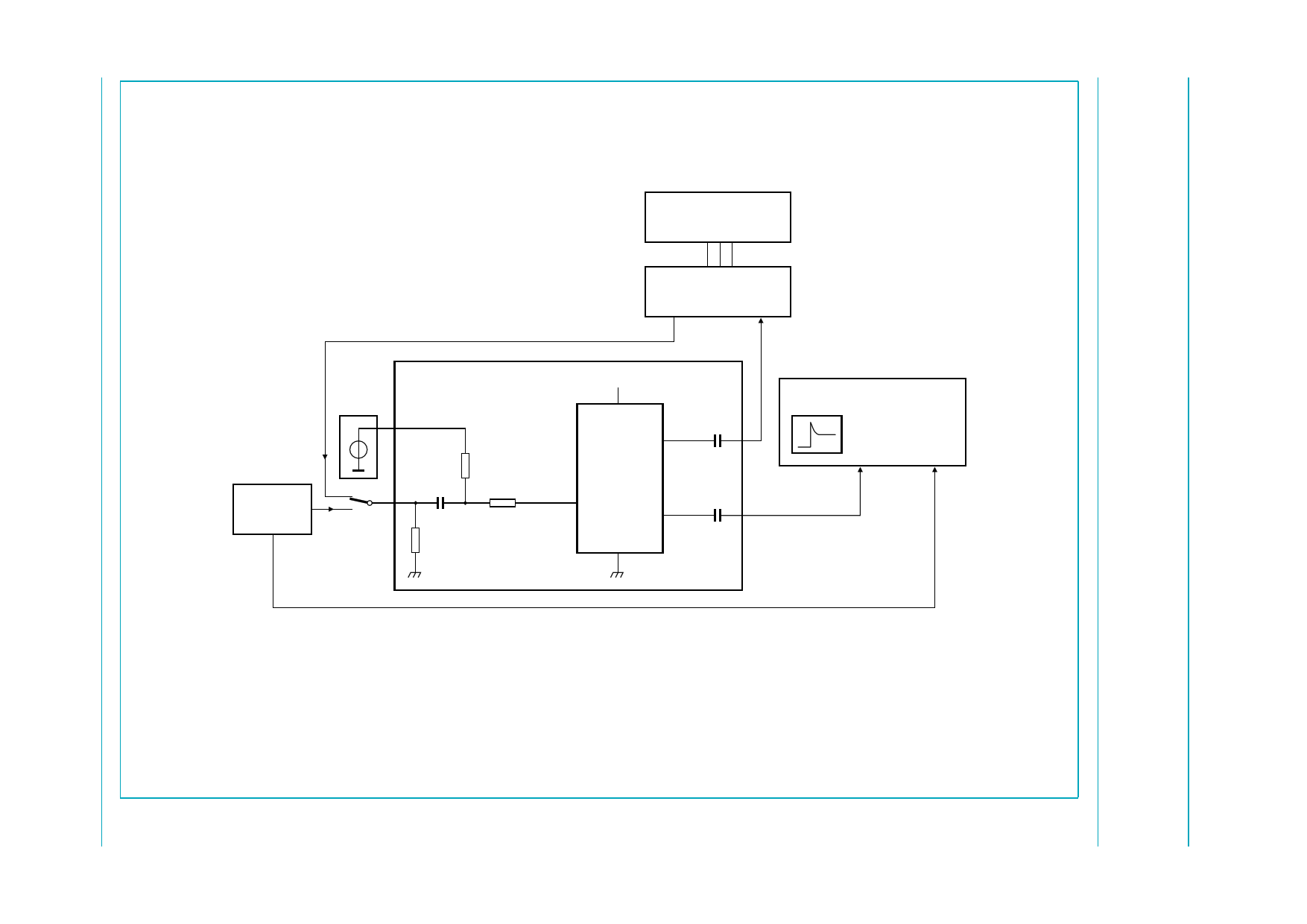

NETWORK ANALYZER

DC-IN

PATTERN

GENERATOR DATA

CLOCK

S-PARAMETER TEST SET

PORT1

PORT2

Zo = 50 Ω

Zo= 50 Ω

VCC

22 nF

55 Ω

8.2

kΩ

330 Ω

R

4 or 17

8 or 14 OUT

22 nF

TZA3046

IPHOTO

2

OUTQ 22 nF

7 or 13

9, 10, 11, 12

GND

SAMPLING OSCILLOSCOPE

12

Zo = 50 Ω

TRIGGER

INPUT

001aae519

Total impedance of the test circuit (Ztot(tc)) is calculated by the equation Ztot(tc) = s21 × (R + Zi) × 2, where s21 is the insertion loss of ports 1 and 2.

Typical values: R = 330 Ω, Zi = 30 Ω.

Fig 9. Test circuit

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet TZA3046.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TZA3041 | Gigabit Ethernet/Fibre Channel laser drivers | NXP Semiconductors |

| TZA3041AHL | Gigabit Ethernet/Fibre Channel laser drivers | NXP Semiconductors |

| TZA3041BHL | Gigabit Ethernet/Fibre Channel laser drivers | NXP Semiconductors |

| TZA3041U | Gigabit Ethernet/Fibre Channel laser drivers | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |