|

|

PDF AT26DF081A Data sheet ( Hoja de datos )

| Número de pieza | AT26DF081A | |

| Descripción | 8-megabit 2.7-volt Minimum SPI Serial Flash Memory | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT26DF081A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Features

• Single 2.7V - 3.6V Supply

• Serial Peripheral Interface (SPI) Compatible

– Supports SPI Modes 0 and 3

• 70 MHz Maximum Clock Frequency

• Flexible, Uniform Erase Architecture

– 4-Kbyte Blocks

– 32-Kbyte Blocks

– 64-Kbyte Blocks

– Full Chip Erase

• Individual Sector Protection with Global Protect/Unprotect Feature

– One 32-Kbyte Top Boot Sector

– Two 8-Kbyte Sectors

– One 16-Kbyte Sector

– Fifteen 64-Kbyte Sectors

• Hardware Controlled Locking of Protected Sectors

• Flexible Programming Options

– Byte/Page Program (1 to 256 Bytes)

– Sequential Program Mode Capability

• Automatic Checking and Reporting of Erase/Program Failures

• JEDEC Standard Manufacturer and Device ID Read Methodology

• Low Power Dissipation

– 5 mA Active Read Current (Typical)

– 25 µA Deep Power-down Current (Typical)

• Endurance: 100,000 Program/Erase Cycles

• Data Retention: 20 Years

• Complies with Full Industrial Temperature Range

• Industry Standard Green (Pb/Halide-free/RoHS Compliant) Package Options

– 8-lead SOIC (150-mil and 200-mil wide)

8-megabit

2.7-volt

Minimum

SPI Serial Flash

Memory

AT26DF081A

1. Description

The AT26DF081A is a serial interface Flash memory device designed for use in a

wide variety of high-volume consumer-based applications in which program code is

shadowed from Flash memory into embedded or external RAM for execution. The

flexible erase architecture of the AT26DF081A, with its eras\e granularity as small as

4 Kbytes, makes it ideal for data storage as well, eliminating the need for additional

data storage EEPROM devices.

The physical sectoring and the erase block sizes of the AT26DF081A have been opti-

mized to meet the needs of today’s code and data storage applications. By optimizing

the size of the physical sectors and erase blocks, the memory space can be used

much more efficiently. Because certain code modules and data storage segments

must reside by themselves in their own protected sectors, the wasted and unused

memory space that occurs with large sectored and large block erase Flash memory

devices can be greatly reduced. This increased memory space efficiency allows addi-

tional code routines and data storage segments to be added while still maintaining the

same overall device density.

3600G–DFLASH–06/09

1 page

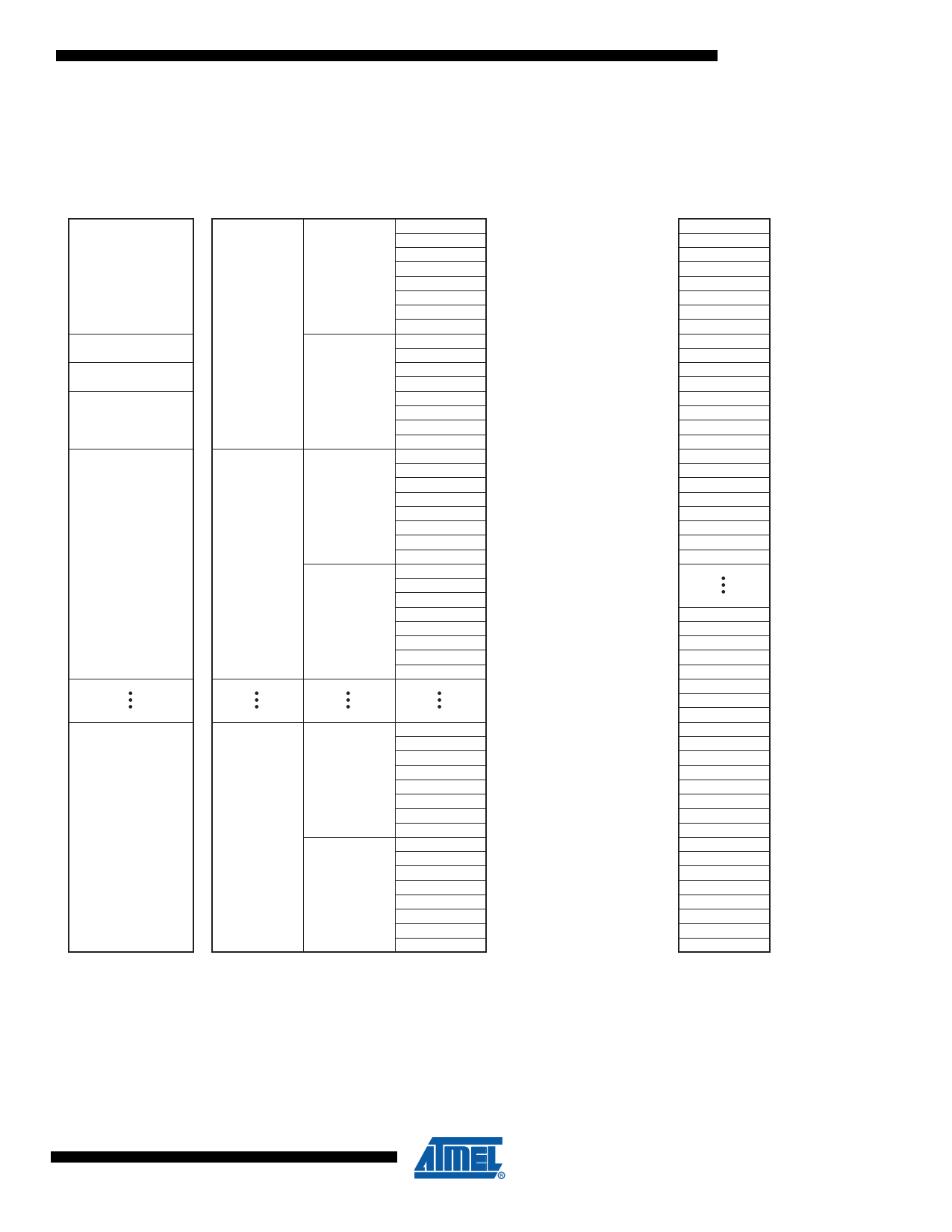

Figure 4-1. Memory Architecture Diagram

Block Erase Detail

Internal Sectoring for

Sector Protection

Function

32KB

(Sector 18)

8KB

(Sector 17)

8KB

(Sector 16)

16KB

(Sector 15)

64KB

(Sector 14)

64KB

32KB

4KB

Block Erase

Block Erase

Block Erase

(D8h Command) (52h Command) (20h Command)

Block Address

Range

64KB

32KB

32KB

64KB

32KB

32KB

4KB 0FFFFFh – 0FF000h

4KB 0FEFFFh – 0FE000h

4KB 0FDFFFh – 0FD000h

4KB 0FCFFFh – 0FC000h

4KB 0FBFFFh – 0FB000h

4KB 0FAFFFh – 0FA000h

4KB 0F9FFFh – 0F9000h

4KB 0F8FFFh – 0F8000h

4KB 0F7FFFh – 0F7000h

4KB 0F6FFFh – 0F6000h

4KB 0F5FFFh – 0F5000h

4KB 0F4FFFh – 0F4000h

4KB 0F3FFFh – 0F3000h

4KB 0F2FFFh – 0F2000h

4KB 0F1FFFh – 0F1000h

4KB 0F0FFFh – 0F0000h

4KB 0EFFFFh – 0EF000h

4KB 0EEFFFh – 0EE000h

4KB 0EDFFFh – 0ED000h

4KB 0ECFFFh – 0EC000h

4KB 0EBFFFh – 0EB000h

4KB 0EAFFFh – 0EA000h

4KB 0E9FFFh – 0E9000h

4KB 0E8FFFh – 0E8000h

4KB 0E7FFFh – 0E7000h

4KB 0E6FFFh – 0E6000h

4KB 0E5FFFh – 0E5000h

4KB 0E4FFFh – 0E4000h

4KB 0E3FFFh – 0E3000h

4KB 0E2FFFh – 0E2000h

4KB 0E1FFFh – 0E1000h

4KB 0E0FFFh – 0E0000h

64KB

(Sector 0)

64KB

32KB

32KB

4KB 00FFFFh – 00F000h

4KB 00EFFFh – 00E000h

4KB 00DFFFh – 00D000h

4KB 00CFFFh – 00C000h

4KB 00BFFFh – 00B000h

4KB 00AFFFh – 00A000h

4KB 009FFFh – 009000h

4KB 008FFFh – 008000h

4KB 007FFFh – 007000h

4KB 006FFFh – 006000h

4KB 005FFFh – 005000h

4KB 004FFFh – 004000h

4KB 003FFFh – 003000h

4KB 002FFFh – 002000h

4KB 001FFFh – 001000h

4KB 000FFFh – 000000h

AT26DF081A

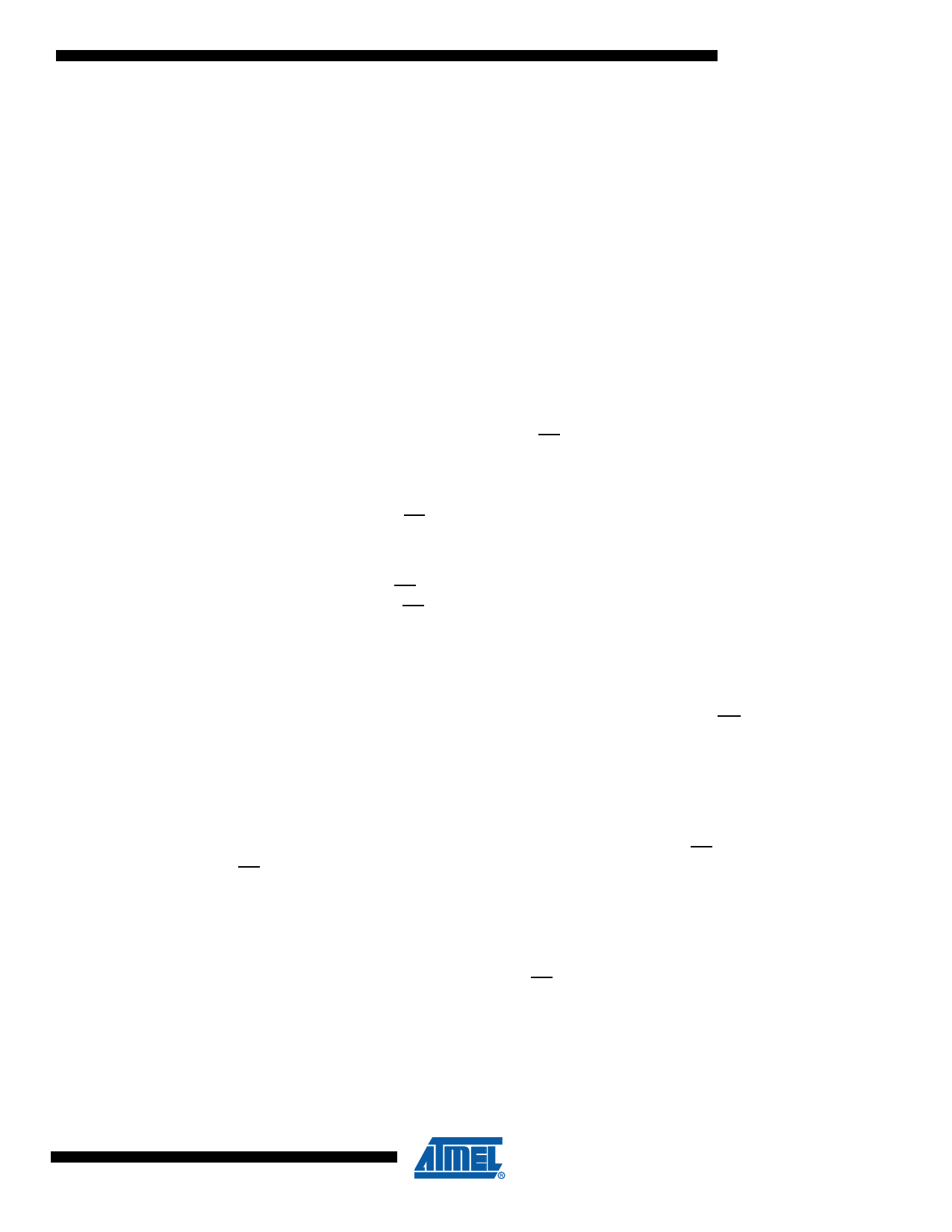

Page Program Detail

1-256 Byte

Page Program

(02h Command)

Page Address

Range

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

0FFFFFh – 0FFF00h

0FFEFFh – 0FFE00h

0FFDFFh – 0FFD00h

0FFCFFh – 0FFC00h

0FFBFFh – 0FFB00h

0FFAFFh – 0FFA00h

0FF9FFh – 0FF900h

0FF8FFh – 0FF800h

0FF7FFh – 0FF700h

0FF6FFh – 0FF600h

0FF5FFh – 0FF500h

0FF4FFh – 0FF400h

0FF3FFh – 0FF300h

0FF2FFh – 0FF200h

0FF1FFh – 0FF100h

0FF0FFh – 0FF000h

0FEFFFh – 0FEF00h

0FEEFFh – 0FEE00h

0FEDFFh – 0FED00h

0FECFFh – 0FEC00h

0FEBFFh – 0FEB00h

0FEAFFh – 0FEA00h

0FE9FFh – 0FE900h

0FE8FFh – 0FE800h

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

256 Bytes

0017FFh – 001700h

0016FFh – 001600h

0015FFh – 001500h

0014FFh – 001400h

0013FFh – 001300h

0012FFh – 001200h

0011FFh – 001100h

0010FFh – 001000h

000FFFh – 000F00h

000EFFh – 000E00h

000DFFh – 000D00h

000CFFh – 000C00h

000BFFh – 000B00h

000AFFh – 000A00h

0009FFh – 000900h

0008FFh – 000800h

0007FFh – 000700h

0006FFh – 000600h

0005FFh – 000500h

0004FFh – 000400h

0003FFh – 000300h

0002FFh – 000200h

0001FFh – 000100h

0000FFh – 000000h

3600G–DFLASH–06/09

5

5 Page

AT26DF081A

8.2 Sequential Program Mode

The Sequential Program Mode improves throughput over the Byte/Page Program command

when the Byte/Page Program command is used to program single bytes only into consecutive

address locations. For example, some systems may be designed to program only a single byte

of information at a time and cannot utilize a buffered Page Program operation due to design

restrictions. In such a case, the system would normally have to perform multiple Byte Program

operations in order to program data into sequential memory locations. This approach can add

considerable system overhead and SPI bus traffic.

The Sequential Programming Mode helps reduce system overhead and bus traffic by incorporat-

ing an internal address counter that keeps track of the byte location to program, thereby

eliminating the need to supply an address sequence to the device for every byte to program.

When using the Sequential Program mode, all address locations to be programmed must be in

the erased state. Before the Sequential Program mode can first be entered, the Write Enable

command must have been previously issued to the device to set the WEL bit of the Status Reg-

ister to a logical “1” state.

To start the Sequential Program Mode, the CS pin must first be asserted, and either an opcode

of ADh or AFh must be clocked into the device. For the first program cycle, three address bytes

must be clocked in after the opcode to designate the first byte location to program. After the

address bytes have been clocked in, the byte of data to be programmed can be sent to the

device. Deasserting the CS pin will start the internally self-timed program operation, and the byte

of data will be programmed into the memory location specified by A23 - A0.

After the first byte has been successfully programmed, a second byte can be programmed by

simply reasserting the CS pin, clocking in the ADh or AFh opcode, and then clocking in the next

byte of data. When the CS pin is deasserted, the second byte of data will be programmed into

the next sequential memory location. The process would be repeated for any additional bytes.

There is no need to reissue the Write Enable command once the Sequential Program Mode has

been entered.

When the last desired byte has been programmed into the memory array, the Sequential

Program Mode operation can be terminated by reasserting the CS pin and sending the

Write Disable command to the device to reset the WEL bit in the Status Register back to the

logical “0” state.

If more than one byte of data is ever clocked in during each program cycle, then only the last

byte of data sent on the SI pin will be stored in the internal latches. The programming of each

byte is internally self-timed and should take place in a time of tBP. For each program cycle, a

complete byte of data must be clocked into the device before the CS pin is deasserted, and the

CS pin must be deasserted on even byte boundaries (multiples of eight bits); otherwise, the

device will abort the operation, the byte of data will not be programmed into the memory array,

and the WEL bit in the Status Register will be reset back to the logical “0” state.

If the address initially specified by A23 - A0 points to a memory location within a sector that is in

the protected state, then the Sequential Program Mode command will not be executed, and the

device will return to the idle state once the CS pin has been deasserted. The WEL bit in the Sta-

tus Register will also be reset back to the logical “0” state.

There is no address wrapping when using the Sequential Program Mode. Therefore, when the

last byte (0FFFFFh) of the memory array has been programmed, the device will automatically

exit the Sequential Program mode and reset the WEL bit in the Status Register back to the logi-

cal “0” state. In addition, the Sequential Program mode will not automatically skip over protected

3600G–DFLASH–06/09

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT26DF081A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT26DF081A | 8-megabit 2.7-volt Minimum SPI Serial Flash Memory | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |