|

|

PDF AT26F004 Data sheet ( Hoja de datos )

| Número de pieza | AT26F004 | |

| Descripción | Serial Firmware DataFlash Memory | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT26F004 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Features

• Single 2.7V - 3.6V Supply

• Serial Peripheral Interface (SPI) Compatible

– Supports SPI Modes 0 and 3

• 33 MHz Maximum Clock Frequency

• Flexible, Uniform Erase Architecture

– 4-Kbyte Blocks

– 32-Kbyte Blocks

– 64-Kbyte Blocks

– Full Chip Erase

• Optimized Physical Sectoring for Code Shadowing and Code + Data Storage

Applications

– One 16-Kbyte Top Boot Sector

– Two 8-Kbyte Sectors

– One 32-Kbyte Sector

– Seven 64-Kbyte Sectors

• Individual Sector Protection for Program/Erase Protection

• Hardware Controlled Locking of Protected Sectors

• Byte Program Architecture with Sequential Byte Program Mode Capability

– Sequential Byte Program Mode Improves Throughput for

Programming Multiple Bytes

• JEDEC Standard Manufacturer and Device ID Read Methodology

• Low Power Dissipation

– 7 mA Active Read Current (Typical)

– 15 µA Deep Power-down Current (Typical)

• Endurance: 100,000 Program/Erase Cycles

• Data Retention: 20 Years

• Complies with Full Industrial Temperature Range

• Industry Standard Green (Pb/Halide-free/RoHS Compliant) Package Options

– 8-lead SOIC

– 8-lead MLF

4-megabit

2.7-volt Only

Serial Firmware

DataFlash®

Memory

AT26F004

1. Description

The AT26F004 is a serial interface Flash memory device designed for use in a wide

variety of high-volume consumer based applications in which program code is shad-

owed from Flash memory into embedded or external RAM for execution. The flexible

erase architecture of the AT26F004, with its erase granularity as small as 4 Kbytes,

makes it ideal for data storage as well, eliminating the need for additional data storage

EEPROM devices.

The physical sectoring and the erase block sizes of the AT26F004 have been opti-

mized to meet the needs of today's code and data storage applications. By optimizing

the size of the physical sectors and erase blocks, the memory space can be used

much more efficiently. Because certain code modules and data storage segments

must reside by themselves in their own protected sectors, the wasted and unused

memory space that occurs with large sectored and large block erase Flash memory

devices can be greatly reduced. This increased memory space efficiency allows addi-

tional code routines and data storage segments to be added while still maintaining the

same overall device density.

3588A–DFLSH–10/05

1 page

AT26F004

5. Device Operation

The AT26F004 is controlled by a set of instructions that are sent from a host controller, com-

monly referred to as the SPI Master. The SPI Master communicates with the AT26F004 via the

SPI bus which is comprised of four signal lines: Chip Select (CS), Serial Clock (SCK), Serial

Input (SI), and Serial Output (SO).

The SPI protocol defines a total of four modes of operation (mode 0, 1, 2, or 3) with each mode

differing in respect to the SCK polarity and phase and how the polarity and phase control the

flow of data on the SPI bus. The AT26F004 supports the two most common modes, SPI modes

0 and 3. The only difference between SPI modes 0 and 3 is the polarity of the SCK signal when

in the inactive state (when the SPI Master is in standby mode and not transferring any data).

With SPI modes 0 and 3, data is always latched in on the rising edge of SCK and always output

on the falling edge of SCK.

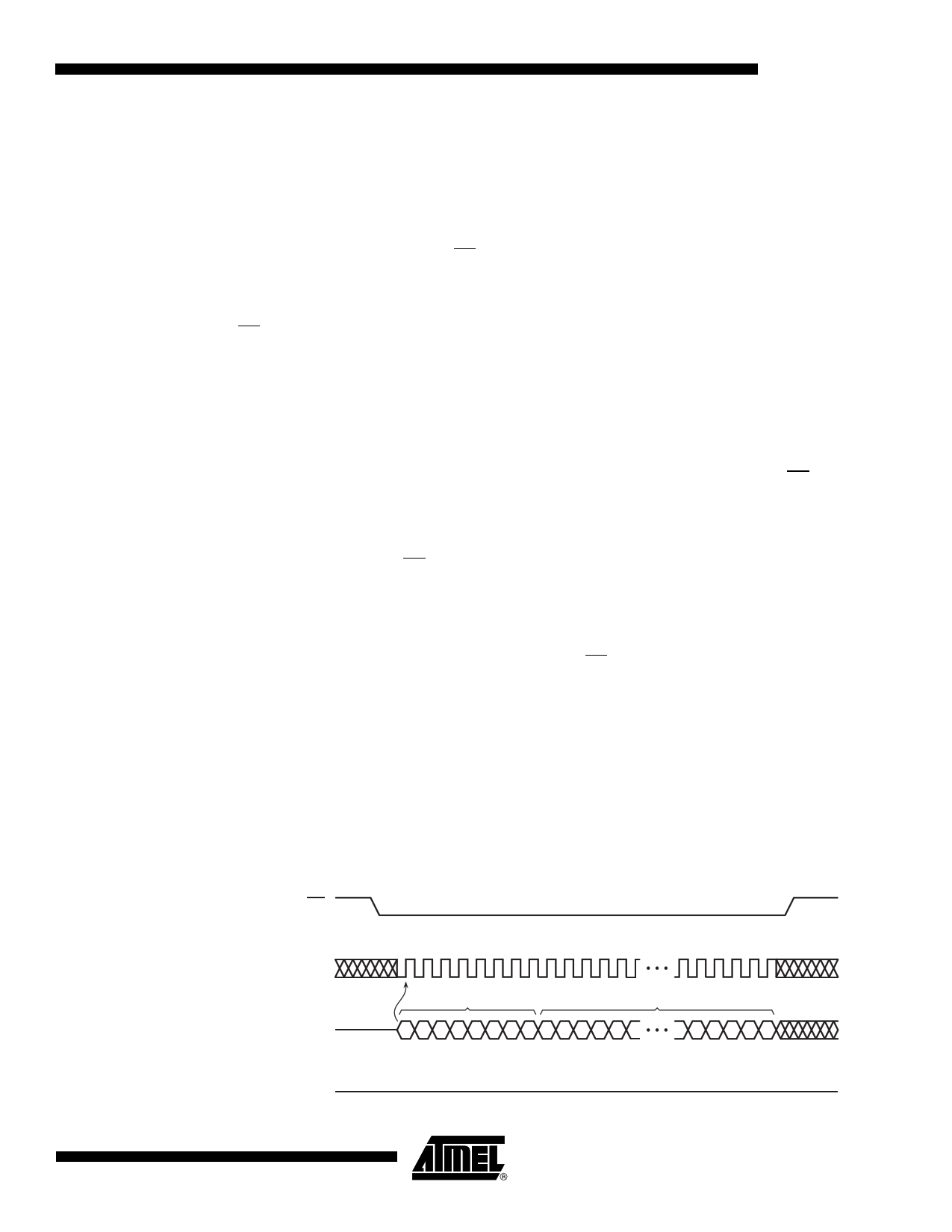

Figure 5-1. SPI Mode 0 and 3

CS

SCK

SI MSB

LSB

SO

MSB

LSB

6. Commands and Addressing

A valid instruction or operation must always be started by first asserting the CS pin. After the CS

pin has been asserted, the SPI Master must then clock out a valid 8-bit opcode on the SPI bus.

Following the opcode, instruction dependent information such as address and data bytes would

then be clocked out by the SPI Master. All opcode, address, and data bytes are transferred with

the most significant bit (MSB) first. An operation is ended by deasserting the CS pin.

Opcodes not supported by the AT26F004 will be ignored by the device and no operation will be

started. The device will continue to ignore any data presented on the SI pin until the start of the

next operation (CS pin being deasserted and then reasserted). In addition, if the CS pin is deas-

serted before all eight bits of an opcode are sent to the device, then the device will simply return

to the idle state and wait for the next operation.

Addressing of the device requires a total of three bytes of information to be sent, representing

address bits A23 - A0. Since the upper address limit of the AT26F004 memory array is

07FFFFh, address bits A23 - A19 are always ignored by the device.

3588A–DFLSH–10/05

5

5 Page

AT26F004

8.3 Block Erase

A block of 4 Kbytes, 32 Kbytes, or 64 Kbytes can be erased (all bits set to the logical “1” state) in

a single operation by using one of three different opcodes for the Block Erase command. An

opcode of 20h is used for a 4-Kbyte erase, an opcode of 52h is used for a 32-Kbyte erase, and

an opcode of D8h is used for a 64-Kbyte erase. Before a Block Erase command can be started,

the Write Enable command must have been previously issued to the device to set the WEL bit of

the Status Register to a logical “1” state.

To perform a Block Erase, the CS pin must first be asserted and the appropriate opcode (20h,

52h or D8h) must be clocked into the device. After the opcode has been clocked in, the three

address bytes specifying an address within the 4-Kbyte, 32-Kbyte, or 64-Kbyte block to be

erased must be clocked in. Any additional data clocked into the device will be ignored. When the

CS pin is deasserted, the device will erase the appropriate block. The erasing of the block is

internally self-timed and should take place in a time of tBLKE.

Since the Block Erase command erases a region of bytes, the lower order address bits do not

need to be decoded by the device. Therefore, for a 4-Kbyte erase, address bits A11 - A0 will be

ignored by the device and their values can be either a logical “1” or “0”. For a 32-Kbyte erase,

address bits A14 - A0 will be ignored, and for a 64-Kbyte erase, address bits A15 - A0 will be

ignored by the device. Despite the lower order address bits not being decoded by the device, the

complete three address bytes must still be clocked into the device before the CS pin is deas-

serted; otherwise, the device will abort the operation and no erase operation will be performed.

If the address specified by A23 - A0 points to a memory location within a sector that is in the pro-

tected state, then the Block Erase command will not be executed, and the device will return to

the idle state once the CS pin has been deasserted. In addition, with the larger Block Erase

sizes of 32 Kbytes and 64 Kbytes, more than one physical sector may be erased (e.g. sectors

10, 9 and 8) at one time. Therefore, in order to erase a larger block that may span more than one

sector, all of the sectors in the span must be in the unprotected state. If one of the physical sec-

tors within the span is in the protected state, then the device will ignore the Block Erase

command and will return to the idle state once the CS pin is deasserted.

The WEL bit in the Status Register will be reset back to the logical “0” state if the erase cycle

aborts due to an incomplete address being sent or because a memory location within the region

to be erased is protected.

While the device is executing a successful erase cycle, the Status Register can be read and will

indicate that the device is busy. For faster throughput, it is recommended that the Status Regis-

ter be polled rather than waiting the tBLKE time to determine if the device has finished erasing. At

some point before the erase cycle completes, the WEL bit in the Status Register will be reset

back to the logical “0” state.

Figure 8-4. Block Erase

CS

SCK

SI

SO

0 1 2 3 4 5 6 7 8 9 10 11 12

26 27 28 29 30 31

OPCODE

ADDRESS BITS A23-A0

CCCCCCCCAAAAAA

MSB

MSB

AAAAAA

HIGH-IMPEDANCE

3588A–DFLSH–10/05

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT26F004.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT26F004 | Serial Firmware DataFlash Memory | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |