|

|

PDF ZL50015 Data sheet ( Hoja de datos )

| Número de pieza | ZL50015 | |

| Descripción | Enhanced 1 K Digital Switch | |

| Fabricantes | Zarlink Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ZL50015 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

ZL50015

Enhanced 1 K Digital Switch with

Stratum 4E DPLL

Data Sheet

Features

• 1024 channel x 1024 channel non-blocking digital

Time Division Multiplex (TDM) switch at 4.096,

8.192 and 16.384 Mbps or using a combination of

ports running at 2.048, 4.096, 8.192 and

16.384 Mbps

• 16 serial TDM input, 16 serial TDM output

streams

• Integrated Digital Phase-Locked Loop (DPLL)

exceeds Telcordia GR-1244-CORE Stratum 4E

specifications

• Output clocks have less than 1 ns of jitter (except

for the 1.544 MHz output)

• DPLL provides holdover, freerun and jitter

attenuation features with four independent

reference source inputs

• Exceptional input clock cycle to cycle variation

tolerance (20 ns for all rates)

July 2005

Ordering Information

ZL50015GAC 256 Ball PBGA

ZL50015QCC 256 Lead LQFP

ZL50015QCC1 256 Lead LQFP*

*Pb Free Matte Tin

-40°C to +85°C

Trays

Trays

Trays

• Output streams can be configured as bi-

directional for connection to backplanes

• Per-stream input and output data rate conversion

selection at 2.048 Mbps, 4.096 Mbps, 8.192 Mbps

or 16.384 Mbps. Input and output data rates can

differ

• Per-stream high impedance control outputs

(STOHZ) for 8 output streams

• Per-stream input bit delay with flexible sampling

point selection

VDD_CORE

VDD_IO

VDD_COREA VDD_IOA

VSS

RESET

ODE

STi[15:0]

FPi

CKi

MODE_4M0

MODE_4M1

REF0

REF1

REF2

REF3

REF_FAIL0

REF_FAIL1

REF_FAIL2

REF_FAIL3

OSC_EN

S/P Converter

Input Timing

DPLL

Data Memory

Connection Memory

OSC

Internal Registers &

Microprocessor Interface

P/S Converter

Output HiZ

Control

Output Timing

Test Port

STio[15:0]

STOHZ[7:0]

FPo[3:0]

CKo[5:0]

FPo_OFF[2:0]

Figure 1 - ZL50015 Functional Block Diagram

Zarlink Semiconductor US Patent No. 5,602,884, UK Patent No. 0772912,

France Brevete S.G.D.G. 0772912; Germany DBP No. 69502724.7-08

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2004-2005, Zarlink Semiconductor Inc. All Rights Reserved.

1 page

ZL50015

Data Sheet

Table of Contents

15.2 Maximum Time Interval Error (MTIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

15.3 Phase Alignment Speed (Phase Slope) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

15.4 Reference Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

15.5 Single Period Reference Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

15.6 Multiple Period Reference Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

16.0 Microprocessor Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

17.0 Device Reset and Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

17.1 Power-up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

17.2 Device Initialization on Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

17.3 Software Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

18.0 Pseudo random Bit Generation and Error Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

19.0 PCM A-law/µ-law Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

20.0 Quadrant Frame Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

21.0 JTAG Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

21.1 Test Access Port (TAP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

21.2 Instruction Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

21.3 Test Data Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

21.4 BSDL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

22.0 Register Address Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

23.0 Detailed Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

24.0 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

24.1 Memory Address Mappings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

24.2 Connection Memory Low (CM_L) Bit Assignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

24.3 Connection Memory High (CM_H) Bit Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

25.0 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

25.1 OSCi Master Clock Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

25.1.1 External Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

25.1.2 External Clock Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

26.0 DC Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

27.0 AC Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5

Zarlink Semiconductor Inc.

5 Page

ZL50015

Data Sheet

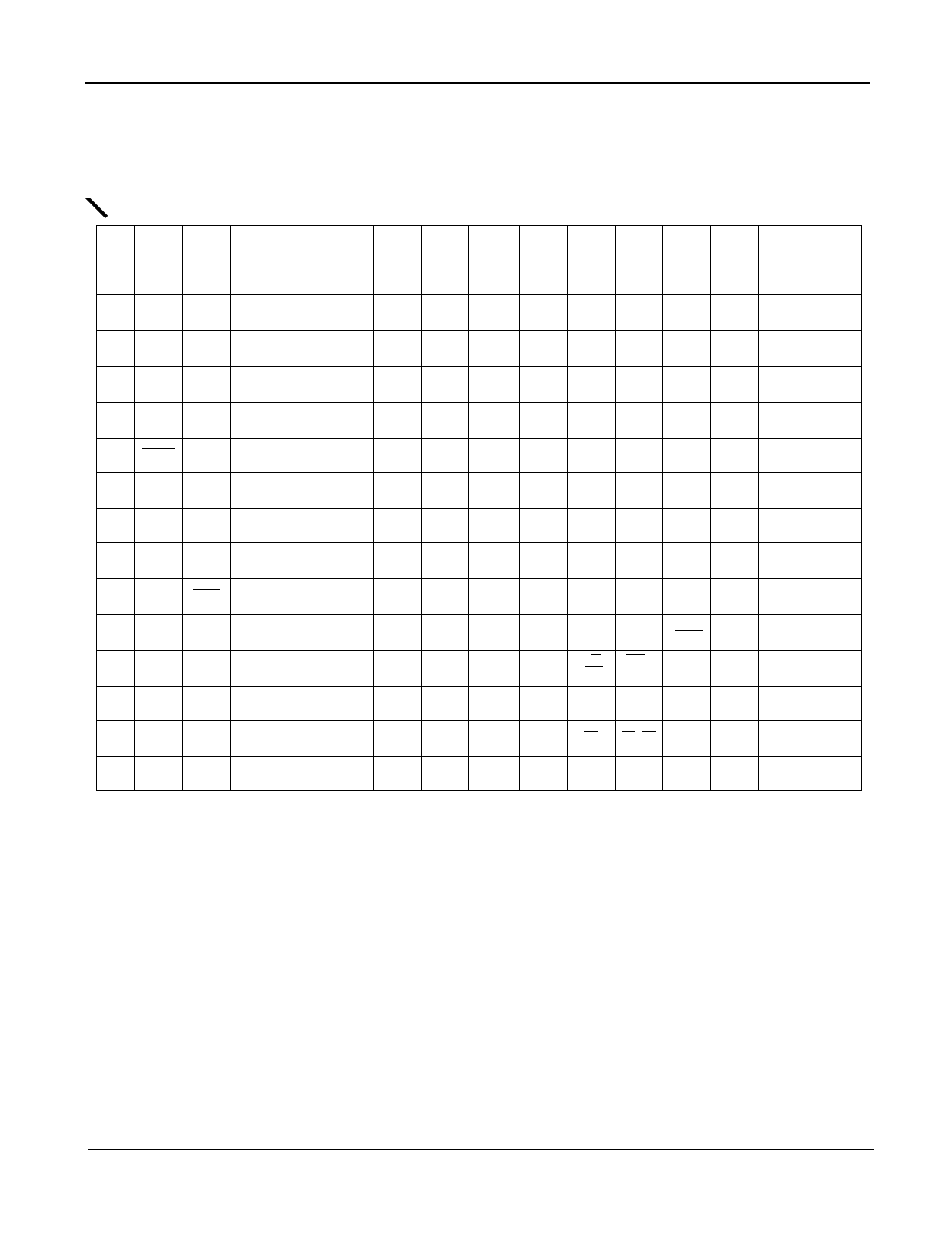

1.0 Pinout Diagrams

1.1 BGA Pinout

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

A VSS

NC

B NC STi10

NC

STi5

NC NC NC NC

STi4

CKo2

STi0

CKo0

C NC

STi9

VSS

STi7

STi6

STi1

CKo1

D NC

STi11 VDD_IO

STi3

STi2 CKo4 REF3

E NC

F NC

STi14

STi15

STi8

STi12

VDD_IO

VSS

STi13 VDD_IO

VDD_

CORE

VDD_

CORE

REF_

FAIL3

VDD_

CORE

G NC RESET IC_GND IC_Open TDo

VDD_IO

VSS

H NC

VSS

VSS

VDD_

COREA

CKo5

VSS

VSS

J NC VDD_IOA VDD_IOA

VSS

VSS CKo3 VSS

K NC

L NC

M NC

VSS

VDD_

COREA

NC

TMS

TRST

TDi

VSS

TCK

D0

VDD_

COREA

VDD_IO

VSS

VDD_IO

VDD_

CORE

VDD_

CORE

VSS

VDD_

CORE

VDD_

CORE

N NC

NC VDD_IO STio0 STOHZ3 D1

D5

P NC

NC

VSS STio1 STio3 STOHZ1 D3

R NC

NC STOHZ0 STio2 STOHZ2 D2

D4

T VSS

NC

NC

NC

NC

NC

NC

NC NC NC NC NC NC NC NC

REF2

REF_

FAIL2

REF1

REF_

FAIL1

VSS

VSS

VSS

VDD_

COREA

FPi

CKi IC_Open IC_Open OSCi ODE

VSS IC_Open IC_Open OSCo IC_GND VSS STio15

REF_

FAIL0

REF0

VSS

VSS

NC

VDD_

CORE

FPo_

OFF1

VDD_

CORE

VDD_

CORE

OSC_

EN

STio13

VDD_IO STio14

VSS VDD_IO STio12 FPo2

VDD_IO IC_Open FPo3

FPo_

OFF2

VSS

VSS

VDD_IO

A12

A13 FPo1 FPo0

VSS VSS A7

A9

A10

FPo_

OFF0

A11

VSS VSS VSS A3 A4 A5 A8 A6

VSS VSS VSS VDD_IO IC_Open A0 A2 A1

VSS

VSS

VDD_

CORE

VDD_

CORE

VDD_IO STio10 STio11

STio9

D6

D10

VDD_

CORE

VDD_

CORE

VSS

MOT MODE_

_INTEL 4M0

STio8

D7

D11

D13

R/W

_WR

DTA_

RDY

STio4 VDD_IO STOHZ5

D8 D14 IRQ STio5 STOHZ4 STOHZ6 VSS STOHZ7

D9

D12

D15

CS

DS_RD

MODE_

4M1

STio6

STio7

NC NC NC NC NC NC NC NC

VSS

A

NC B

NC C

NC D

NC E

NC F

NC G

NC H

NC J

NC K

NC L

NC M

NC N

NC P

NC R

VSS

T

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Note: A1 corner identified by metallized marking.

Note: Pinout is shown as viewed through top of package.

Figure 2 - ZL50015 256-Ball 17 mm x 17 mm PBGA (as viewed through top of package)

11

Zarlink Semiconductor Inc.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ZL50015.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ZL50010 | Flexible 512 Channel DX | Zarlink Semiconductor |

| ZL50011 | Flexible 512 Channel DX | Zarlink Semiconductor |

| ZL50012 | Flexible 512-ch Digital Switch | Zarlink Semiconductor |

| ZL50015 | Enhanced 1 K Digital Switch | Zarlink Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |