|

|

PDF 74AUP2G00 Data sheet ( Hoja de datos )

| Número de pieza | 74AUP2G00 | |

| Descripción | Low-power dual 2-input NAND gate | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74AUP2G00 (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

74AUP2G00

Low-power dual 2-input NAND gate

Rev. 8 — 5 February 2013

Product data sheet

1. General description

The 74AUP2G00 provides dual 2-input NAND function.

Schmitt trigger action at all inputs makes the circuit tolerant to slower input rise and fall

times across the entire VCC range from 0.8 V to 3.6 V.

This device ensures a very low static and dynamic power consumption across the entire

VCC range from 0.8 V to 3.6 V.

This device is fully specified for partial power-down applications using IOFF. The IOFF

circuitry disables the output, preventing a damaging backflow current through the device

when it is powered down.

2. Features and benefits

Wide supply voltage range from 0.8 V to 3.6 V

High noise immunity

Complies with JEDEC standards:

JESD8-12 (0.8 V to 1.3 V)

JESD8-11 (0.9 V to 1.65 V)

JESD8-7 (1.2 V to 1.95 V)

JESD8-5 (1.8 V to 2.7 V)

JESD8-B (2.7 V to 3.6 V)

ESD protection:

HBM JESD22-A114F Class 3A exceeds 5000 V

MM JESD22-A115-A exceeds 200 V

CDM JESD22-C101E exceeds 1 000 V

Low static power consumption; ICC = 0.9 A (maximum)

Latch-up performance exceeds 100 mA per JESD78 Class II

Inputs accept voltages up to 3.6 V

Low noise overshoot and undershoot < 10 % of VCC

IOFF circuitry provides partial power-down mode operation

Multiple package options

Specified from 40 C to +85 C and 40 C to +125 C

1 page

NXP Semiconductors

74AUP2G00

Low-power dual 2-input NAND gate

10. Static characteristics

Table 7. Static characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

Symbol Parameter

Conditions

Min Typ

Tamb = 25 C

VIH HIGH-level input voltage

VCC = 0.8 V

VCC = 0.9 V to 1.95 V

0.70 VCC -

0.65 VCC -

VCC = 2.3 V to 2.7 V

1.6 -

VCC = 3.0 V to 3.6 V

2.0 -

VIL LOW-level input voltage VCC = 0.8 V

--

VCC = 0.9 V to 1.95 V

VCC = 2.3 V to 2.7 V

--

--

VCC = 3.0 V to 3.6 V

--

VOH HIGH-level output voltage VI = VIH or VIL

IO = 20 A; VCC = 0.8 V to 3.6 V

IO = 1.1 mA; VCC = 1.1 V

IO = 1.7 mA; VCC = 1.4 V

IO = 1.9 mA; VCC = 1.65 V

IO = 2.3 mA; VCC = 2.3 V

IO = 3.1 mA; VCC = 2.3 V

VCC 0.1 -

0.75 VCC -

1.11 -

1.32 -

2.05 -

1.9 -

IO = 2.7 mA; VCC = 3.0 V

IO = 4.0 mA; VCC = 3.0 V

2.72 -

2.6 -

VOL LOW-level output voltage VI = VIH or VIL

IO = 20 A; VCC = 0.8 V to 3.6 V

-

-

IO = 1.1 mA; VCC = 1.1 V

--

IO = 1.7 mA; VCC = 1.4 V

--

IO = 1.9 mA; VCC = 1.65 V

--

IO = 2.3 mA; VCC = 2.3 V

--

IO = 3.1 mA; VCC = 2.3 V

--

IO = 2.7 mA; VCC = 3.0 V

--

IO = 4.0 mA; VCC = 3.0 V

-

II

input leakage current

VI = GND to 3.6 V; VCC = 0 V to 3.6 V

-

-

-

IOFF

IOFF

power-off leakage current

additional power-off

leakage current

VI or VO = 0 V to 3.6 V; VCC = 0 V

VI or VO = 0 V to 3.6 V;

VCC = 0 V to 0.2 V

-

-

-

-

ICC

ICC

supply current

additional supply current

VI = GND or VCC; IO = 0 A;

VCC = 0.8 V to 3.6 V

VI = VCC 0.6 V; IO = 0 A;

VCC = 3.3 V

-

[1] -

-

-

CI input capacitance

VCC = 0 V to 3.6 V; VI = GND or VCC

-

0.8

CO output capacitance

VO = GND; VCC = 0 V

- 1.7

Max Unit

-V

-V

-V

-V

0.30 VCC V

0.35 VCC V

0.7 V

0.9 V

-V

-V

-V

-V

-V

-V

-V

-V

0.1

0.3 VCC

0.31

0.31

0.31

0.44

0.31

0.44

0.1

0.2

0.2

V

V

V

V

V

V

V

V

A

A

A

0.5 A

40 A

- pF

- pF

74AUP2G00

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 8 — 5 February 2013

© NXP B.V. 2013. All rights reserved.

5 of 21

5 Page

NXP Semiconductors

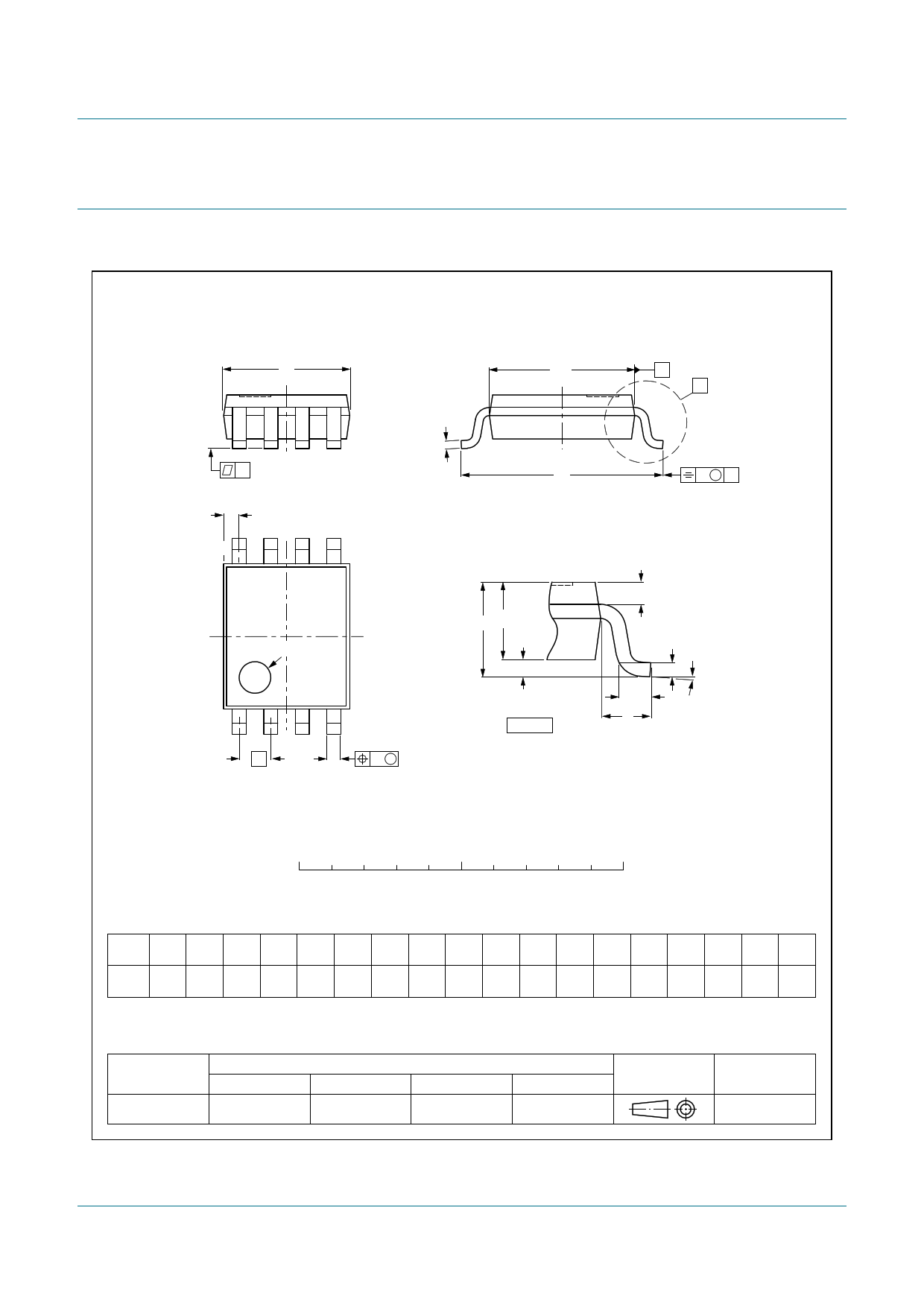

13. Package outline

74AUP2G00

Low-power dual 2-input NAND gate

VSSOP8: plastic very thin shrink small outline package; 8 leads; body width 2.3 mm

SOT765-1

D

y

Z

8

5

pin 1 index

E

c

HE

A A2

A1

1

e

4

bp w M

detail X

A

X

vM A

Q

(A3)

θ

Lp

L

0 2.5 5 mm

scale

DIMENSIONS (mm are the original dimensions)

UNIT

A

max.

A1

A2

A3

bp

c D(1) E(2) e

mm

1

0.15

0.00

0.85

0.60

0.12

0.27

0.17

0.23

0.08

2.1

1.9

2.4

2.2

0.5

Notes

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

HE

3.2

3.0

OUTLINE

VERSION

SOT765-1

IEC

REFERENCES

JEDEC

JEITA

MO-187

L Lp Q v w y Z(1) θ

0.4

0.40 0.21

0.15 0.19

0.2

0.13

0.1

0.4

0.1

8°

0°

EUROPEAN

PROJECTION

ISSUE DATE

02-06-07

Fig 10. Package outline SOT765-1 (VSSOP8)

74AUP2G00

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 8 — 5 February 2013

© NXP B.V. 2013. All rights reserved.

11 of 21

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet 74AUP2G00.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74AUP2G00 | Low-power dual 2-input NAND gate | NXP Semiconductors |

| 74AUP2G00 | DUAL NAND GATE | Diodes |

| 74AUP2G02 | DUAL NOR GATE | Diodes |

| 74AUP2G02 | Low-power Dual 2-input NOR Gate | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |