|

|

PDF SSTUB32866 Data sheet ( Hoja de datos )

| Número de pieza | SSTUB32866 | |

| Descripción | configurable registered buffer | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SSTUB32866 (archivo pdf) en la parte inferior de esta página. Total 29 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

SSTUB32866

1.8 V 25-bit 1 : 1 or 14-bit 1 : 2 configurable registered buffer

with parity for DDR2-800 RDIMM applications

Rev. 02 — 9 October 2006

Product data sheet

1. General description

The SSTUB32866 is a 1.8 V configurable register specifically designed for use on DDR2

memory modules requiring a parity checking function. It is defined in accordance with the

JEDEC standard for the SSTUB32866 registered buffer. The register is configurable

(using configuration pins C0 and C1) to two topologies: 25-bit 1 : 1 or 14-bit 1 : 2, and in

the latter configuration can be designated as Register A or Register B on the DIMM.

The SSTUB32866 accepts a parity bit from the memory controller on its parity bit

(PAR_IN) input, compares it with the data received on the DIMM-independent D-inputs

and indicates whether a parity error has occurred on its open-drain QERR pin

(active LOW). The convention is even parity, that is, valid parity is defined as an even

number of ones across the DIMM-independent data inputs combined with the parity input

bit.

The SSTUB32866 is packaged in a 96-ball, 6 × 16 grid, 0.8 mm ball pitch LFBGA

package (13.5 mm × 5.5 mm).

2. Features

I Configurable register supporting DDR2 up to 800 MT/s Registered DIMM applications

I Configurable to 25-bit 1 : 1 mode or 14-bit 1 : 2 mode

I Controlled output impedance drivers enable optimal signal integrity and speed

I Meets or exceeds SSTUB32866 JEDEC standard speed performance

I Supports up to 450 MHz clock frequency of operation

I Optimized pinout for high-density DDR2 module design

I Chip-selects minimize power consumption by gating data outputs from changing state

I Supports SSTL_18 data inputs

I Checks parity on the DIMM-independent data inputs

I Partial parity output and input allows cascading of two SSTUB32866s for correct parity

error processing

I Differential clock (CK and CK) inputs

I Supports LVCMOS switching levels on the control and RESET inputs

I Single 1.8 V supply operation (1.7 V to 2.0 V)

I Available in 96-ball, 13.5 mm × 5.5 mm, 0.8 mm ball pitch LFBGA package

3. Applications

I 400 MT/s to 800 MT/s DDR2 registered DIMMs desiring parity checking functionality

1 page

NXP Semiconductors

SSTUB32866

1.8 V DDR2-800 configurable registered buffer with parity

6. Pinning information

6.1 Pinning

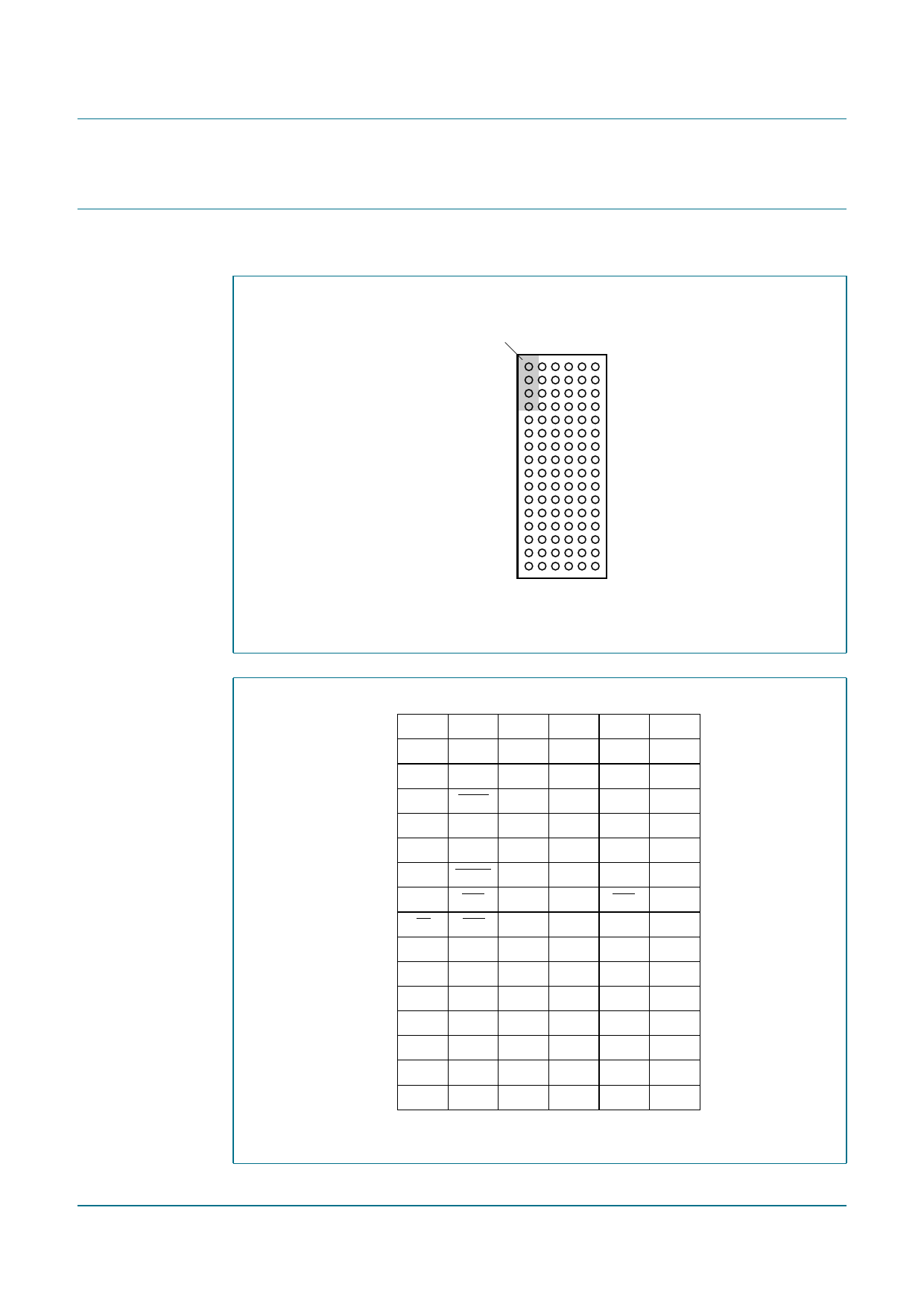

SSTUB32866EC/G

ball A1 SSTUB32866EC/S

index area

123456

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

002aac011

Transparent top view

Fig 3. Pin configuration for LFBGA96

SSTUB32866_2

Product data sheet

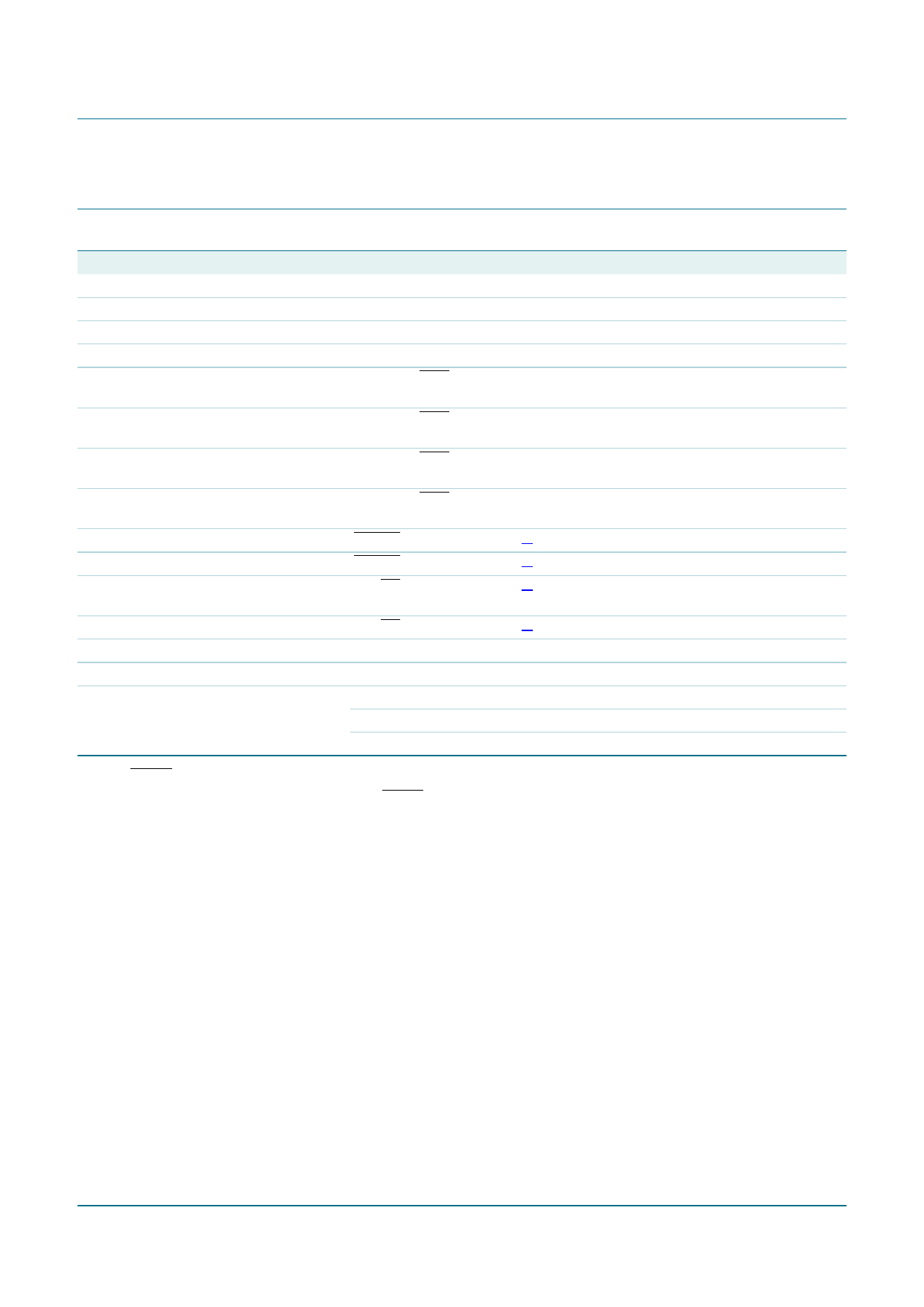

123

A DCKE PPO VREF

B D2

D15 GND

C D3

D16

D DODT QERR

VDD

GND

E D5

F D6

D17 VDD

D18 GND

G PAR_IN RESET

H CK

DCS

VDD

GND

J CK

K D8

CSR

D19

VDD

GND

L D9

D20 VDD

M D10

D21 GND

N D11 D22 VDD

P D12

D23 GND

R D13

T D14

D24 VDD

D25 VREF

4

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

VDD

56

QCKE DNU

Q2 Q15

Q3 Q16

QODT DNU

Q5 Q17

Q6 Q18

C1 C0

QCS DNU

n.c. n.c.

Q8 Q19

Q9 Q20

Q10 Q21

Q11 Q22

Q12 Q23

Q13 Q24

Q14

Q25

002aab108

Fig 4. Ball mapping, 1 : 1 register (C0 = 0, C1 = 0)

Rev. 02 — 9 October 2006

© NXP B.V. 2006. All rights reserved.

5 of 29

5 Page

NXP Semiconductors

SSTUB32866

1.8 V DDR2-800 configurable registered buffer with parity

9. Recommended operating conditions

Table 7. Recommended operating conditions

Symbol Parameter

Conditions

VDD

Vref

VT

VI

VIH(AC)

supply voltage

reference voltage

termination voltage

input voltage

AC HIGH-level input voltage

data (Dn), CSR, and

PAR_IN inputs

VIL(AC) AC LOW-level input voltage

data (Dn), CSR, and

PAR_IN inputs

VIH(DC) DC HIGH-level input voltage

data (Dn), CSR, and

PAR_IN inputs

VIL(DC) DC LOW-level input voltage

data (Dn), CSR, and

PAR_IN inputs

VIH

VIL

VICR

HIGH-level input voltage

LOW-level input voltage

common mode input voltage

range

RESET, Cn

RESET, Cn

CK, CK

VID

IOH

IOL

Tamb

differential input voltage

HIGH-level output current

LOW-level output current

ambient temperature

CK, CK

operating in free air

SSTUB32866EC/G

SSTUB32866EC/S

Min

1.7

0.49 × VDD

Vref − 0.040

0

Vref + 0.250

Typ Max

- 2.0

0.50 × VDD

Vref

-

-

0.51 × VDD

Vref + 0.040

VDD

-

Unit

V

V

V

V

V

- - Vref − 0.250 V

Vref + 0.125 -

-

V

--

[1] 0.65 × VDD

[1] -

[2] 0.675

-

-

-

Vref − 0.125 V

-

0.35 × VDD

1.125

V

V

V

[2] 600

-

-

mV

- - −8 mA

-

-8

mA

0 - 70 °C

0 - 85 °C

[1] The RESET and Cn inputs of the device must be held at valid levels (not floating) to ensure proper device operation.

[2] The differential inputs must not be floating, unless RESET is LOW.

SSTUB32866_2

Product data sheet

Rev. 02 — 9 October 2006

© NXP B.V. 2006. All rights reserved.

11 of 29

11 Page | ||

| Páginas | Total 29 Páginas | |

| PDF Descargar | [ Datasheet SSTUB32866.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SSTUB32866 | configurable registered buffer | NXP Semiconductors |

| SSTUB32868 | 1.8 V 28-bit 1 : 2 configurable registered buffer with parity | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |