|

|

PDF CS42L52 Data sheet ( Hoja de datos )

| Número de pieza | CS42L52 | |

| Descripción | Stereo CODEC w/Headphone & Speaker Amps | |

| Fabricantes | Cirrus Logic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CS42L52 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DRAFTv1

3/1/13

CS42L52

Low-Power, Stereo CODEC with Headphone and Speaker Amps

Stereo CODEC

High Performance Stereo ADC and DAC

– 99 dB (ADC), 98 dB (DAC) Dyn. Range (A-wtd)

– -88 dB THD+N

Flexible Stereo Analog Input Architecture

– 4:1 Analog Input MUX

– Analog Input Mixing

– Analog Passthrough with Volume Control

– Analog Programmable Gain Amplifier (PGA)

Programmable Automatic Level Control (ALC)

– Noise Gate for Noise Suppression

– Programmable Threshold and Attack/Release

Rates

Dual MIC Inputs

– Differential or Single-ended

– +16 dB to +32 dB with 1-dB step Mic Pre-

Amplifiers

– Programmable, Low-noise MIC Bias Levels

Digital Signal Processing Engine

– Bass and Treble Tone Control, De-emphasis

– Master Vol. and Independent PCM SDIN + ADC

SDOUT Mix Volume Control

– Soft-Ramp and Zero-Cross Transitions

– Programmable Peak-detect and Limiter

– Beep Generator w/Full Tone Control

Class D Stereo/Mono Speaker Amplifier

No External Filter Required

High-power Stereo Output at 10% THD+N

– 2 x 1.00 W into 8 @ 5.0 V

– 2 x 550 mW into 8 @ 3.7 V

– 2 x 230 mW into 8 @ 2.5 V

High-power Mono Output at 10% THD+N

– 1 x 1.90 W into 4 @ 5.0 V

– 1 x 1.00 W into 4 @ 3.7 V

– 1 x 350 mW into 4 @ 2.5 V

Direct Battery-powered Operation

– Battery Level Monitoring and Compensation

81% Efficiency at 800 mW

Phase-aligned PWM Output Reduces Idle

Channel Current

Spread Spectrum Modulation

Low Quiescent Current

Stereo Headphone Amplifier

Ground-centered Outputs

– No DC-Blocking Capacitors Required

– Integrated Negative Voltage Regulator

High-power Output at -75 dB THD+N

– 2 x 23 mW Into 16 @ 1.8 V

– 2 x 44 mW Into 16 @ 2.5 V

(Features continued on page 2)

Left

Inputs

Right

Inputs

1

2

3

4

1

2

3

4

+1.65 V to +2.63 V

Analog Supply

Summing

Programmable

Gain Amps

Multi-bit

ADC

+16 to +32 dB Diff./

S.E. MIC Pre-Amps

MIC Bias

+1.65 V to +2.63 V

Digital Supply

+1.60 V to +5.25 V

Battery

Battery Level Monitoring & Compensation

Pulse-Width

Modulator

ALC (PWM)

Beep

Volume, Mono

Swap, Mix

Mono mix,

Limiter, Bass,

Treble Adjust

HPF

ALC

Multi-bit

DAC

Control Port

Serial Audio Port

Level Shifter

+ Stereo/Mono

- Full-Bridge

+

-

Speaker

Outputs

Class D Amps

Left HP/Line

Output

Ground-Centered

Amps

-VHP

+VHP

Charge Pump

Right HP/Line

Output

Speaker/HP

Switch

+1.65 V to +2.63 V

Headphone Supply

Selectable

Bias Voltage

+1.65 V to +3.47 V

Interface Supply

I2C Control

Reset

Serial Audio

Input/Output

+1.65 V to +2.63 V

Analog Supply

http://www.cirrus.com

Copyright Cirrus Logic, Inc. 2013

(All Rights Reserved)

MAR ’13

DS680F2

1 page

3/1/13

CS42L52

6.12 Playback Control 1 (Address 0Dh) ............................................................................................... 51

6.12.1 Headphone Analog Gain ..................................................................................................... 51

6.12.2 Playback Volume Setting B=A ............................................................................................ 51

6.12.3 Invert PCM Signal Polarity .................................................................................................. 52

6.12.4 Master Playback Mute ......................................................................................................... 52

6.13 Miscellaneous Controls (Address 0Eh) ........................................................................................ 52

6.13.1 Passthrough Analog ............................................................................................................ 52

6.13.2 Passthrough Mute ............................................................................................................... 52

6.13.3 Freeze Registers ................................................................................................................. 52

6.13.4 HP/Speaker De-emphasis ................................................................................................... 53

6.13.5 Digital Soft Ramp ................................................................................................................ 53

6.13.6 Digital Zero Cross ................................................................................................................ 53

6.14 Playback Control 2 (Address 0Fh) ................................................................................................ 54

6.14.1 Headphone Mute ................................................................................................................. 54

6.14.2 Speaker Mute ...................................................................................................................... 54

6.14.3 Speaker Volume Setting B=A .............................................................................................. 54

6.14.4 Speaker Channel Swap ....................................................................................................... 54

6.14.5 Speaker MONO Control ...................................................................................................... 54

6.14.6 Speaker Mute 50/50 Control ............................................................................................... 54

6.15 MICx Amp Control:MIC A (Address 10h) and MIC B (Address 11h) ............................................ 55

6.15.1 MIC x Select ........................................................................................................................ 55

6.15.2 MICx Configuration .............................................................................................................. 55

6.15.3 MICx Gain ........................................................................................................................... 55

6.16 PGAx Vol. and ALCx Transition Ctl.:

ALC, PGA A (Address 12h) and ALC, PGA B (Address 13h) .............................................................. 55

6.16.1 ALCx Soft Ramp Disable ..................................................................................................... 55

6.16.2 ALCx Zero Cross Disable .................................................................................................... 56

6.16.3 PGAx Volume ...................................................................................................................... 56

6.17 Passthrough x Volume: PASSAVOL (Address 14h) and PASSBVOL (Address 15h) ................. 57

6.17.1 Passthrough x Volume ........................................................................................................ 57

6.18 ADCx Volume Control: ADCAVOL (Address 16h) and ADCBVOL (Address 17h) ....................... 57

6.18.1 ADCx Volume ...................................................................................................................... 57

6.19 ADCx Mixer Volume: ADCA (Address 18h) and ADCB (Address 19h) ........................................ 58

6.19.1 ADC Mixer Channel x Mute ................................................................................................. 58

6.19.2 ADC Mixer Channel x Volume ............................................................................................. 58

6.20 PCMx Mixer Volume: PCMA (Address 1Ah) and PCMB (Address 1Bh) ...................................... 58

6.20.1 PCM Mixer Channel x Mute ................................................................................................ 58

6.20.2 PCM Mixer Channel x Volume ............................................................................................ 58

6.21 Beep Frequency and On Time (Address 1Ch) ............................................................................. 59

6.21.1 Beep Frequency .................................................................................................................. 59

6.21.2 Beep On Time ..................................................................................................................... 60

6.22 Beep Volume and Off Time (Address 1Dh) .................................................................................. 60

6.22.1 Beep Off Time ..................................................................................................................... 60

6.22.2 Beep Volume ....................................................................................................................... 61

6.23 Beep and Tone Configuration (Address 1Eh) ............................................................................... 61

6.23.1 Beep Configuration .............................................................................................................. 61

6.23.2 Beep Mix Disable ................................................................................................................ 61

6.23.3 Treble Corner Frequency .................................................................................................... 62

6.23.4 Bass Corner Frequency ...................................................................................................... 62

6.23.5 Tone Control Enable ........................................................................................................... 62

6.24 Tone Control (Address 1Fh) ......................................................................................................... 62

6.24.1 Treble Gain .......................................................................................................................... 62

6.24.2 Bass Gain ............................................................................................................................ 63

6.25 Master Volume Control: MSTA (Address 20h) and MSTB (Address 21h) .................................... 63

DS680F2

5

5 Page

3/1/13

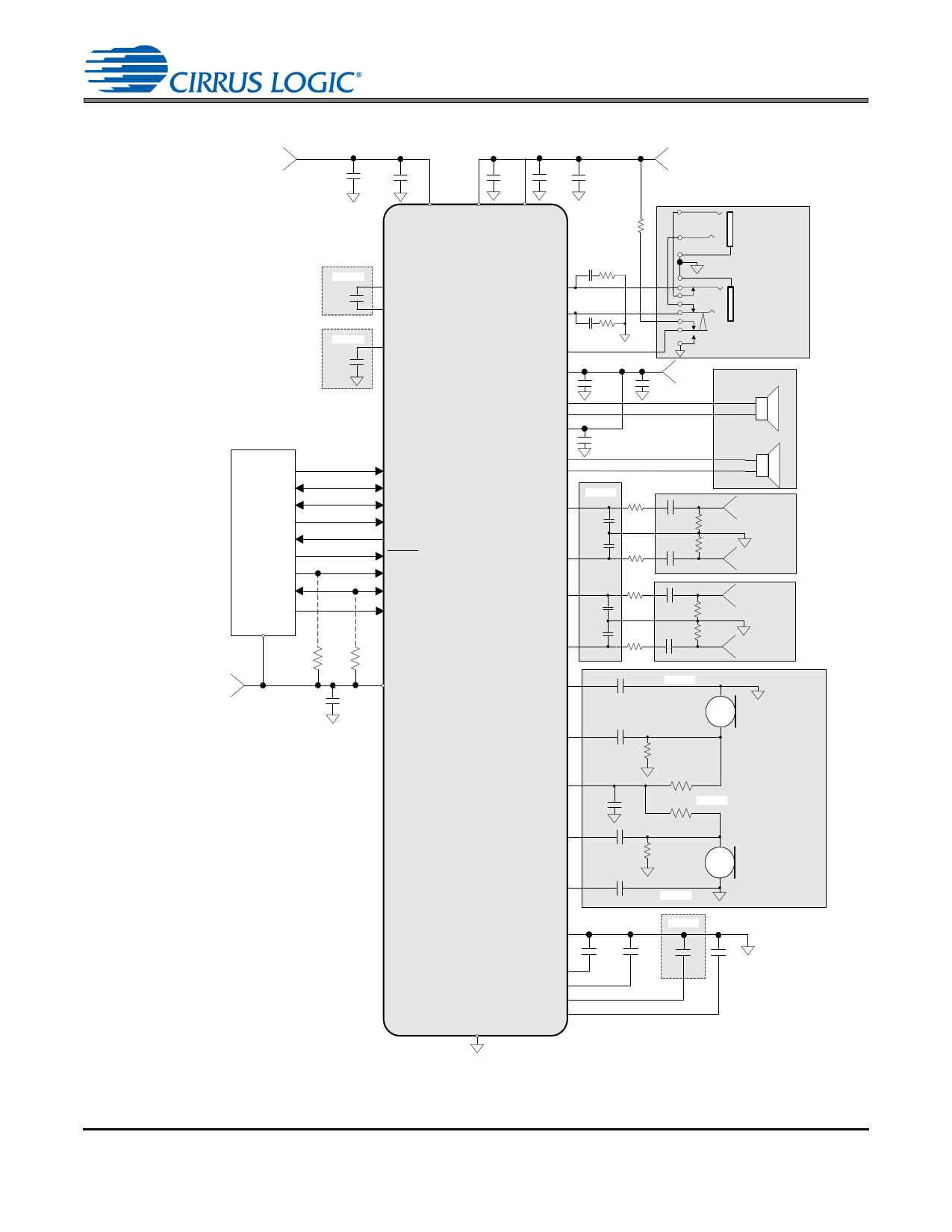

2. TYPICAL CONNECTION DIAGRAM

CS42L52

+1.8 V to +2.5 V

1 µF

0.1 µF

0.1 µF 0.1 µF 1 µF

+1.8 V to +2.5 V

See Note 5

VD VA +VHP

47 k

Line Level Out

Left & Right

Note 1

1 µF **

Note 2

1 µF **

* *Use low ESR ceramic capacitors.

Digital Audio

Processor

+1.8 V to +3.3 V

2 k 2 k

0.1 µF

Notes:

1. Recommended values for the default charge pump switching

frequency. The required capacitance follows an inverse

relationship with the charge pump’s switching frequency. When

increasing the switching frequency, the capacitance may

decrease; when lowering the switching frequency, the

capacitance must increase.

2. Larger capacitance reduces the ripple on the internal

amplifier’s supply. This may reduce the distortion at higher

output power levels.

3. Additional bulk capacitance may be added to improve PSRR

at low frequencies.

4. These capacitors serve as a charge reservoir for the internal

switched capacitor ADC modulators. They are only needed

when the PGA (Programmable Gain Amplifier) is bypassed.

5. Series resistance in the path of the power supplies must be

avoided. Any voltage drop on VHP will directly impact the

negative charge pump supply (-VHPFILT) and clip the audio

output.

6. The value of RL, a current-limiting resistor used with electret

condenser microphones, is dictated by the microphone

cartridge.

7. The negative terminal of the MICx inputs connects to the

ground pin of the microphone cartridge. Gain is applied only to

the positive terminal.

FLYP

FLYN

-VHPFILT

MCLK

SCLK

LRCK

SDIN

SDOUT

RESET

SCL

SDA

AD0

0.022 µF

HP/LINE_OUTB

51.1

HP/LINE_OUTA

51.1

0.022 µF

SPKR/HP

CS42L52

VP

0.1 µF

Headphone Out

Left & Right

+1.6 V to

10 µF +5 V Stereo Speakers

SPKR_OUTA+

SPKR_OUTA-

VP

0.1 µF

SPKR_OUTB+

SPKR_OUTB-

AIN1A

AIN1B

Note 4

1800 pF * 100

1800 pF *

100

Left 1

1 µF

100 k

Analog

100 k

Input 1

Right 1

1 µF

AIN2A

AIN2B

1800 pF * 100

1800 pF *

100

Left 2

1 µF

100 k

Analog

Input 2

100 k

Right 2

1 µF

VL

MIC1-

Note 7

AIN3A/MIC1A

1 µF

Microphone 1

MIC1+

AIN4A/MIC2A

1 µF

100 k

DGND

MICBIAS

0.1 µF

RL Note 6

Mic-Level

Inputs

MIC2+

AIN4B/MIC2B

RL

1 µF

100 k

Microphone 2

MIC2-

AIN3B/MIC1B

1 µF

Note 7

AGND

*

AFILTA

AFILTB

VQ

FILT+

*

150 pF

150 pF

Note 3

1 µF

10 µF

* Capacitors must be C0G or equivalent

Figure 1. Typical Connection Diagram

DS680F2

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CS42L52.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CS42L50 | Low Voltage/ Stereo CODEC with headphone Amp | Cirrus Logic |

| CS42L50-KN | Low Voltage/ Stereo CODEC with headphone Amp | Cirrus Logic |

| CS42L51 | Stereo CODEC | Cirrus Logic |

| CS42L51 | Stereo CODEC | Cirrus Logic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |