|

|

PDF CS5371A Data sheet ( Hoja de datos )

| Número de pieza | CS5371A | |

| Descripción | (CS5371A / CS5372A) High-performance Modulators | |

| Fabricantes | Cirrus Logic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CS5371A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

CS5371A

CS5372A

Low-power, High-performance ∆Σ Modulators

Features

Fourth-order ∆Σ Architecture

Clock-jitter-tolerant Architecture

Input Voltage: 5 Vpp Fully Differential

Input Signal Bandwidth: DC to 2 kHz

High Dynamic Range

• 127 dB SNR @ 215 Hz BW (2 ms sampling)

• 124 dB SNR @ 430 Hz BW (1 ms sampling)

Low Total Harmonic Distortion

• -118 dB THD typical (0.000126%)

• -112 dB THD maximum (0.000251%)

Low Power Consumption

• Normal operation: 25 mW per channel

• Power down: 10 µW per channel

Small Footprint, 24-pin SSOP package

Multi-channel System Support

• 1-channel System: CS5371A

• 2-channel System: CS5372A

• 3-channel System: CS5371A + CS5372A

• 4-channel System: CS5372A + CS5372A

Bipolar Power Supply Configuration

• VA+ = +2.5 V; VA- = -2.5 V; VD = +3.3 V

Description

The CS5371A and CS5372A are one- and two-channel,

high-dynamic-range, fourth-order ∆Σ modulators intend-

ed for geophysical and sonar applications. When

combined with CS3301A / CS3302A differential amplifi-

ers, the CS4373A test DAC and CS5376A digital filter, a

small, low-power, self-testing, high-accuracy, multi-

channel measurement system results.

The modulators have high dynamic range and low total

harmonic distortion with very low power consumption.

They convert differential analog input signals from the

CS3301A / CS3302A amplifiers to an oversampled seri-

al bit stream at 512 kbits per second. This oversampled

bit stream is then decimated by the CS5376A digital filter

to a 24-bit output at the selected output word rate.

In normal operation, power consumption is 5 mA per

channel. Each modulator can be independently powered

down to 500 µA per channel, and by halting the input

clock they will enter a micro-power state using only 2 µA

per channel.

The CS5371A and CS5372A modulators are available in

small 24-pin SSOP packages, providing exceptional per-

formance in a very small footprint.

ORDERING INFORMATION

See page 31.

VA+

PWDN

INR+

INF+

INF-

INR-

VREF+

VREF-

4th Order

∆Σ Modulator

CS5371A

VA-

OFST

VD

VA+

PWDN1

MFLAG

MDATA

Clock

Generator

MCLK

MSYNC

INR1+

INF1+

INF1-

INR1-

VREF+

VREF-

INR2+

INF2+

INF2-

INR2-

4th Order

∆Σ Modulator

4th Order

∆Σ Modulator

GND

VA- PWDN2 OFST

VD

MFLAG1

MDATA1

Clock

Generator

MCLK

MSYNC

MFLAG2

MDATA2

CS5372A

GND

http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2006

(All Rights Reserved)

DEC ‘06

DS748F1

1 page

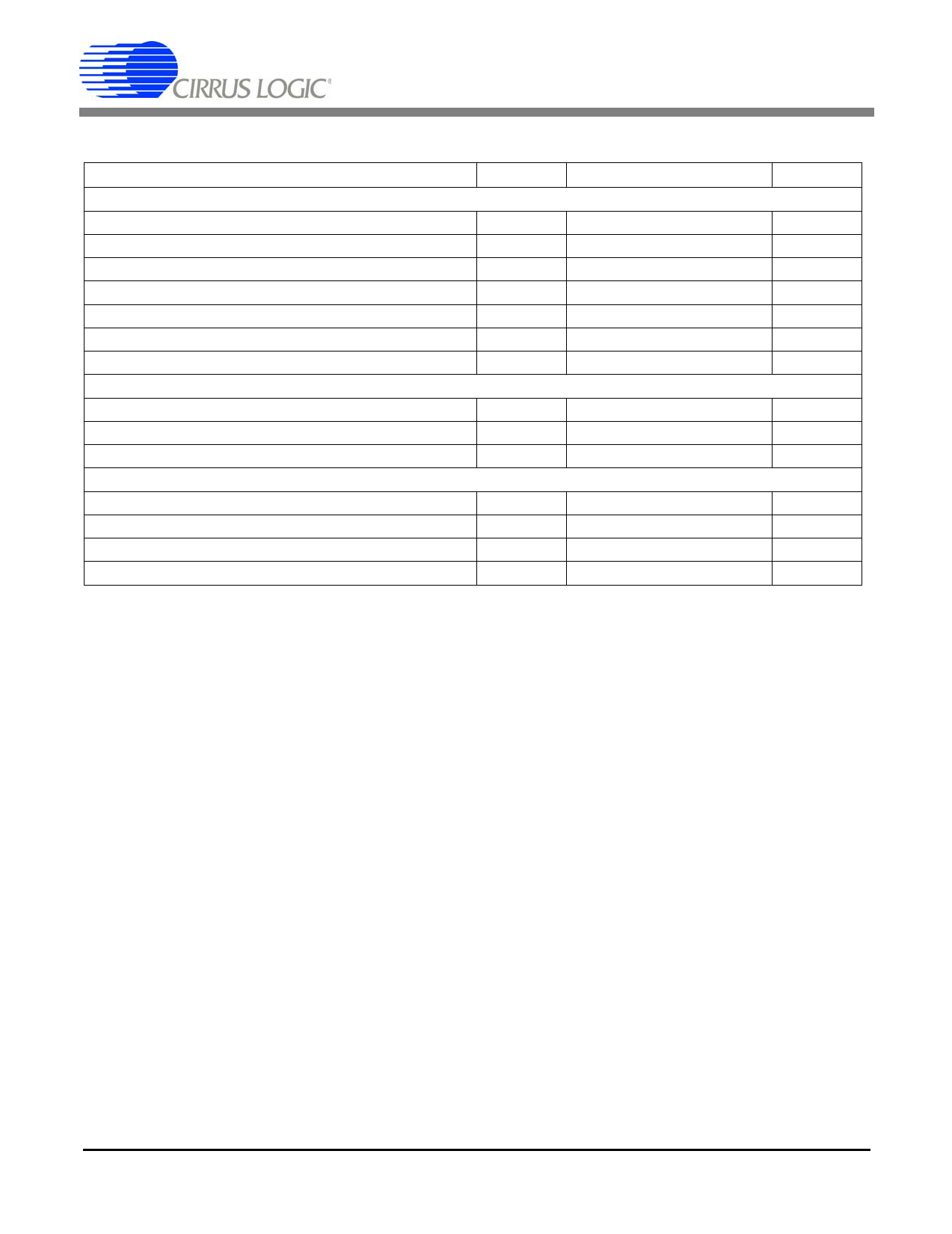

CS5371A CS5372A

TEMPERATURE CONDITIONS

Parameter

Symbol Min Typ Max

Unit

Ambient Operating Temperature

TA -40

-

85

ºC

Storage Temperature Range

TSTR

-65

-

150

ºC

Allowable Junction Temperature

TJCT

-

- 125

ºC

Junction to Ambient Thermal Impedance (4-layer PCB)

θJA

-

65

-

ºC / W

ANALOG INPUT CHARACTERISTICS

Parameter

Symbol

VREF Input

[VREF+] - [VREF-]

(Note 2, 3) VREF

VREF-

(Note 4) VREF-

VREF Input Current

VREF Input Noise

Modulator INR±, INF± Inputs

VREFIMOD

(Note 7) VREFIN

External Anti-alias Filter

(Note 8)

Series Resistance

Differential Capacitance

RAA

CDIFF

Differential Input Impedance

Single-ended Input Impedance

INR±

INF±

INR±

INF±

ZDIFINR

ZDIFINF

ZSEINR

ZSEINF

Min

-

-

-

-

-

-

-

-

-

-

Typ

2.500

VA -

120

-

680

20

20

1

40

2

Max

-

-

-

1

-

-

-

-

-

-

Unit

V

V

µA

µVrms

Ω

nF

kΩ

MΩ

kΩ

MΩ

Notes: 7. Maximum integrated noise over the measurement bandwidth for the voltage reference device attached

to the VREF± inputs.

8. Anti-alias capacitors are discrete external components and must be of good quality (C0G, NPO, poly).

Poor quality capacitors will degrade total harmonic distortion (THD) performance. See Figure 1 on

page 6

DS748F1

5

5 Page

CS5371A CS5372A

DIGITAL CHARACTERISTICS (CONT.)

Parameter

Master Clock Input

MCLK Frequency

MCLK Period

MCLK Duty Cycle

MCLK Rise Time

MCLK Fall Time

MCLK Jitter (in-band or aliased in-band)

MCLK Jitter (out-of-band)

Master Sync Input

MSYNC Setup Time to MCLK Falling

MSYNC Period

MSYNC Hold Time after MCLK Falling

MDATA Output

MDATA Output Bit Rate

MDATA Output Bit Period

MDATA Output One’s Density Range

Full-scale Output Code

Symbol Min

Typ Max

(Note 19) fCLK

- 2.048 -

(Note 19) tmclk

- 488 -

(Note 9) MCLKDC

40

-

60

(Note 9) tRISE - - 50

(Note 9) tFALL

-

- 50

(Note 9) MCLKIBJ

-

- 300

(Note 9) MCLKOBJ

-

-1

(Note 9, 20)

(Note 9, 20)

(Note 9, 20)

tmss

tmsync

tmsh

20 122

40 976

20 122

-

-

-

(Note 9)

(Note 21)

fmdata

tmdata

MDATOD

MDATFS

-

-

14

0xA2EBE0

512

1953

-

-

-

-

86

0x5D1420

Unit

MHz

ns

%

ns

ns

ps

ns

ns

ns

ns

kbits/s

ns

%

Notes: 19. MCLK is generated by the digital filter. If MCLK is disabled, the device automatically enters a power-

down state.

20. MSYNC is generated by the digital filter and is latched on MCLK falling edge, synchronization instant

(t0) is on the next MCLK rising edge.

21. Decimated, filtered, and offset-corrected 24-bit output word from the digital filter.

DS748F1

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CS5371A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CS5371 | LOW POWER HIGH PERFORMANCE MODULATORS | Cirrus Logic |

| CS5371-BS | LOW POWER HIGH PERFORMANCE MODULATORS | Cirrus Logic |

| CS5371A | (CS5371A / CS5372A) High-performance Modulators | Cirrus Logic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |