|

|

PDF CS5322 Data sheet ( Hoja de datos )

| Número de pieza | CS5322 | |

| Descripción | Two-Phase Buck Controller | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CS5322 (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

CS5322

Two−Phase Buck Controller

with Integrated Gate

Drivers and 5−Bit DAC

The CS5322 is a two−phase step down controller which

incorporates all control functions required to power high performance

processors and high current power supplies. Proprietary multi−phase

architecture guarantees balanced load current distribution and reduces

overall solution cost in high current applications. Enhanced V2™

control architecture provides the fastest possible transient response,

excellent overall regulation, and ease of use.

The CS5322 multi−phase architecture reduces output voltage and

input current ripple, allowing for a significant reduction in inductor

values and a corresponding increase in inductor current slew rate. This

approach allows a considerable reduction in input and output capacitor

requirements, as well as reducing overall solution size and cost.

Features

• Enhanced V2 Control Method

• 5−Bit DAC with 1.0% Accuracy

• Adjustable Output Voltage Positioning

• 4 On−Board Gate Drivers

• 200 kHz to 800 kHz Operation Set by Resistor

• Current Sensed through Buck Inductors, Sense Resistors, or V−S

Control

• Hiccup Mode Current Limit

• Individual Current Limits for Each Phase

• On−Board Current Sense Amplifiers

• 3.3 V, 1.0 mA Reference Output

• 5.0 V and/or 12 V Operation

• On/Off Control (through Soft Start Pin)

• Power Good Output with Internal Delay

http://onsemi.com

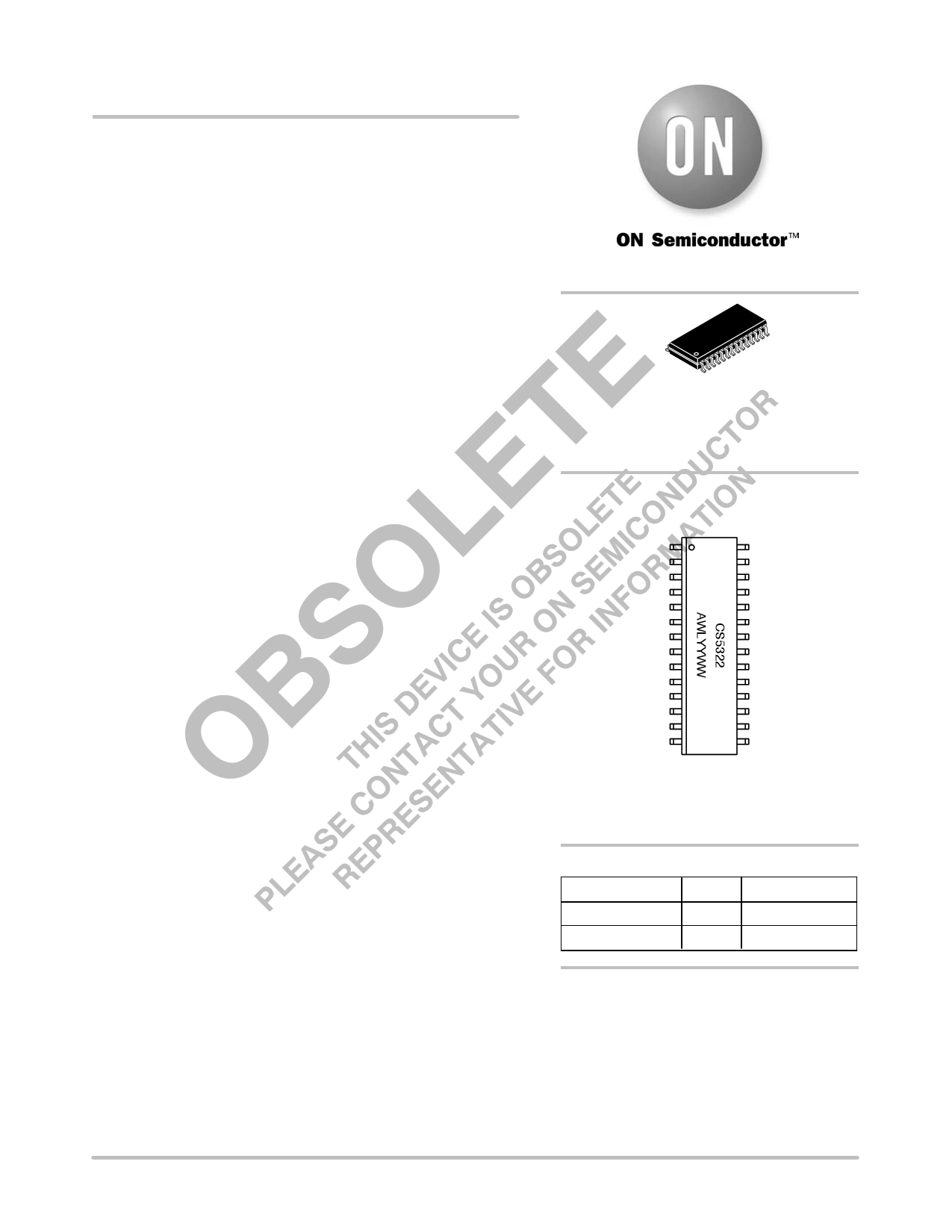

28

1

SO−28L

DW SUFFIX

CASE 751F

PIN CONNECTIONS AND

MARKING DIAGRAM

1

COMP

VFB

VDRP

CS1

CS2

CSREF

PWRGD

VID0

VID1

VID2

VID3

VID4

ILIM

REF

28ROSC

VCCL

VCCL1

GATE(L)1

GND

GATE(H)1

VCCH1

LGND

SS

VCCL2

GATE(L)2

GND2

GATE(H)2

VCCH2

A = Assembly Location

WL, L = Wafer Lot

YY, Y = Year

WW, W = Work Week

ORDERING INFORMATION

Device

Package

Shipping

CS5322GDW28

SO−28L 27 Units/Rail

CS5322GDWR28 SO−28L 1000 Tape & Reel

© Semiconductor Components Industries, LLC, 2006

July, 2006 − Rev. 7

1

Publication Order Number:

CS5322/D

1 page

CS5322

ELECTRICAL CHARACTERISTICS (0°C < TA < 70°C; 0°C < TJ < 125°C; 4.7 V < VCCL < 14 V; 8.0 V < VCCH < 20 V;

CGATE(H) = 3.3 nF, CGATE(L) = 3.3 nF, RR(OSC) = 32.4 k, CCOMP = 1.0 nF, CSS = 0.1 μF, CREF = 0.1 μF, DAC Code 10000, CVCC = 1.0 μF,

ILIM ≥ 1.0 V; unless otherwise specified.)

Characteristic

Test Conditions

Min Typ Max Unit

Power Good Output

Power Good Fault Delay

Output Low Voltage

Output Leakage Current

Lower Threshold

CSREF = VDAC to VDAC ± 15%

CSREF = 1.0 V, IPWRGD = 4.0 mA

CSREF = 1.45 V, PWRGD = 5.5 V

% of Nominal VID Code

25 50 125 μs

−

0.25 0.40

V

− 0.1 10 μA

−14 −11 −8.0 %

Upper Threshold

% of Nominal VID Code

8 11 14 %

Voltage Feedback Error Amplifier

VFB Bias Current (Note 2)

COMP Source Current

1.0 V < VFB < 1.9 V

COMP = 0.5 V to 2.0 V;

VFB = 1.8 V; DAC = 00000

9.0 10.3 11.5 μA

15 30 60 μA

COMP Sink Current

COMP Max Voltage

COMP Min Voltage

Transconductance

Output Impedance

COMP = 0.5 V to 2.0 V;

VFB = 1.9 V; DAC = 00000

VFB = 1.8 V COMP Open; DAC = 00000

VFB = 1.9 V COMP Open; DAC = 00000

−10 μA < ICOMP < +10 μA

−

15 30 60 μA

2.4 2.7 − V

− 0.1 0.2 V

− 32 − mmho

− 2.5 − MΩ

Open Loop DC Gain

Note 3

60 90

− dB

Unity Gain Bandwidth

0.01 μF COMP Capacitor

− 400 − kHz

PSRR @ 1.0 kHz

− − 70 − dB

Soft Start

Soft Start Charge Current

0.2 V ≤ SS ≤ 3.0 V

15 30 50 μA

Soft Start Discharge Current

0.2 V ≤ SS ≤ 3.0 V

4.0 7.5 13 μA

Hiccup Mode Charge/Discharge Ratio

−

3.0 4.0 − −

Peak Soft Start Charge Voltage

− 3.3 4.0 4.2 V

Soft Start Discharge Threshold Voltage

−

0.20 0.27 0.34

V

PWM Comparators

Minimum Pulse Width

Channel Start Up Offset

Measured from CSx to GATE(H)X

V(VFB) = V(CSREF) = 1.0 V, V(COMP) = 1.5 V

60 mV step applied between VCSX and VCREF

−

350 515 ns

V(CS1) = V(CS2) = V(VFB) = V(CSREF) = 0 V;

0.3

0.4

0.5

V

Measure V(COMP) when GATE(H)1,

GATE(H)2, switch high

GATE(H) and GATE(L)

High Voltage (AC)

Note 3 Measure VCCLX − GATE(L)X or

VCCHX − GATE(H)X

Low Voltage (AC)

Note 3 Measure GATE(L)X or GATE(H)X

Rise Time GATE(H)X

1.0 V < GATE < 8.0 V; VCCHX = 10 V

Rise Time GATE(L)X

1.0 V < GATE < 8.0 V; VCCLX = 10 V

2. The VFB Bias Current changes with the value of ROSC per Figure 4.

− 0 1.0 V

− 0 0.5 V

− 35 80 ns

− 35 80 ns

http://onsemi.com

5

5 Page

CS5322

APPLICATIONS INFORMATION

FIXED FREQUENCY MULTI−PHASE CONTROL

In a multi−phase converter, multiple converters are

connected in parallel and are switched on at different times.

This reduces output current from the individual converters

and increases the apparent ripple frequency. Because several

converters are connected in parallel, output current can ramp

up or down faster than a single converter (with the same

value output inductor) and heat is spread among multiple

components.

The CS5322 uses a two−phase, fixed frequency,

Enhanced V2 architecture. Each phase is delayed 180° from

the previous phase. Normally Gate(H) transitions high at the

beginning of each oscillator cycle. Inductor current ramps

up until the combination of the current sense signal and the

output ripple trip the PWM comparator and bring Gate(H)

low. Once Gate(H) goes low, it will remain low until the

beginning of the next oscillator cycle. While Gate(H) is

high, the enhanced V2 loop will respond to line and load

transients. Once Gate(H) is low, the loop will not respond

again until the beginning of the next cycle. Therefore,

constant frequency Enhanced V2 will typically respond

within the off−time of the converter.

The Enhanced V2 architecture measures and adjusts

current in each phase. An additional input (Cx) for inductor

current information has been added to the V2 loop for each

phase as shown in Figure 9.

SWNODE L

RL

RS

VOUT

+

CX +CSA

+

OFFSET

CSREF

+

+

VFB

DACOUT

E+.A.

+ COMP

PWM-

COMP

+

Figure 9. Enhanced V2 Feedback and Current

Sense Scheme

The inductor current is measured across RS, amplified by

CSA and summed with the OFFSET and Output Voltage at

the non−inverting input of the PWM comparator. The

inductor current provides the PWM ramp and as inductor

current increases the voltage on the positive pin of the PWM

comparator rises and terminates the PWM cycle. If the

inductor starts the cycle with a higher current, the PWM

cycle will terminate earlier providing negative feedback.

The CS5322 provides a Cx input for each phase, but the

CSREF, VFB and COMP inputs are common to all phases.

Current sharing is accomplished by referencing all phases to

the same VFB and COMP pins, so that a phase with a larger

current signal will turn off earlier than phases with a smaller

current signal.

Including both current and voltage information in the

feedback signal allows the open loop output impedance of

the power stage to be controlled. When the average output

current is zero, the COMP pin will be only 1/2 of the steady

state ramp height plus the OFFSET above the output

voltage. If the COMP pin is held steady and the inductor

current changes, there must also be a change in the output

voltage. Or, in a closed loop configuration when the output

current changes, the COMP pin must move to keep the same

output voltage. The required change in the output voltage or

COMP pin depends on the scaling of the current feedback

signal and is calculated as

DV + RS CSA Gain DI

The single−phase power stage output impedance is:

Single Stage Impedance + DVńDI + RS CSA Gain.

The multi−phase power stage output impedance is the

single−phase output impedance divided by the number of

phases. The output impedance of the power stage determines

how the converter will respond during the first few μs of a

transient before the feedback loop has repositioned the

COMP pin.

The peak output current of each phase can also be

calculated from;

Ipkout

(per

phase)

+

VCOMP *

RS

VFB * VOFFSET

CSA Gain

Figure 10 shows the step response of a single phase with

the COMP pin at a fixed level. Before T1 the converter is in

normal steady state operation. The inductor current provides

the PWM ramp through the Current Sense Amplifier. The

PWM cycle ends when the sum of the current signal, voltage

signal and OFFSET exceed the level of the COMP pin. At

T1 the output current increases and the output voltage sags.

The next PWM cycle begins and the cycle continues longer

than previously while the current signal increases enough to

make up for the lower voltage at the VFB pin and the cycle

ends at T2. After T2 the output voltage remains lower than

at light load and the current signal level is raised so that the

sum of the current and voltage signal is the same as with the

original load. In a closed loop system the COMP pin would

http://onsemi.com

11

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet CS5322.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CS5320 | 24-Bit Variable Bandwidth A/D Converter Chipset | Cirrus Logic |

| CS5320-KL | 24-Bit Variable Bandwidth A/D Converter Chipset | Cirrus Logic |

| CS5320-KL1 | 24-Bit Variable Bandwidth A/D Converter Chipset | Cirrus Logic |

| CS5321 | 24-Bit Variable Bandwidth A/D Converter Chipset | Cirrus Logic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |