|

|

PDF NBSG86A Data sheet ( Hoja de datos )

| Número de pieza | NBSG86A | |

| Descripción | 2.5V/3.3V SiGe Differential Smart Gate | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NBSG86A (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

NBSG86A

2.5V/3.3V SiGe Differential

Smart Gate with Output

Level Select

The NBSG86A is a multi−function differential Logic Gate which

can be configured as an AND/NAND, OR/NOR, XOR/XNOR, or 2:1

MUX. This device is part of the GigaComm™ family of high

performance Silicon Germanium products. The device is housed in a

low profile 4x4 mm, 16−pin, flip−chip BGA or a 3x3 mm 16 pin QFN

package.

Differential inputs incorporate internal 50 W termination resistors

and accept NECL (Negative ECL), PECL (Positive ECL),

LVCMOS/LVTTL, CML, or LVDS. The OLS* input is used to

program the peak−to−peak output amplitude between 0 and 800 mV

in five discrete steps.

The NBSG86A employs input default circuitry so that under open

input conditions (Dx, Dx, VTDx, VTDx, VTSEL) the outputs of the

device will remain stable.

Features

• Maximum Input Clock Frequency > 8 GHz Typical

• Maximum Input Data Rate > 8 Gb/s Typical

• 165 ps Typical Propagation Delay

• 40 ps Typical Rise and Fall Times

www.DataSheet4U.com

• Selectable Swing PECL Output with Operating Range:

VCC = 2.375 V to 3.465 V with VEE = 0 V

• Selectable Swing NECL Output with NECL Inputs with

Operating Range: VCC = 0 V with VEE = −2.375 V to −3.465 V

• Selectable Output Level (0 V, 200 mV, 400 mV,

600 mV, or 800 mV Peak−to−Peak Output)

• 50 W Internal Input Termination Resistors

• Pb−Free Packages are Available

*Output Level Select

http://onsemi.com

MARKING

DIAGRAM*

FCBGA−16

BA SUFFIX

CASE 489

1

QFN−16

MN SUFFIX

CASE 485G

SG

86A

LYW

16

ÇÇÇÇ1

SG

86A

ALYWG

G

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

(Note: Microdot may be in either location)

*For additional marking information, refer to

Application Note AND8002/D.

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 12 of this data sheet.

© Semiconductor Components Industries, LLC, 2006

July, 2006 − Rev. 10

1

Publication Order Number:

NBSG86A/D

1 page

NBSG86A

Table 7. Interfacing Options

INTERFACING OPTIONS

CONNECTIONS

CML

LVDS

Connect VTD0, VTD1, VTSEL and VTD0, VTD1 to VCC

Connect VTD0, VTD1, VTD0 and VTD1 together. Leave VTSEL open.

AC−COUPLED

Bias VTD0, VTD1, VTSEL and VTD0, VTD1 Inputs within (VIHCMR) Common Mode Range

RSECL, PECL, NECL

Standard ECL Termination Techniques

LVTTL, LVCMOS

An external voltage should be applied to the unused complementary differential input.

Nominal voltage 1.5 V for LVTTL and VCC/2 for LVCMOS inputs.

Table 8. ATTRIBUTES

Characteristics

Internal Input Pulldown Resistors

Internal Input Pullup Resistor

ESD Protection

(R1)

(R2)

Human Body Model

Machine Model

Charged Device Model

Moisture Sensitivity (Note 6)

16−FCBGA

16−QFN

Flammability Rating

Oxygen Index: 28 to 34

Transistor Count

Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

6. For additional information, see Application Note AND8003/D.

Value

75 kW

37.5 kW

> 1 KV

> 50 V

> 4 KV

Level 3

Level 1

UL 94 V−0 @ 0.125 in

364

Table 9. MAXIMUM RATINGS (Note 7)

Symbol

Parameter

Condition 1

Condition 2

Rating

Units

VCC

VEE

VI

VINPP

IIN

Positive Power Supply

Negative Power Supply

Positive Input

Negative Input

Differential Input Voltage |Dn − Dn|

Input Current Through RT (50 W Resistor)

VEE = 0 V

VCC = 0 V

VEE = 0 V

VCC = 0 V

VCC − VEE w 2.8 V

VCC − VEE < 2.8 V

Static

Surge

VI v VCC

VI w VEE

3.6

−3.6

3.6

−3.6

2.8

|VCC − VEE|

45

80

V

V

V

V

V

V

mA

mA

Iout Output Current

Continuous

Surge

25 mA

50 mA

TA Operating Temperature Range

16−FCBGA

16−QFN

−40 to +70

−40 to +85

°C

°C

Tstg Storage Temperature Range

qJA Thermal Resistance (Junction−to−Ambient) 0 LFPM

(Note 8)

500 LFPM

0 LFPM

500 LFPM

16 FCBGA

16 FCBGA

16 QFN

16 QFN

−65 to +150

108

86

41.6

35.2

°C

°C/W

°C/W

°C/W

°C/W

qJC

Thermal Resistance (Junction−to−Case)

2S2P (Note 8)

2S2P (Note 9)

16 FCBGA

16 QFN

5.0 °C/W

4.0 °C/W

Tsol Wave Solder

Pb (BGA) < 15 sec

Pb (QFN) < 3 sec @ 248°C

Pb−Free (QFN) < 3 sec @ 260°C

225 °C

265

265

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the

Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect

device reliability.

7. Maximum Ratings are those values beyond which device damage may occur.

8. JEDEC standard multilayer board − 2S2P (2 signal, 2 power).

9. JEDEC standard multilayer board − 2S2P (2 signal, 2 power) with 8 filled thermal vias under exposed pad.

http://onsemi.com

5

5 Page

NBSG86A

300

200

100

0

−100

−200

−300

−400

−500

−600

−700

VCC

VCC − 400

VCC − 800

VOLS (mV)

VCC − 1200

VEE

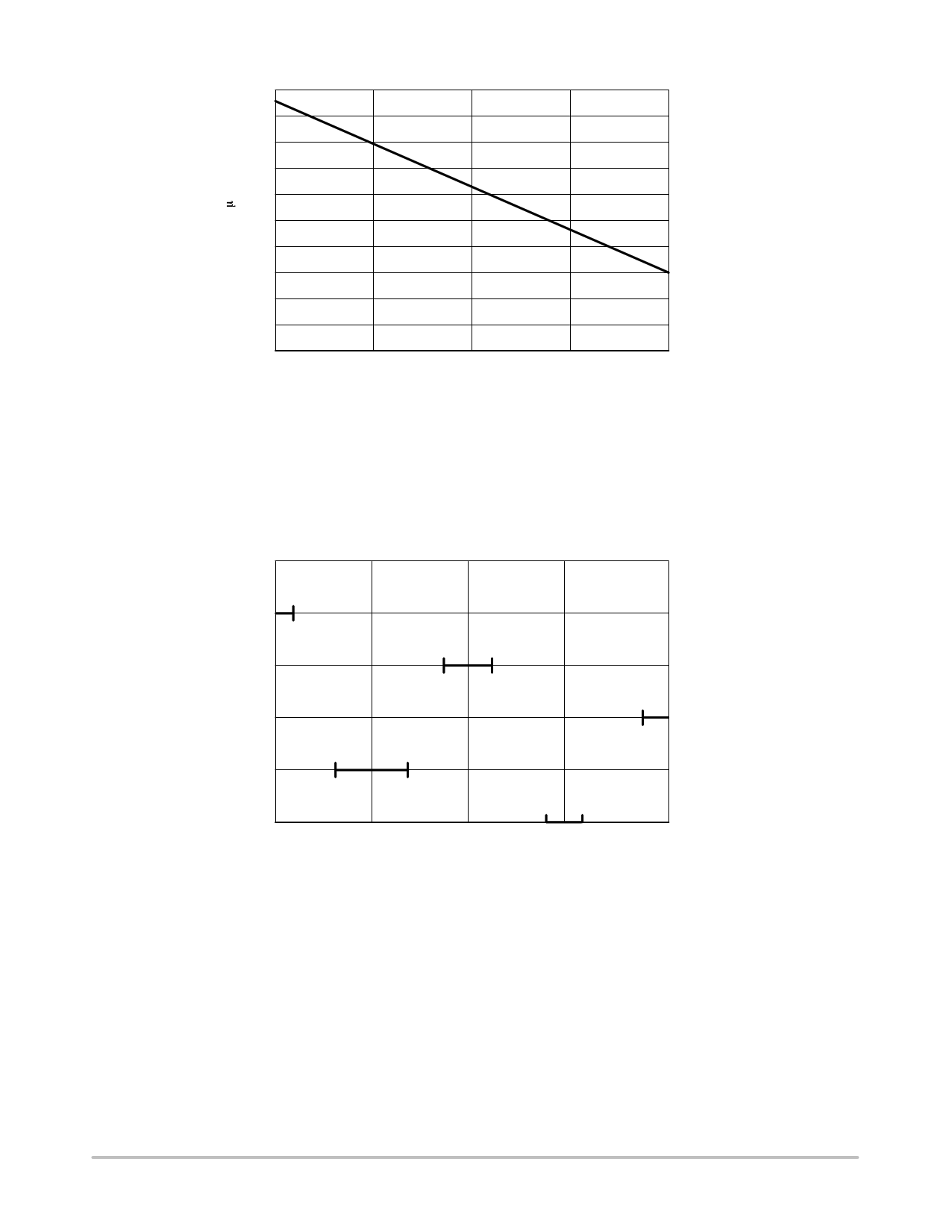

Figure 10. Typical OLS Input Current vs. OLS Input Voltage

(VCC − VEE = 3.3 V @ 255C)

1000

VCC − 75

800

600

400

VCC − 700 VCC − 900

VEE + 100

VCC − 250 VCC − 550

200

0

VCC

VCC − 400

VCC − 1125 VCC − 1275

VCC − 800

OLS (mV)

VCC − 1200

VEE

Figure 11. OLS Operating Area

http://onsemi.com

11

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet NBSG86A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NBSG86A | 2.5V/3.3V SiGe Differential Smart Gate | ON Semiconductor |

| NBSG86ABAEVB | Evaluation Board Manual | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |