|

|

PDF NIMD6302R2 Data sheet ( Hoja de datos )

| Número de pieza | NIMD6302R2 | |

| Descripción | HDPlus Dual N-Channel Self-protected Field Effect Transistors | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NIMD6302R2 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

NIMD6302R2

HDPlus Dual N−Channel

Self−protected Field Effect

Transistors with 1:200

Current Mirror FET

HDPlus devices are an advanced HDTMOS™ series of power

MOSFET which utilize ON’s latest MOSFET technology process to

achieve the lowest possible on−resistance per silicon area while

incorporating smart features. They are capable of withstanding high

energy in the avalanche and commutation modes. The avalanche

energy is specified to eliminate guesswork in designs where inductive

loads are switched and offer additional safety margin against

unexpected voltage transients.

This HDPlus device features an integrated Gate−to−Source clamp

for ESD protection. Also, this device features a mirror FET for current

monitoring.

• ±3.5% Current Mirror Accuracy in Linear Region

• ±15% Current Mirror Accuracy in Low Current Saturation Region

• IDSS Specified at Elevated Temperature

• Avalanche Energy Specified

• Current Sense FET

• ESD Protected on the Main and the Mirror FET

ABSOLUTE MAXIMUM RATINGS

www.DataSheet4U.com

Stresses beyond those listed may cause permanent damage to the device.

These are stress ratings only and functional operation of the device at these

or any other conditions beyond those indicated in this specification is not

implied. Exposure to absolute maximum rated conditions for extended peri-

ods may affect device reliability.

MAIN MOSFET MAXIMUM RATINGS (TJ = 25°C unless otherwise noted)

Rating

Symbol Value Unit

Drain−to−Source Voltage

Drain−to−Gate Voltage (RGS = 1.0 MW)

Gate−to−Source Voltage

Drain Current

− Continuous @ TA = 25°C

− Continuous @ TA = 100°C (Note 3)

− Pulsed (tpv10 ms)

Total Power Dissipation @ TA = 25°C (Note 1)

Total Power Dissipation @ TA = 25°C (Note 2)

Thermal Resistance

Junction−to−Ambient (Note 1)

Junction−to−Ambient (Note 2)

Single Pulse Drain−to−Source Avalanche

Energy (Note 3)

(VDD = 25 Vdc, VGS = 10 Vdc,

VDS = 20 Vdc, IL = 15 Apk, L = 10 mH, RG =

25 W)

VDSS

VDGR

VGS

ID

ID

IDM

PD

PD

RqJA

RqJA

EAS

30

30

"16

Vdc

Vdc

Vdc

6.5 Adc

4.4 Adc

33 Apk

1.3 W

1.67

°C/W

96

75

250 mJ

1. Mounted onto min pad board.

2. Mounted onto 1″ pad board.

3. Switching characteristics are independent of operating junction tempera-

tures.

http://onsemi.com

5.0 AMPERES

30 VOLTS

RDS(on) = 50 mW

ISOLATED DUAL PACKAGING

Drain1

Drain2

Gate1

Mirror Main

FET

Gate2

Mirror Main

FET

Mirror1 Source1

Mirror2 Source2

SOIC−8

CASE 751

STYLE 19

MARKING DIAGRAM

Source 1

Gate 1

Source 2

Gate 2

1

2

3

4

8

Mirror 1

7

Drain 1

6

Mirror 2

5

Drain 2

(Top View)

N6302

A

Y

WW

= Specific Device Code

= Assembly Location

= Year

= Work Week

ORDERING INFORMATION

Device

Package

Shipping

NIMD6302R2

SOIC−8 2500/Tape & Reel

© Semiconductor Components Industries, LLC, 2006

March, 2006 − Rev. 4

1

Publication Order Number:

NIMD6302R2/D

1 page

NIMD6302R2

POWER MOSFET SWITCHING

Switching behavior is most easily modeled and predicted

by recognizing that the power MOSFET is charge

controlled. The lengths of various switching intervals (Dt)

are determined by how fast the FET input capacitance can

be charged by current from the generator.

The published capacitance data is difficult to use for

calculating rise and fall because drain−gate capacitance

varies greatly with applied voltage. Accordingly, gate

charge data is used. In most cases, a satisfactory estimate of

average input current (IG(AV)) can be made from a

rudimentary analysis of the drive circuit so that

t = Q/IG(AV)

During the rise and fall time interval when switching a

resistive load, VGS remains virtually constant at a level

known as the plateau voltage, VSGP. Therefore, rise and fall

times may be approximated by the following:

tr = Q2 x RG/(VGG − VGSP)

tf = Q2 x RG/VGSP

where

VGG = the gate drive voltage, which varies from zero to VGG

RG = the gate drive resistance

and Q2 and VGSP are read from the gate charge curve.

During the turn−on and turn−off delay times, gate current is

not constant. The simplest calculation uses appropriate

values from the capacitance curves in a standard equation for

voltage change in an RC network. The equations are:

td(on) = RG Ciss In [VGG/(VGG − VGSP)]

td(off) = RG Ciss In (VGG/VGSP)

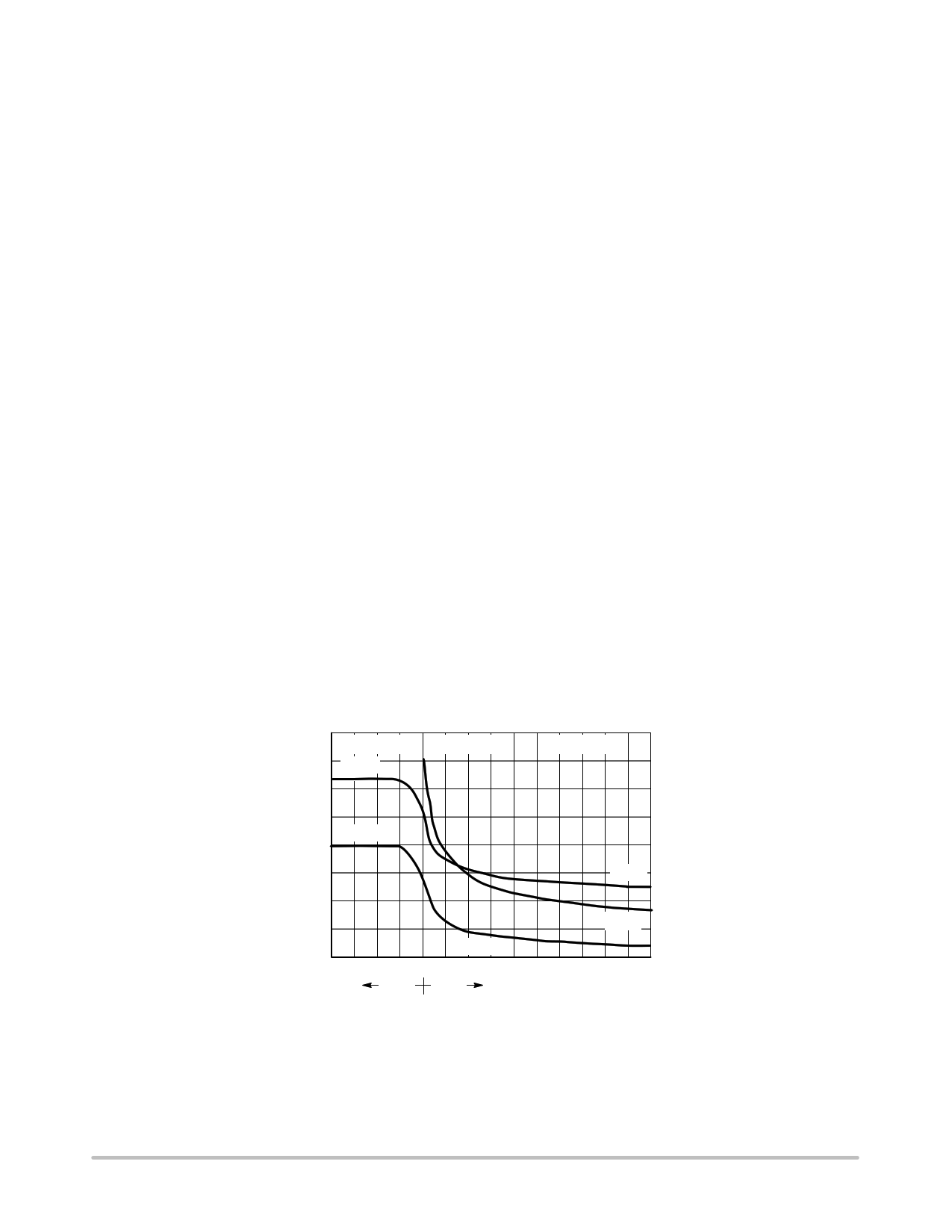

The capacitance (Ciss) is read from the capacitance curve at

a voltage corresponding to the off−state condition when

calculating td(on) and is read at a voltage corresponding to the

on−state when calculating td(off).

At high switching speeds, parasitic circuit elements

complicate the analysis. The inductance of the MOSFET

source lead, inside the package and in the circuit wiring

which is common to both the drain and gate current paths,

produces a voltage at the source which reduces the gate drive

current. The voltage is determined by Ldi/dt, but since di/dt

is a function of drain current, the mathematical solution is

complex. The MOSFET output capacitance also

complicates the mathematics. And finally, MOSFETs have

finite internal gate resistance which effectively adds to the

resistance of the driving source, but the internal resistance

is difficult to measure and, consequently, is not specified.

The resistive switching time variation versus gate

resistance (Figure 9) shows how typical switching

performance is affected by the parasitic circuit elements. If

the parasitics were not present, the slope of the curves would

maintain a value of unity regardless of the switching speed.

The circuit used to obtain the data is constructed to minimize

common inductance in the drain and gate circuit loops and

is believed readily achievable with board mounted

components. Most power electronic loads are inductive; the

data in the figure is taken with a resistive load, which

approximates an optimally snubbed inductive load. Power

MOSFETs may be safely operated into an inductive load;

however, snubbing reduces switching losses.

800

VGS = 0 V

Ciss

600

VDS = 0 V

TJ = 25°C

Crss

400

Ciss

200

Coss

0 Crss

−10 −5 0 5 10 15 20 25

VGS

VDS

GATE−TO−SOURCE OR DRAIN−TO−SOURCE VOLTAGE (VOLTS)

Figure 7. Capacitance Variation

http://onsemi.com

5

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet NIMD6302R2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NIMD6302R2 | HDPlus Dual N-Channel Self-protected Field Effect Transistors | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |