|

|

PDF SY100S839V Data sheet ( Hoja de datos )

| Número de pieza | SY100S839V | |

| Descripción | Pecl Clock Generation | |

| Fabricantes | Micrel Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SY100S839V (archivo pdf) en la parte inferior de esta página. Total 5 Páginas | ||

|

No Preview Available !

÷2/4, ÷4/5/6 CLOCK

GENERATION CHIP

ClockWorks™

SY100S839V

FINAL

FEATURES

DESCRIPTION

s 3.3V and 5V power supply option

The SY100S839V is a low skew ÷2/4, ÷4/5/6 clock

s 50ps output-to-output skew

s 50% duty cycle outputs

s Synchronous enable/disable

generation chip designed explicitly for low skew clock

generation applications. The internal dividers are

synchronous to each other, therefore, the common output

edges are all precisely aligned. The device can be driven

s Master Reset for synchronization

by either a differential or single-ended ECL/LVECL or, if

s Internal 75KΩ input pull-down resistors

s Available in 20-pin SOIC package

positive power supplies are used, PECL/LVPECL input

signal. In addition, by using the VBB output, a sinusoidal

source can be AC-coupled into the device. If a single-

ended input is to be used, the VBB output should be

connected to the /CLK input and bypassed to ground via

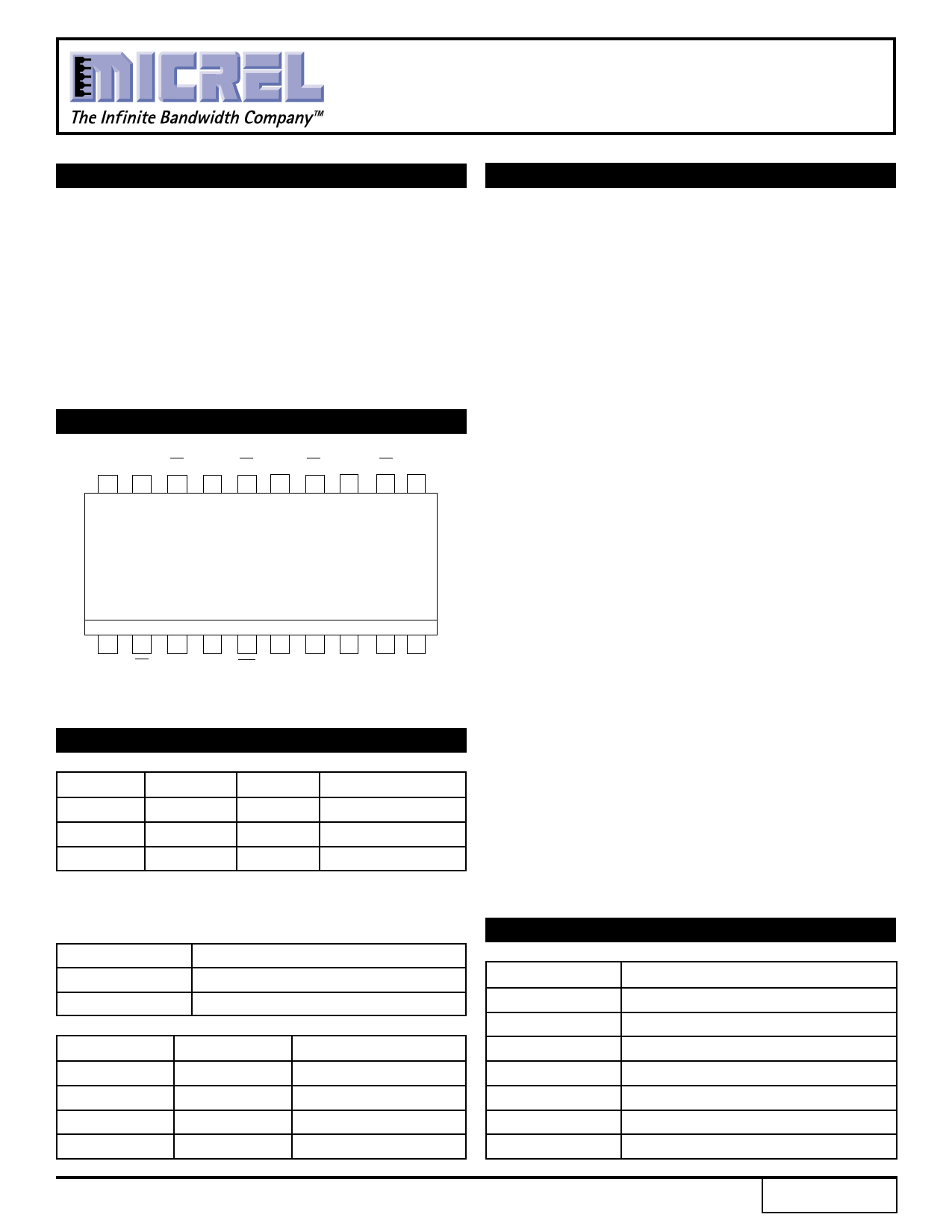

PIN CONFIGURATION/BLOCK DIAGRAM

a 0.01µF capacitor. The VBB output is designed to act as

the switching reference for the input of the S839V under

VCC Q0

Q0

Q1

Q1 Q2 Q2

Q3

20 19 18 17 16 15 14 13

Q3 VEE

12 11

single-ended input conditions. As a result, this pin can

only source/sink up to 0.5mA of current.

The common enable (/EN) is synchronous so that the

internal dividers will only be enabled/disabled when the

internal clock is already in the LOW state. This avoids

TOP VIEW

SOIC

Z20-1

any chance of generating a runt clock pulse on the

internal clock when the device is enabled/disabled as

can happen with an asynchronous control. An internal

runt pulse could lead to losing synchronization between

www.DataSheet4U.com

the internal divider stages. The internal enable flip-flop is

1 2 3 4 5 6 7 8 9 10

clocked on the falling edge of the input clock, therefore,

VCC EN

CLK CLK VBB MR VCC

all associated specification limits are referenced to the

negative edge of the clock input.

Upon start-up, the internal flip-flops will attain a

random state; the master reset (MR) input must be

TRUTH TABLE

asserted to ensure synchronization. For systems which

only use one S839V, the MR pin need not be exercised

CLK /EN MR

Function

as the internal divider designs ensures synchronization

between the ÷2/4, and the ÷4/5/6 outputs of a single

Z L L Divide

device.

ZZ H L Hold Q0–3

X X H Reset Q0–3

NOTE:

Z = LOW-to-HIGH transition

ZZ = HIGH-to-LOW transition

PIN NAMES

DIVSELa

0

1

Q0, Q1 OUTPUTS

Divide by 2

Divide by 4

Pin

CLK

/EN

Function

Differential Clock Inputs

Synchronous Enable

DIVSELb1

DIVSELb0

Q2, Q3 OUTPUTS

MR

Master Reset

0 0 Divide by 4 VBB Reference Output

0

1

Divide by 6

Q0, Q1

Differential ÷2/4 Outputs

1

0

Divide by 5

Q2, Q3

Differential ÷4/5/6 Outputs

1

1

Divide by 5

DIVSEL

Frequency Select Input

Rev.: A

Amendment: /0

1 Issue Date: May, 1999

1 page

Micrel

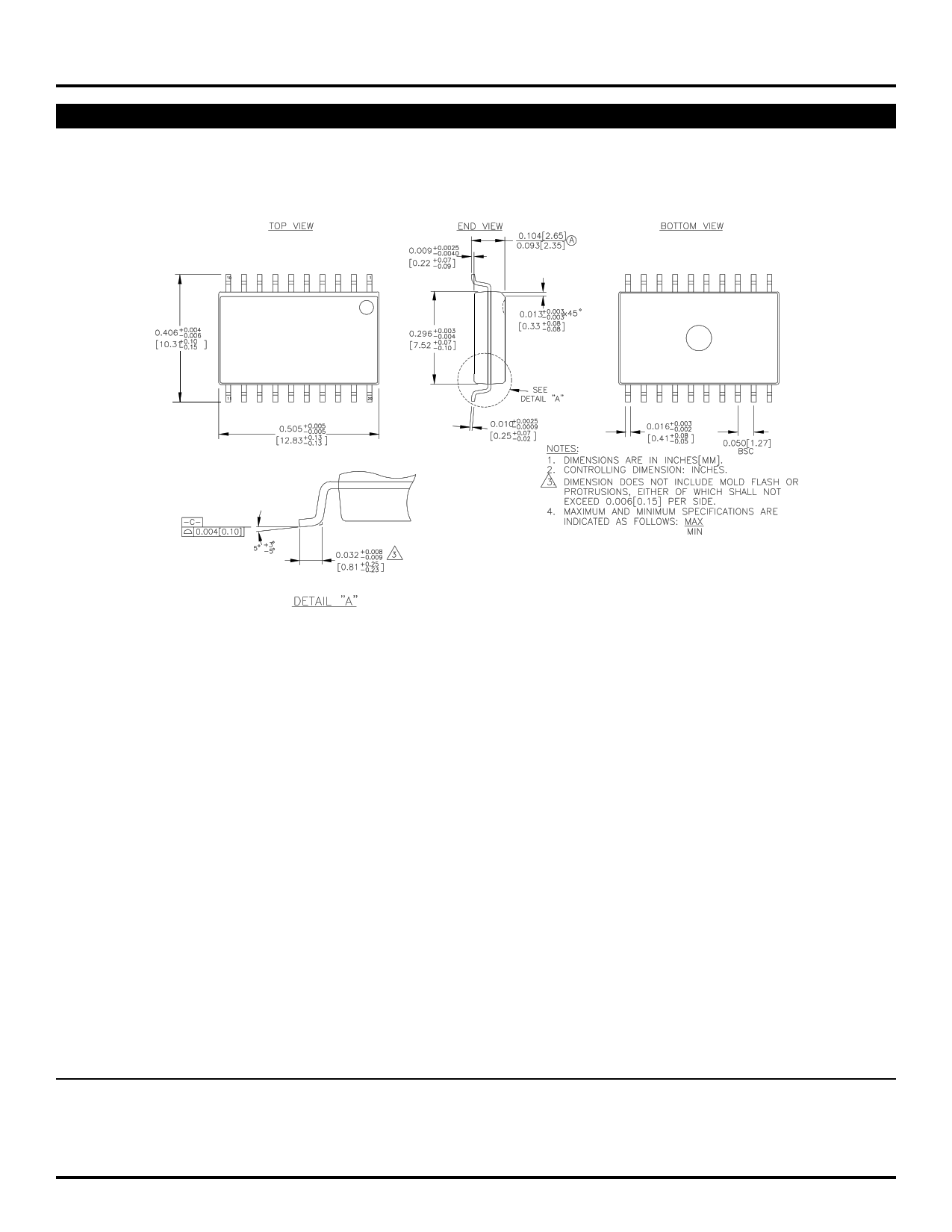

20 LEAD SOIC .300" WIDE (Z20-1)

ClockWorks™

SY100S839V

Rev. 03

MICREL-SYNERGY 3250 SCOTT BOULEVARD SANTA CLARA CA 95054 USA

TEL + 1 (408) 980-9191 FAX + 1 (408) 914-7878 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or

other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.

© 2000 Micrel Incorporated

5

5 Page | ||

| Páginas | Total 5 Páginas | |

| PDF Descargar | [ Datasheet SY100S839V.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SY100S839V | Pecl Clock Generation | Micrel Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |