|

|

PDF X9408 Data sheet ( Hoja de datos )

| Número de pieza | X9408 | |

| Descripción | Low Noise/Low Power/2-Wire Bus | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de X9408 (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

®

Data Sheet

X9408

Low Noise/Low Power/2-Wire Bus

September 19, 2005

FN8191.2

Quad Digitally Controlled (XDCP™)

Potentiometers

FEATURES

• Four potentiometers in one package

• 64 resistor taps per potentiometer

• 2-wire serial interface

• Wiper resistance, 40Ω typical at 5V

• Four nonvolatile data registers for each pot

• Nonvolatile storage of wiper position

• Standby current < 1µA max (total package)

• VCC = 2.7V to 5.5V operation

V+ = 2.7V to 5.5V

V- = –2.7V to -5.5V

• 10kΩ, 2.5kΩ end to end resistances

• High reliability

—Endurance–100,000 data changes per bit per

register

—Register data retention–100 years

• 24 Ld SOIC, 24 Ld TSSOP, 24 Ld PDIP packages

• Pb-free plus anneal available (RoHS compliant)

DESCRIPTION

The X9408 integrates four digitally controlled

potentiometers (XDCP) on a monolithic CMOS

integrated circuit.

The digital controlled potentiometer is implemented

using 63 resistive elements in a series array. Between

each element are tap points connected to the wiper

terminal through switches. The position of the wiper on

the array is controlled by the user through the 2-wire

bus interface. Each potentiometer has associated with

it a volatile Wiper Counter Register (WCR) and four

non-volatile Data Registers that can be directly written

to and read by the user. The contents of the WCR

controls the position of the wiper on the resistor array

though the switches. Powerup recalls the contents of

the default data register (DR0) to the WCR.

The XDCP can be used as a three-terminal

potentiometer or as a two terminal variable resistor in

a wide variety of applications including control,

parameter adjustments, and signal processing.

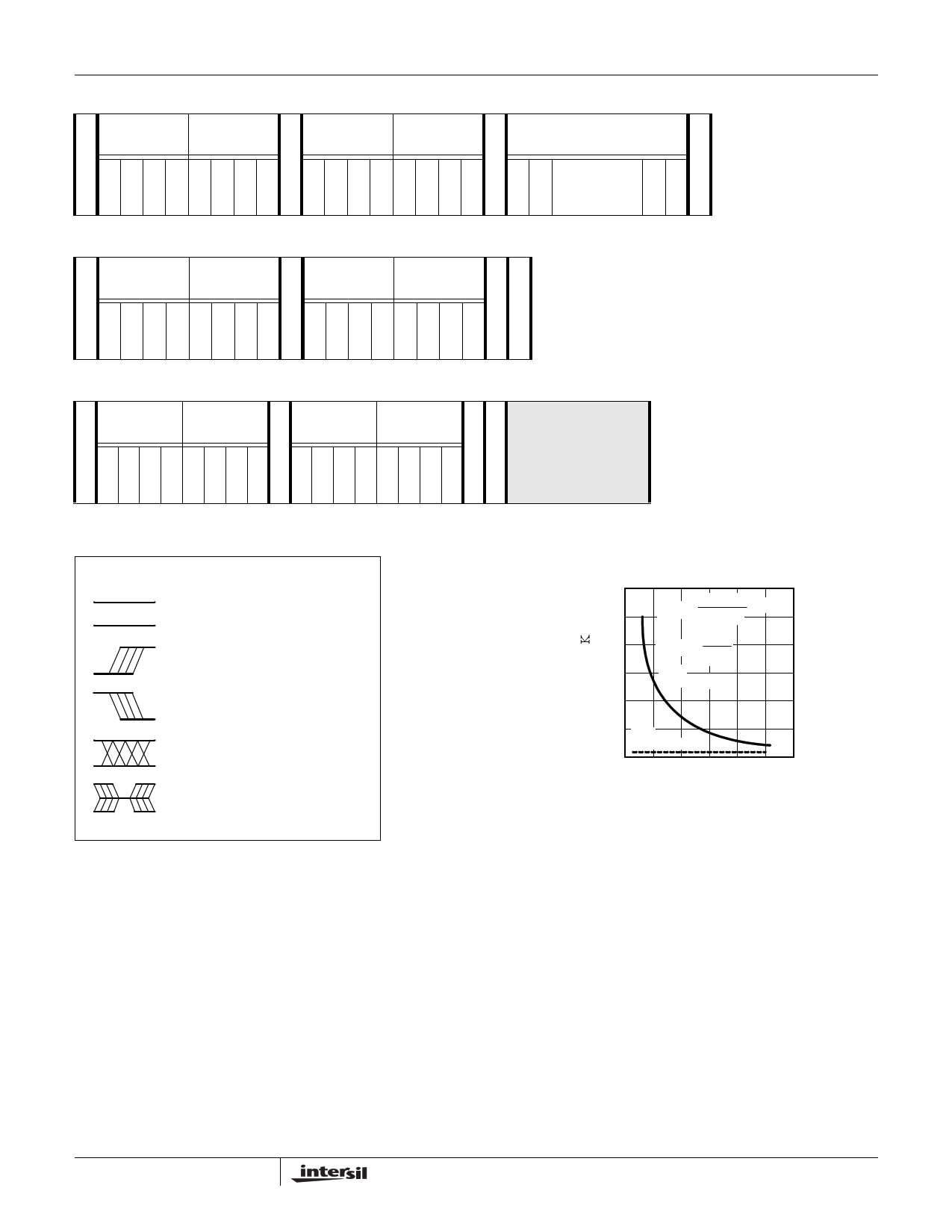

BLOCK DIAGRAM

www.DataSheet4U.com

VCC

VSS

V+

V-

WP

SCL

SDA

A0

A1

A2

A3

Interface

and

Control

Circuitry

8

Data

Pot 0

R0 R1

R2 R3

Wiper

Counter

Register

(WCR)

VH0/RH0

VL0/RL0

VW0/RW0

R0 R1

R2 R3

Wiper

Counter

Register

(WCR)

Resistor

Array

Pot 2

VH2/RH2

VL2/RL2

VW2/RW2

R0 R1

R2 R3

Wiper

Counter

Register

(WCR)

VW1/RW1

Resistor

Array

Pot 1

VH1/RH1

VL1/RL1

R0 R1

R2 R3

Wiper

Counter

Register

(WCR)

VW3/RW3

Resistor

Array

Pot 3

VH3/RH3

VL3/RL3

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

XDCP is a trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2005. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

X9408

Acknowledge Polling

The disabling of the inputs, during the internal

Nonvolatile write operation, can be used to take

advantage of the typical 5ms EEPROM write cycle

time. Once the stop condition is issued to indicate the

end of the nonvolatile write command the X9408

initiates the internal write cycle. ACK polling can be

initiated immediately. This involves issuing the start

condition followed by the device slave address. If the

X9408 is still busy with the write operation no ACK will

be returned. If the X9408 has completed the write

operation an ACK will be returned and the master can

then proceed with the next operation.

Flow 1. ACK Polling Sequence

Nonvolatile Write

Command Completed

Enter ACK Polling

Issue

START

Issue Slave

Address

ACK

Returned?

YES

NO

Further

Operation?

YES

Issue

Instruction

NO

Issue STOP

Issue STOP

Proceed

Proceed

Instruction Structure

The next byte sent to the X9408 contains the instruction

and register pointer information. The four most

significant bits are the instruction. The next four bits

point to one of the two pots and when applicable they

point to one of four associated registers. The format is

shown below in Figure 2.

Figure 2. Instruction Byte Format

Register

Select

I3 I2 I1 I0 R1 R0 P1 P0

Instructions

Wiper Counter

Register Select

The four high order bits define the instruction. The

next two bits (R1 and R0) select one of the four

registers that is to be acted upon when a register

oriented instruction is issued. The last bits (P1, P0)

select which one of the four potentiometers is to be

affected by the instruction.

Four of the nine instructions end with the transmission

of the instruction byte. The basic sequence is

illustrated in Figure 3. These two-byte instructions

exchange data between the Wiper Counter Register

and one of the Data Registers. A transfer from a Data

Register to a Wiper Counter Register is essentially a

write to a static RAM. The response of the wiper to this

action will be delayed tWRL. A transfer from the Wiper

Counter Register (current wiper position), to a data

register is a write to nonvolatile memory and takes a

minimum of tWR to complete. The transfer can occur

between one of the four potentiometers and one of its

associated registers; or it may occur globally, wherein

the transfer occurs between all of the potentiometers

and one of their associated registers.

Four instructions require a three-byte sequence to

complete. These instructions transfer data between

the host and the X9408; either between the host and

one of the data registers or directly between the host

and the Wiper Counter Register. These instructions

are: Read Wiper Counter Register (read the current

wiper position of the selected pot), Write Wiper

Counter Register (change current wiper position of the

selected pot), Read Data Register (read the contents

of the selected nonvolatile register) and Write Data

Register (write a new value to the selected Data

Register). The sequence of operations is shown in

Figure 4.

5 FN8191.2

September 19, 2005

5 Page

X9408

Increment/Decrement Wiper Counter Register (WCR)

S device type

T identifier

device

addresses

S

A

instruction

opcode

WCR

addresses

S

A

increment/decrement

(sent by master on SDA)

S

T

A

R

T

0

1

0

1

A

3

A

2

A

1

A

0

C

K

0

0

1

0

0

0

P

1

P

0

C I/ I/

KDD

.

.

.

.

I/ I/ O

DDP

Global XFR Data Register (DR) to Wiper Counter Register (WCR)

S device type

T identifier

device

addresses

S

instruction

opcode

DR

addresses

SS

A

R

T

0

1

0

1

A

3

A

2

A

1

A

0

A

C

K

0

0

0

1

R

1

R

0

0

0

AT

CO

KP

Global XFR Wiper Counter Register (WCR) to Data Register (DR)

S device type device S instruction

DR S S

T

A

R

T

identifier

0101

addresses

AAAA

3210

A

C

K

opcode

1000

addresses

R

1

R

0

0

0

A

C

K

T

O

P

HIGH-VOLTAGE

WRITE CYCLE

SYMBOL TABLE

WAVEFORM INPUTS

OUTPUTS

Must be

steady

May change

from Low to

High

May change

from High to

Low

Don’t Care:

Changes

Allowed

N/A

Will be

steady

Will change

from Low to

High

Will change

from High to

Low

Changing:

State Not

Known

Center Line

is High

Impedance

Guidelines for Calculating Typical Values of Bus

Pull-Up Resistors

120

100

RMIN = VIOCLCMMINAX=1.8kΩ

80

RMAX

=

tR

CBUS

60 Max.

Resistance

40

20 Min.

Resistance

0

0 20 40 60

80 100 120

Bus Capacitance (pF)

11 FN8191.2

September 19, 2005

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet X9408.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| X9400 | Quad Digitally Controlled Potentiometers (XDCP) | Xicor |

| X9400 | Quad Digitally Controlled Potentiometers | Intersil Corporation |

| X9401 | Digitally Controlled Potentiometer | Intersil Corporation |

| X9408 | Low Noise/Low Power/2-Wire Bus | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |