|

|

PDF AT25512 Data sheet ( Hoja de datos )

| Número de pieza | AT25512 | |

| Descripción | SPI Serial EEPROM | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT25512 (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

Features

• Serial Peripheral Interface (SPI) Compatible

• Supports SPI Modes 0 (0,0) and 3 (1,1)

• Data Sheet Describes Mode 0 Operation

• Low-voltage Operation

– 1.8 (VCC = 1.8V to 5.5V)

• 20 MHz Clock Rate (4.5 – 5.5V)

• 128-byte Page Mode and Byte Write Operation Supported

• Block Write Protection

– Protect 1/4, 1/2, or Entire Array

• Write Protect (WP) Pin and Write Disable Instructions for

Both Hardware and Software Data Protection

• Self-timed Write Cycle (5 ms Max)

• High-reliability

– Endurance: 1 Million Write Cycles

– Data Retention: >40 Years

• Lead-free/Halogen-free Devices

• 8-lead JEDEC SOIC, 8-lead TSSOP and 8-lead SAP Packages

• Die Sales: Wafer Form, Waffle Pack, and Bumped Die

SPI Serial

EEPROM

512K (65,536 x 8)

AT25512

Description

The AT25512 provides 524,288 bits of serial electrically-erasable programmable read

only memory (EEPROM) organized as 65,536 words of 8 bits each. The device is opti-

mized for use in many industrial and commercial applications where low-power and

low-voltage operation are essential. The devices are available in space saving 8-lead

JEDEC SOIC, 8-lead TSSOP and 8-lead SAP packages. In addition, the entire family

is available in 1.8V (1.8V to 5.5V) versions.

The AT25512 is enabled through the Chip Select pin (CS) and accessed via a 3-wire

interface consisting of Serial Data Input (SI), Serial Data Output (SO), and Serial

Clock (SCK). All programming cycles are completely self-timed, and no separate

Erase cycle is required before Write.

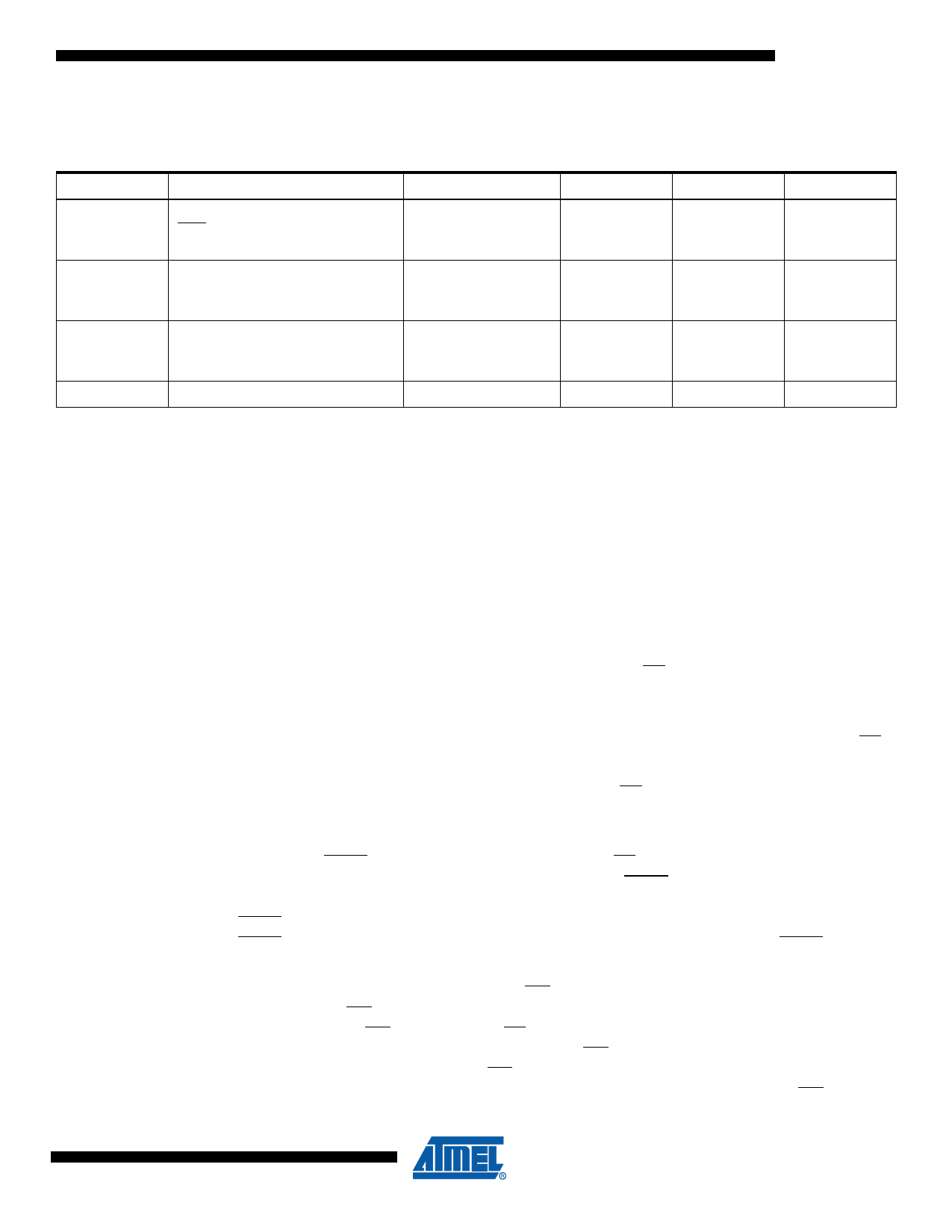

Table 0-1.

Pin Name

CS

SCK

SI

SO

GND

VCC

WP

HOLD

NC

Pin Configurations

Function

Chip Select

Serial Data Clock

Serial Data Input

Serial Data Output

Ground

Power Supply

Write Protect

Suspends Serial Input

No Connect

8-lead SOIC

CS

SO

WP

GND

1

2

3

4

8 VCC

7 HOLD

6 SCK

5 SI

8-lead TSSOP

CS 1

SO 2

WP 3

GND 4

8 VCC

7 HOLD

6 SCK

5 SI

8-lead SAP

VCC 8

HOLD 7

SCK 6

SI 5

1 CS

2 SO

3 WP

4 GND

Bottom View

5165G–SEEPR–9/09

1 page

AT25512

Table 1-3. AC Characteristics (Continued)

Applicable over recommended operating range from TAI = –40⋅ C to + 85⋅ C, VCC = As Specified,

CL = 1 TTL Gate and 30 pF (unless otherwise noted)

Symbol

Parameter

Voltage

Min Max

tHZ Hold to Output High Z

4.5–5.5

2.7–5.5

1.8–5.5

25

50

100

tDIS Output Disable Time

4.5–5.5

2.7–5.5

1.8–5.5

25

50

100

tWC Write Cycle Time

4.5–5.5

2.7–5.5

1.8–5.5

5

5

5

Endurance(1) 5.0V, 25⋅ C, Page Mode

1M

Notes: 1. This parameter is characterized and is not 100% tested. Contact Atmel for further information.

Units

ns

ns

ms

Write Cycles

2. Serial Interface Description

MASTER: The device that generates the serial clock.

SLAVE: Because the serial clock pin (SCK) is always an input, the AT25512 always operates

as a slave.

TRANSMITTER/RECEIVER: The AT25512 has separate pins designated for data transmission

(SO) and reception (SI).

MSB: The Most Significant Bit (MSB) is the first bit transmitted and received.

SERIAL OP-CODE: After the device is selected with CS going low, the first byte will be

received. This byte contains the op-code that defines the operations to be performed.

INVALID OP-CODE: If an invalid op-code is received, no data will be shifted into the AT25512,

and the serial output pin (SO) will remain in a high impedance state until the falling edge of CS is

detected again. This will reinitialize the serial communication.

CHIP SELECT: The AT25512 is selected when the CS pin is low. When the device is not

selected, data will not be accepted via the SI pin, and the serial output pin (SO) will remain in a

high impedance state.

HOLD: The HOLD pin is used in conjunction with the CS pin to select the AT25512. When the

device is selected and a serial sequence is underway, HOLD can be used to pause the serial

communication with the master device without resetting the serial sequence. To pause, the

HOLD pin must be brought low while the SCK pin is low. To resume serial communication, the

HOLD pin is brought high while the SCK pin is low (SCK may still toggle during HOLD). Inputs to

the SI pin will be ignored while the SO pin is in the high impedance state.

WRITE PROTECT: The write protect pin (WP) will allow normal read/write operations when held

high. When the WP pin is brought low and WPEN bit is “1”, all write operations to the status reg-

ister are inhibited. WP going low while CS is still low will interrupt a write to the status register. If

the internal write cycle has already been initiated, WP going low will have no effect on any write

operation to the status register. The WP pin function is blocked when the WPEN bit in the status

register is “0”. This will allow the user to install the AT25512 in a system with the WP pin tied to

5165G–SEEPR–9/09

5

5 Page

Figure 4-3. WRDI Timing

AT25512

Figure 4-4. RDSR Timing

CS

SCK

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

SI INSTRUCTION

HIGH IMPEDANCE

SO

Figure 4-5. WRSR Timing

DATA OUT

76543210

MSB

5165G–SEEPR–9/09

11

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet AT25512.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT25512 | SPI Serial EEPROM | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |