|

|

PDF XR16C2450 Data sheet ( Hoja de datos )

| Número de pieza | XR16C2450 | |

| Descripción | 2.97V TO 5.5V DUART | |

| Fabricantes | Exar Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XR16C2450 (archivo pdf) en la parte inferior de esta página. Total 31 Páginas | ||

|

No Preview Available !

xrwww.DataSheet4U.com

DECEMBER 2004

GENERAL DESCRIPTION

The XR16C2450 (2450) is a dual universal asynchro-

nous receiver and transmitter (UART). The

XR16C2450 is an improved version of the

XR16C2450 with lower operating voltage and 5 volt

tolerant inputs. The 2450 provides enhanced UART

functions, a modem control interface and data rates

up to 1.5 Mbps. Onboard status registers provide the

user with error indications and operational status. In-

dependent programmable baud rate generators are

provided to select transmit and receive clock rates up

to 1.5 Mbps. An internal loopback capability allows

onboard diagnostics. The 2450 is available in a 44-

pin PLCC and 48-pin TQFP packages. The 2450 is

fabricated in an advanced CMOS process capable of

operating from 2.97 volt to 5.5 volt power supply with

5 volt tolerant inputs.

APPLICATIONS

• Portable Appliances

• Telecommunication Network Routers

• Ethernet Network Routers

• Cellular Data Devices

• Factory Automation and Process Controls

XR16C2450

2.97V TO 5.5V DUART

FEATURES

REV. 1.0.0

• 2.97 to 5.5 Volt Operation

• 5 Volt Tolerant Inputs

• Pin-to-pin compatible to Exar’s XR16C2450,

ST16C2550, XR16L2550, XR16L2750 and

XR16C2850

• Pin-to-pin compatible to TI’s TL16C752B on the 48-

TQFP package

• 2 independent UART channels

■ Up to 1.5 Mbps data rate with a 24 MHz crystal

oscillator or external clock frequency

■ 1 byte Transmit FIFO

■ 1 byte Receive FIFO with error tags

■ Status report registers

■ Modem control signals (CTS#, RTS#, DSR#,

DTR#, RI#, CD#)

■ Programmable character lengths (5, 6, 7, 8)

with even, odd, or no parity

• Crystal oscillator or external clock input

• TTL compatible inputs, outputs

• Industrial temperature ranges

• 48-TQFP and 44-PLCC packages

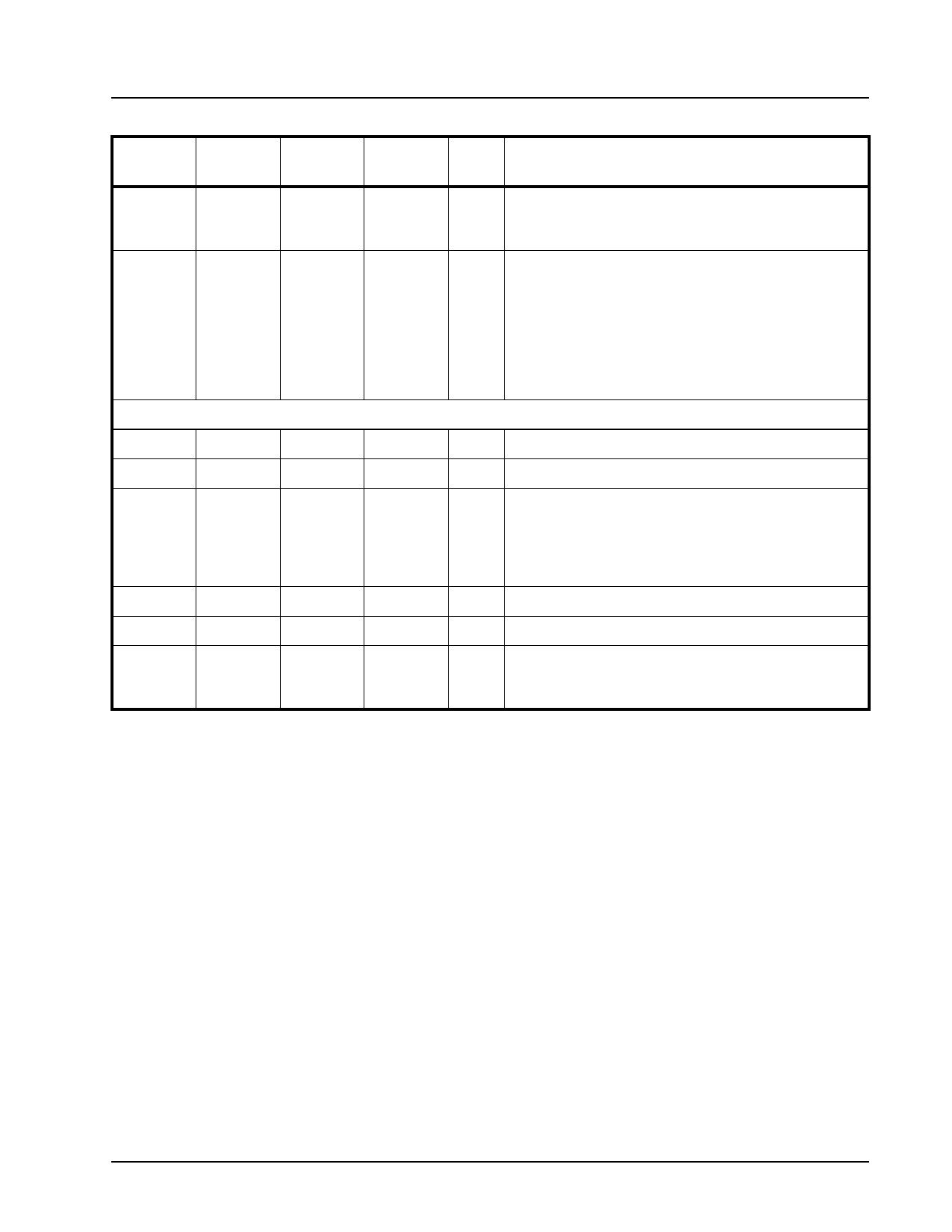

FIGURE 1. XR16C2450 BLOCK DIAGRAM

A2:A0

D7:D0

IOR#

IOW#

CSA#

CSB#

INTA

INTB

Reset

8-bit Data

Bus

Interface

*5V Tolerant inputs

UART Channel A

UART

Regs

THR

RHR

BRG

Modem I/Os

UART Channel B

(same as Channel A)

Crystal Osc/Buffer

2.97 to 5.5 Volt VCC

TXA

RXA

RTSA#, CTSA#,

DTRA#, DSRA#,

CDA#, RIA#, OP2A#

TXB

RXB

RTSB#, CTSB#,

DTRB#, DSRB#,

CDB#, RIB#, OP2B#

XTAL1

XTAL2

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

xr

REV. 1.0.0

Pin Description

NAME

40-PDIP

PIN #

RIB#

23

OP2B#

13

ANCILLARY SIGNALS

XTAL1

16

XTAL2

17

RESET

35

VCC

GND

N.C.

40

20

-

XR16C2450

2.97V TO 5.5V DUART

44-PLCC

PIN #

26

15

48-TQFP

PIN #

21

9

TYPE

DESCRIPTION

I UART channel B Ring-Indicator (active low) or general

purpose input. This input should be connected to VCC

when not used. This input has no effect on the UART.

O Output Port 2 Channel B - The output state is defined by

the user and through the software setting of MCR[3].

INTB is set to the active mode and OP2B# output to a

logic 0 when MCR[3] is set to a logic 1. INTB is set to the

three state mode and OP2B# to a logic 1 when MCR[3] is

set to a logic 0. This output should not be used as a gen-

eral output else it will disturb the INTB output functionality.

If it is not used, leave it unconnected.

18 13

19 14

39 36

44

22

1, 12, 23,

34

42

17

6, 12, 18,

24, 25, 31,

37, 43

I Crystal or external clock input.

O Crystal or buffered clock output.

I Reset (active high) - A longer than 40 ns logic 1 pulse on

this pin will reset the internal registers and all outputs. The

UART transmitter output will be held at logic 1, the

receiver input will be ignored and outputs are reset during

reset period.

Pwr 2.97V to 5.5V power supply. All inputs are 5V tolerant.

Pwr Power supply common, ground.

- No Connection.

Pin type: I=Input, O=Output, IO= Input/output, OD=Output Open Drain.

5

5 Page

xr

REV. 1.0.0

XR16C2450

2.97V TO 5.5V DUART

2.10 Internal Loopback

The 2450 UART provides an internal loopback capability for system diagnostic purposes. The internal

loopback mode is enabled by setting MCR register bit-4 to logic 1. All regular UART functions operate normally.

Figure 7 shows how the modem port signals are re-configured. Transmit data from the transmit shift register

output is internally routed to the receive shift register input allowing the system to receive the same data that it

was sending. The TX pin is held at logic 1 or mark condition while RTS# and DTR# are de-asserted, and

CTS#, DSR# CD# and RI# inputs are ignored. Caution: the RX input must be held to a logic 1 during loopback

test else upon exiting the loopback test the UART may detect and report a false “break” signal.

FIGURE 7. INTERNAL LOOP BACK IN CHANNELS A AND B

VCC

Transmit Shift Register

(THR/FIFO)

MCR bit-4=1

Receive Shift Register

(RHR/FIFO)

VCC

RTS#

CTS#

VCC

DTR#

DSR#

RI#

OP1#

VCC

OP2#

CD#

TXA/TXB

RXA/RXB

RTSA#/RTSB#

CTSA#/CTSB

DTRA#/DTRB#

DSRA#/DSRB#

RIA#/RIB#

OP2A#/OP2B#

CDA#/CDB#

11

11 Page | ||

| Páginas | Total 31 Páginas | |

| PDF Descargar | [ Datasheet XR16C2450.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XR16C2450 | 2.97V TO 5.5V DUART | Exar Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |