|

|

PDF 92HD71B7 Data sheet ( Hoja de datos )

| Número de pieza | 92HD71B7 | |

| Descripción | 4-CHANNEL HD AUDIO CODEC OPTIMIZED | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 92HD71B7 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATASHEET

4-CHANNEL HD AUDIO CODEC OPTIMIZED FOR

LOW POWER

92HD71B7

Description

The 92HD71B7 codec is a low power optimized, high

fidelity, 4-channel audio codec compatible with Intel’s High

Definition (HD) Audio Interface. The 92HD71B7 codec

provides stereo 24-bit resolution with sample rates up to

192kHz. Dual SPDIF provides connectivity to consumer

electronic equipment that is WLP complaint. The

92HD71B7 provides high quality, HD Audio capability to

notebook and business desktop PC applications.

Features

• 4 Channels (2 stereo DACs and 2 stereo ADCs) with

24-bit resolution

• Supports full-duplex stereo audio and simultaneous VoIP

• Provides a mono output for laptop sub-woofer

• Microsoft WLP 3/4 premium logo compliant, as

defined in WLP 3.09

• Optimized and flexible power management with

pop/click mitigation

• 2 independent S/PDIF Output converters for WLP

compliant HDMI/SPDIF support.

• Support for 1.5V and 3.3V HDA signaling with

runtime selection

• Digital microphone input (mono, stereo, or quad

array)

• 3 Adjustable VREF Out pins for microphone bias

• High performance analog mixer option

• 6 analog ports

• Supports to 3 stereo microphone inputs

• Two-pin volume up/down control

• Digital PC Beep to all outputs

• Integrated headphone amp

• Jack insertion detection

• Sample rates up to 192kHz

• +3.3 V, +4 V, +4.75 V and +5 V analog power supply

options

• 48-pin QFP and 48-pad QFN RoHS packages

Block Diagram

X

DUAL SPDIF

Port A

Port B

Port C

Port D

Port E

Port F

SPDIF Out 1

SPDIF Out 2

4-CHANNEL HD AUDIO CODEC OPTIMIZED FOR LOW POWER

1

92HD71B7

V 1.0, 01/08

1 page

92HD71B7

4-CHANNEL HD AUDIO CODEC OPTIMIZED FOR LOW POWER

PC AUDIO

8.8.2. PortF PinCap .....................................................................................................................85

8.8.3. PortF ConLst ......................................................................................................................86

8.8.4. PortF ConLstEntry0 ...........................................................................................................86

8.8.5. PortF ConSelectCtrl ...........................................................................................................87

8.8.6. PortF PinWCntrl .................................................................................................................87

8.8.7. PortF UnsolResp ................................................................................................................87

8.8.8. PortF ChSense ..................................................................................................................88

8.8.9. PortF InAmpLeft .................................................................................................................88

8.8.10. PortF InAmpRight ............................................................................................................89

8.8.11. PortF ConfigDefault .........................................................................................................89

8.9. DAC0 Node (NID = 10) ....................................................................................................................91

8.9.1. DAC0 WCap ......................................................................................................................91

8.9.2. DAC0 Cnvtr ........................................................................................................................92

8.9.3. DAC0 OutAmpLeft .............................................................................................................93

8.9.4. DAC0 OutAmpRight ...........................................................................................................93

8.9.5. DAC0 PwrState ..................................................................................................................94

8.9.6. DAC0 CnvtrID ....................................................................................................................94

8.9.7. DAC0 LR ............................................................................................................................95

8.10. DAC1 Node (NID = 11) ..................................................................................................................95

8.10.1. DAC1 WCap ....................................................................................................................95

8.10.2. DAC1 Cnvtr ......................................................................................................................97

8.10.3. DAC1 OutAmpLeft ...........................................................................................................98

8.10.4. DAC1 OutAmpRight .........................................................................................................98

8.10.5. DAC1 PwrState ................................................................................................................99

8.10.6. DAC1 CnvtrID ..................................................................................................................99

8.10.7. DAC1 LR ........................................................................................................................100

8.11. ADC0 Node (NID = 12) ................................................................................................................100

8.11.1. ADC0 WCap ..................................................................................................................100

8.11.2. ADC0 ConLst .................................................................................................................101

8.11.3. ADC0 ConLstEntry0 .......................................................................................................102

8.11.4. ADC0 Cnvtr ....................................................................................................................102

8.11.5. ADC0 ProcState .............................................................................................................103

8.11.6. ADC0 PwrState ..............................................................................................................104

8.11.7. ADC0 CnvtrID ................................................................................................................104

8.12. ADC1 Node (NID = 13) ................................................................................................................105

8.12.1. ADC1 WCap ..................................................................................................................105

8.12.2. ADC1 ConLst .................................................................................................................106

8.12.3. ADC1 ConLstEntry0 .......................................................................................................107

8.12.4. ADC1 Cnvtr ....................................................................................................................107

8.12.5. ADC1 ProcState .............................................................................................................108

8.12.6. ADC1 PwrState ..............................................................................................................109

8.12.7. ADC1 CnvtrID ................................................................................................................109

8.13. MonoOut Node (NID = 14) ...........................................................................................................110

8.13.1. MonoOut WCap .............................................................................................................110

8.13.2. MonoOut PinCap ...........................................................................................................111

8.13.3. MonoOut ConLst ............................................................................................................112

8.13.4. MonoOut ConLstEntry0 .................................................................................................112

8.13.5. MonoOut PinWCntrl .......................................................................................................113

8.13.6. MonoOut InAmpLeft .......................................................................................................113

8.13.7. MonoOut ConfigDefault .................................................................................................114

8.14. MonoMux Node (NID = 15) ..........................................................................................................115

8.14.1. MonoMux WCap ............................................................................................................115

8.14.2. MonoMux ConLst ...........................................................................................................116

8.14.3. MonoMux ConLstEntry0 ................................................................................................117

8.14.4. MonoMux ConSelectCtrl ................................................................................................117

4-CHANNEL HD AUDIO CODEC OPTIMIZED FOR LOW POWER

5

92HD71B7

V 1.0, 01/08

5 Page

92HD71B7

4-CHANNEL HD AUDIO CODEC OPTIMIZED FOR LOW POWER

PC AUDIO

1.2. Orderable Part numbers

92HD71B7X5PRGXyyX

6port, 95dB, 5V, 48QFP

92HD71B7X5NLGXyyX

6port, 95dB, 5V, 48QFN

92HD71B7X3PRGXyyX

6port, 95dB, 3.3V, 48QFP

92HD71B7X3NLGXyyX

6port, 95dB, 3.3V, 48QFN

yy = silicon stepping/revision, contact sales for current data.

Add an “8” to the end for tape and reel delivery. Min/Mult order quantitiy 2ku.

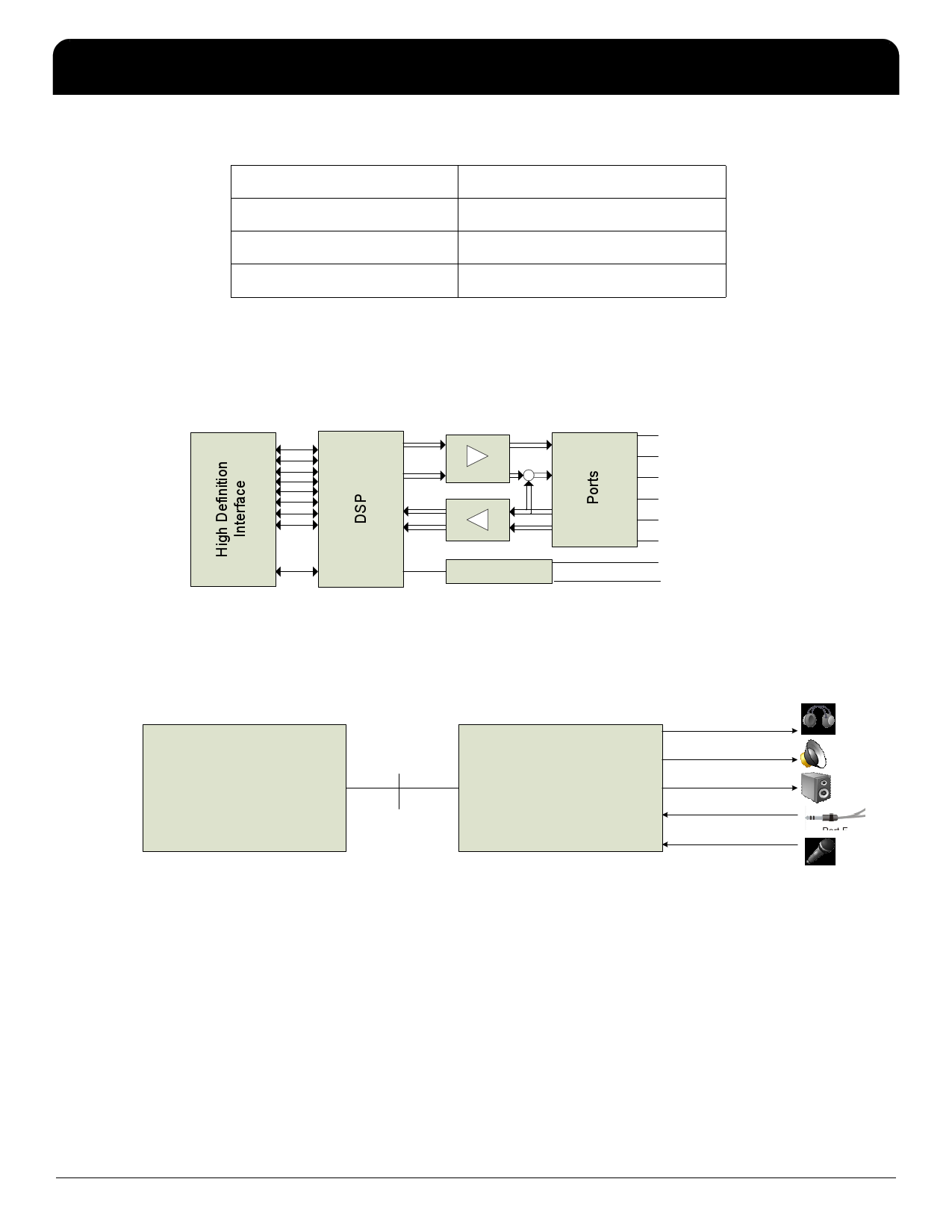

1.3. Block Diagram

Figure 1. 92HD71B7 Block Diagram

X

DUAL SPDIF

Port A

Port B

Port C

Port D

Port E

Port F

SPDIF Out 1

SPDIF Out 2

Figure 2. System Diagram

I/O Controller Hub (ICH)

HD Audio Bus

92HD71B

Head Phone

Speakers

Sub Woofer

Line In

Microphone

4-CHANNEL HD AUDIO CODEC OPTIMIZED FOR LOW POWER

11

92HD71B7

V 1.0, 01/08

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 92HD71B7.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 92HD71B5 | 4-CHANNEL HD AUDIO CODEC OPTIMIZED | IDT |

| 92HD71B7 | 4-CHANNEL HD AUDIO CODEC OPTIMIZED | IDT |

| 92HD71B8 | 4-CHANNEL HD AUDIO CODEC OPTIMIZED | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |