|

|

PDF N16D1633LPA Data sheet ( Hoja de datos )

| Número de pieza | N16D1633LPA | |

| Descripción | 512K X 16 Bits X 2 Banks Low Power Synchronous DRAM | |

| Fabricantes | NanoAmp Solutions | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de N16D1633LPA (archivo pdf) en la parte inferior de esta página. Total 27 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

NanoAmp Solutions, Inc.

670 North McCarthy Blvd. Suite 220, Milpitas, CA 95035

ph: 408-935-7777, FAX: 408-935-7770

www.nanoamp.com

N16D1633LPA

Advance Information

512K × 16 Bits × 2 Banks Low Power Synchronous DRAM

DESCRIPTION

These N16D1633LPA are low power 16,777,216 bits CMOS Synchronous DRAM organized as 2 banks of 524,288

words x 16 bits. These products are offering fully synchronous operation and are referenced to a positive edge of the

clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths are internally

pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL.

Features

• JEDEC standard 3.0V/3.3V power supply.

• Auto refresh and self refresh.

• All pins are compatible with LVTTL interface.

• 4K refresh cycle / 64ms.

• Programmable Burst Length and Burst Type.

- 1, 2, 4, 8 or Full Page for Sequential Burst.

- 4 or 8 for Interleave Burst.

• Programmable CAS Latency : 2,3 clocks.

• Programmable Driver Strength Control.

- Full Strength or 1/2, 1/4 of Full Strength

• Deep Power Down Mode

• All inputs and outputs referenced to the positive

edge of the system clock.

• Data mask function by DQM.

• Internal dual banks operation.

• Burst Read Single Write operation.

• Special Function Support.

-PASR (Partial Array Self Refresh)

-Auto TCSR(Temperature Compensated Self Refresh)

• Automatic precharge, includes CONCURRENT

Auto Precharge Mode and controlled Precharge

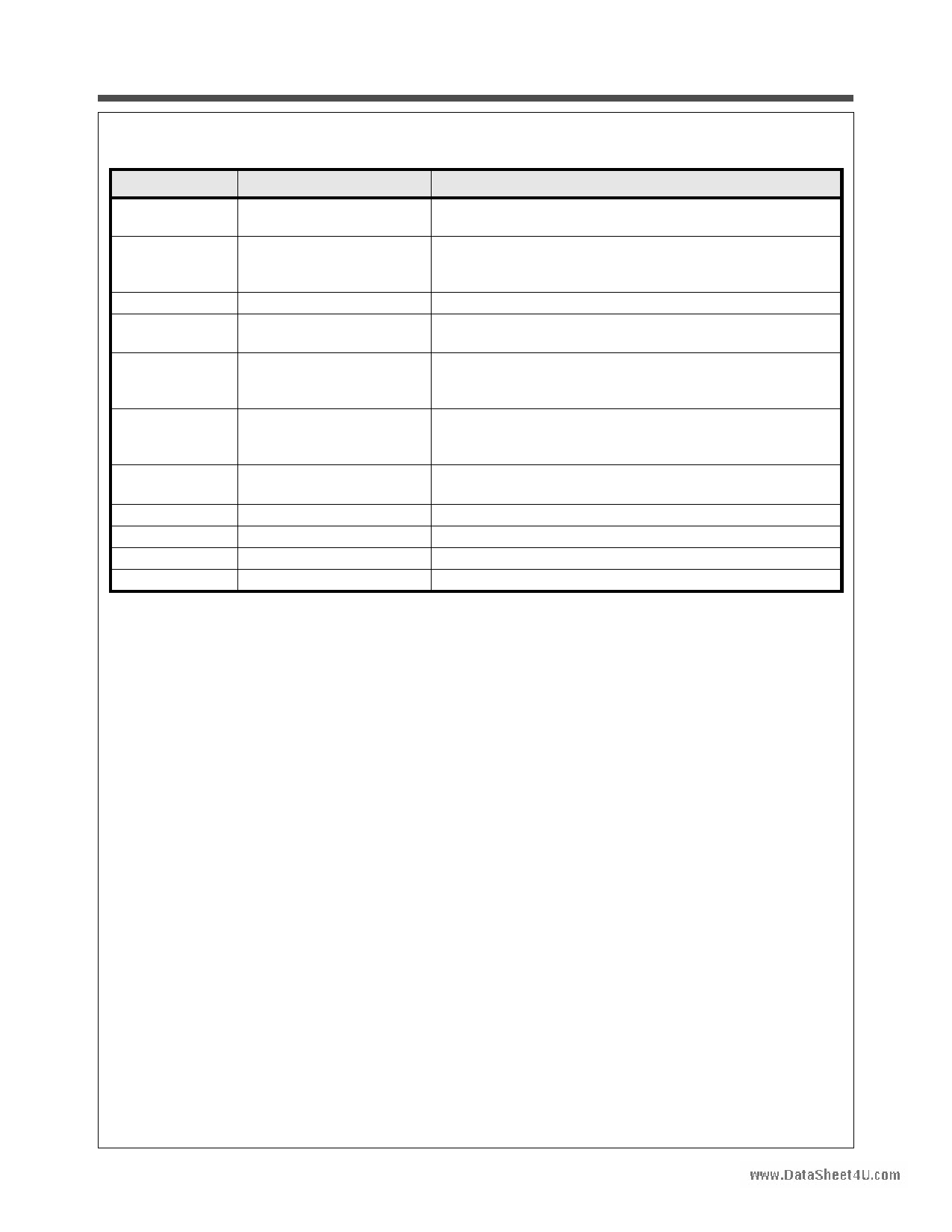

Table 1: Ordering Information

PART NO.

N16D1633LPAZ2-75I

N16D1633LPAZ2-10I

N16D1633LPAC2-60I

N16D1633LPAC2-75I

N16D1633LPAC2-10I

N16D1633LPAT2-60I

N16D1633LPAT2-75I

N16D1633LPAT2-10I

CLOCK Freq.

133MHz

100MHz

166MHz

133MHz

100MHz

166MHz

133MHz

100MHz

Temperature

-25o C to

85o C

VDD/VDDQ

3.0V/3.0V

or

3.3V/3.3V

INTERLEAVE

LVTTL

PACKAGE

48-Ball Green

FBGA

60-Ball Green

WBGA

50-Pin Green

TSOP II

Stock No. 23395- Rev L 1/06

The specifications of this device are subject to change without notice. For latest documentation see http://www.nanoamp.com.

1

1 page

www.DataSheet4U.com

NanoAmp Solutions, Inc.

N16D1633LPA

Advance Information

Table 2: Pin Descriptions

PIN

CLK

CKE

/CS

A11

A0~A10

/RAS, /CAS, /WE

LDQM/UDQM

DQ0~DQ15

VDD/VSS

VDDQ/VSSQ

NC

PIN NAME

System Clock

Clock Enable

Chip Select

Bank Address

Address

Row Address Strobe,

Column Address Strobe,

Write Enable

Data Input/Output Mask

Data Input/Output

Power Supply/Ground

Data Output Power/Ground

No Connection

DESCRIPTIONS

The system clock input. All other inputs are registered to the

SDRAM on the rising edge of the CLK

Controls internal clock signal and when deactivated, the

SDRAM will be one of the states among power down, suspend

or self refresh.

Enable or disable all inputs except CLK, CKE and DQM

Selects bank to be activated during /RAS activity

Selects bank to be read/written during /CAS activity

Row Address : RA0~RA10

Column Address: CA0~CA7

Auto Precharge : A10

/RAS, /CAS and /WE define the operation

Refer function truth table for details

Controls output buffers in read mode and masks input data in

write mode

Multiplexed data input/output pin

Power supply for internal circuits and input buffers

Power Supply for output buffers

No Connection

Stock No. 23395- Rev L 1/06

The specifications of this device are subject to change without notice. For latest documentation see http://www.nanoamp.com.

5

5 Page

www.DataSheet4U.com

NanoAmp Solutions, Inc.

N16D1633LPA

Advance Information

Burst Length

Read and write accesses to the SDRAM are burst oriented, with the burst length being programmable, as shown in

Figure 1. The burst length determines the maximum number of column locations that can be accessed for a given

READ or WRITE command. Burst lengths of 1, 2, 4 or 8 locations are available for both the sequential and the

interleaved burst types, and a full-page burst is available for the sequential type. The full-page burst is used in

conjunction with the BURST TERMINATE command to generate arbitrary burst lengths.

Reserved states should not be used, as unknown operation or incompatibility with future versions may result. When a

READ or WRITE command is issued, a block of columns equal to the burst length is effectively selected. All accesses

for that burst take place within this block, meaning that the burst will wrap within the block if a boundary is reached. The

block is uniquely selected by A1-A7 when the burst length is set to two; by A2-A7 when the burst length is set to four;

and by A3-A7 when the burst length is set to eight. The remaining (least significant) address bit(s) is (are) used to

select the starting location within the block. Full-page bursts wrap within the page if the boundary is reached.

Bank(Row) Active

The Bank Active command is used to activate a row in a specified bank of the device. This command is initiated by

activating /CS, /RAS and deasserting /CAS, /WE at the positive edge of the clock. The value on the A11 selects the

bank, and the value on the A0-A10 selects the row. This row remains active for column access until a precharge

command is issued to that bank. Read and write operations can only be initiated on this activated bank after the

minimum tRCD time is passed from the activate command.

Read

The READ command is used to initiate the burst read of data. This command is initiated by activating /CS, /CAS, and

deasserting /WE, /RAS at the positive edge of the clock. A11 input select the bank, A0-A7 address inputs select the

starting column location. The value on input A10 determines whether or not Auto Precharge is used. If Auto Precharge

is selected the row being accessed will be precharged at the end of the READ burst; if Auto Precharge is not selected,

the row will remain active for subsequent accesses. The length of burst and the CAS latency will be determined by the

values programmed during the MRS command.

Write

The WRITE command is used to initiate the burst write of data. This command is initiated by activating /CS, /CAS, /WE

and deasserting /RAS at the positive edge of the clock. A11 input select the bank, A0-A7 address inputs select the

starting column location. The value on input A10 determines whether or not Auto Precharge is used. If Auto Precharge

is selected the row being accessed will be precharged at the end of the WRITE burst; if Auto Precharge is not selected,

the row will remain active for subsequent accesses.

Stock No. 23395- Rev L 1/06

The specifications of this device are subject to change without notice. For latest documentation see http://www.nanoamp.com.

11

11 Page | ||

| Páginas | Total 27 Páginas | |

| PDF Descargar | [ Datasheet N16D1633LPA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| N16D1633LPA | 512K X 16 Bits X 2 Banks Low Power Synchronous DRAM | NanoAmp Solutions |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |