|

|

PDF ML145502 Data sheet ( Hoja de datos )

| Número de pieza | ML145502 | |

| Descripción | (ML145502 - ML145505) PCM Codec-Filter Mono-Circuit | |

| Fabricantes | LANSDALE Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ML145502 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

ML145502

ML145503

ML145505

PCM Codec–Filter Mono–Circuit

Legacy Device: Motorola MC145502, MC145503, MC145505

The ML145502, ML145503, and ML145505 are all per channel PCM

Codec–Filter mono–circuits. These devices perform the voice digitization

and reconstruction as well as the band limiting and smoothing required

for PCM systems. The ML145503 is a general purpose device that is

offered in a 16–pin package. These are designed to operate in both syn-

chronous and asynchronous applications and contain an on–chip preci-

sion reference voltage. The ML145505 is a synchronous device offered in

a 16–pin DIP and wide body SOIC package intended for instrument use.

The ML145502 is the full–featured device which presents all of the

options of the chip. This device is packaged in a 22–pin DIP and a

28–pin chip carrier package

These devices are pin–for–pin replacements for Motorola’s first genera-

tion of MC14400/01/02/03/05 PCM mono–circuits and are upwardly

compatible with the MC14404/06/07 codecs and other industry standard

codecs. They also maintain compatibility with Motorola’s family of

MC33120 and MC3419 SLIC products.

The ML1455xx family of PCM Codec–Filter mono–circuits utilizes

CMOS due to its reliable low–power performance and proven capability

for complex analog/digital VLSI functions.

ML145502

• 22 Pin and 28 Pin Packages

• Transmit Bandpass and Receive Low–Pass Filter On–Chip

• Pin Selectable Mu–Law/A–Law Companding with Corresponding

Data Format

• On–Chip Precision Reference Voltage (3.15 V)

• Power Dissipation of 50 mW, Power–Down of 0.1 mW at ±5 V

• Automatic Prescaler Accepts 128 kHz, 1.536, 1.544, 2.048, and 2.56

MHz for Internal Sequencing

• Selectable Peak Overload Voltages (2.5, 3.15, 3.78 V)

• Access to the Inverting Input of the TxI Input Operational Amplifier

• Variable Data Clock Rates (64 kHz to 4.1 MHz)

• Complete Access to the Three Terminal Transmit Input Operational

Amplifiers

• An External Precision Reference May Be Used

ML145503— Similar to the ML145502 Plus:

• 16–Pin Dip and SOIC 16 Packages

• Complete Access to the Three Terminal Transmit Input Operational

Amplifiers

ML145505 — Somewhat Similar To ML145503 Except:

• Common 64 kHz to 4.1 MHz Transmit/Receive Data Clock

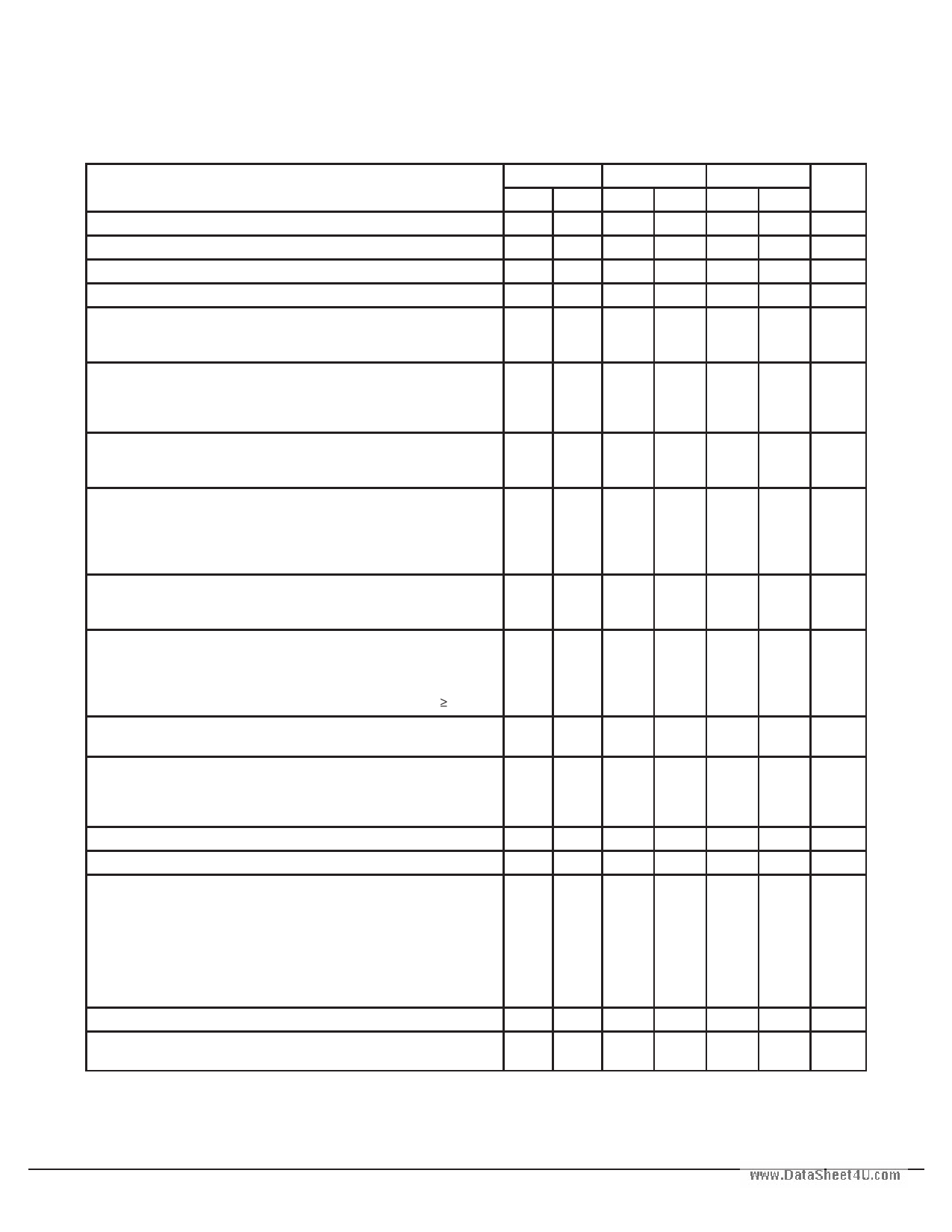

16

1

P DIP 16 = EP

PLASTIC DIP

CASE 648

22

1

P DIP 22 = WP

PLASTIC DIP

CASE 708

16

1

SOG 16 = -5P

SOG PACKAGE

CASE 751G

PLCC 28 = -4P

PLCC PACKAGE

CASE 776

28 1

CROSS REFERENCE/ORDERING INFORMATION

PACKAGE

MOTOROLA

LANSDALE

P DIP 22

PLCC 28

P DIP 16

SO 16W

MC145502P

MC145502FN

MC145503P

MC145503DW

ML145502WP

ML145502-4P

ML145503EP

ML145503-5P

P DIP 16

SO 16W

MC145505P ML145505EP

MC145505DW ML145505-5P

Note: Lansdale lead free (Pb) product, as it

becomes available, will be identified by a part

number prefix change from ML to MLE.

Page 1 of 26

www.lansdale.com

Issue A

1 page

ML145502, ML145503, ML145505

www.DataSheet4U.com

LANSDALE Semiconductor, Inc.

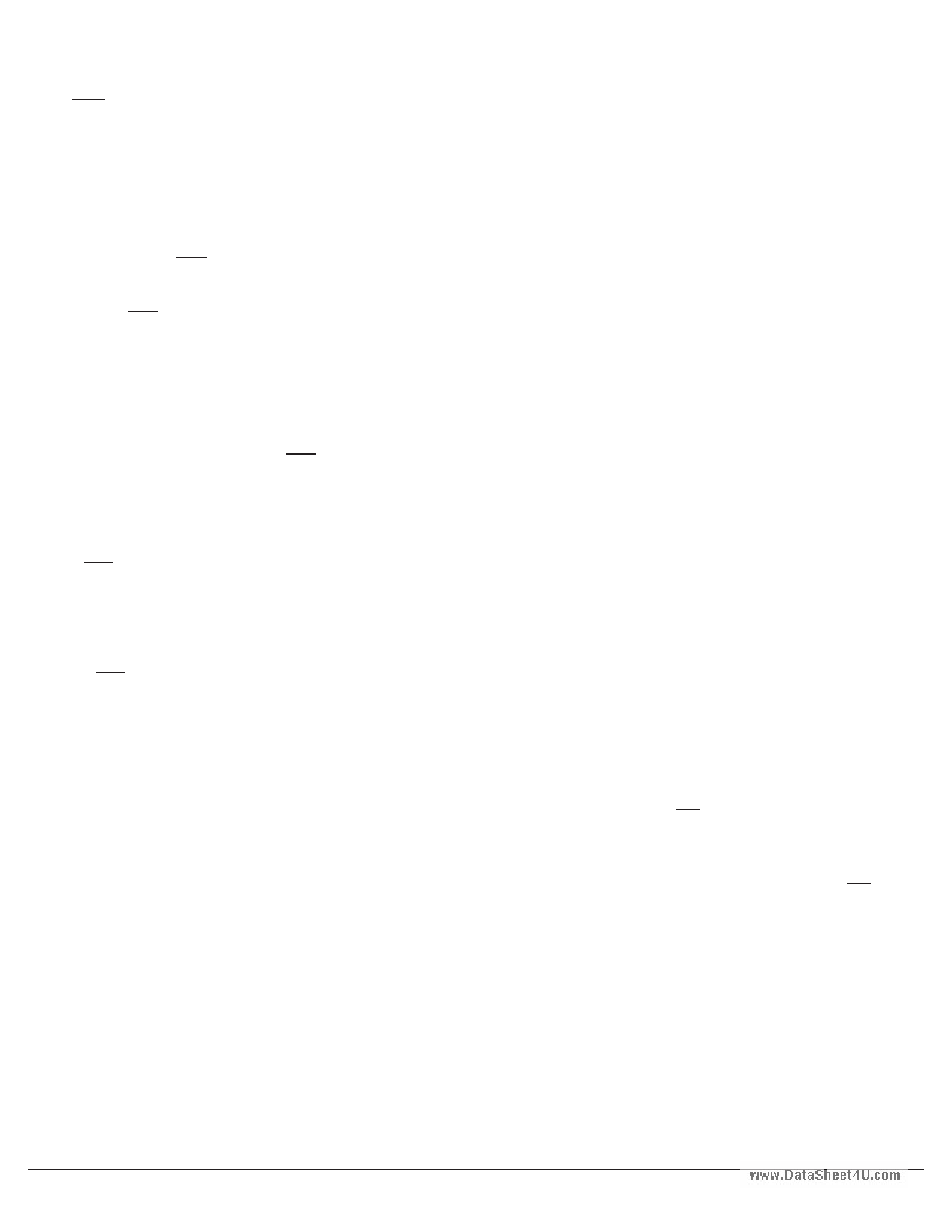

ANALOG TRANSMISSION PERFORMANCE

(VDD = + 5 V ± 5%, VSS = – 5 V ± 5%, VLS = VAG = 0 V, Vref = RSI = VSS (Internal 3.15 V Reference), 0 dBm0 = 1.546 Vrms = + 6 dBm @

600 Ω, TA = – 40 to + 85°C, TDC = RDC = CC = 2.048 MHz, TDE = RCE = MSI = 8 kHz, Unless Otherwise Noted)

End–to–End

A/D

D/A

Characteristic

Min Max Min Max Min Max Unit

Absolute Gain (0 dBm0 @ 1.02 kHz, TA = 25°C, VDD = 5 V, VSS = – 5 V)

Absolute Gain Variation with Temperature 0 to + 70°C

—

—

— – 0.30 + 0.30 – 0.30 + 0.30

— — ± 0.03 — ± 0.03

dB

dB

Absolute Gain Variation with Temperature – 40 to +85°C

— — — ± 0.1 — ± 0.1 dB

Absolute Gain Variation with Power Supply (VDD = 5 V, VSS = – 5 V, 5%)

Gain vs Level Tone (Relative to – 10 dBm0, 1.02 kHz) + 3 to – 40 dBm0

– 40 to – 50 dBm0

– 50 to – 55 dBm0

—

– 0.4

– 0.8

– 1.6

—

+ 0.4

+ 0.8

+ 1.6

—

– 0.2

– 0.4

– 0.8

± 0.02

+ 0.2

+ 0.4

+ 0.8

—

– 0.2

– 0.4

– 0.8

± 0.02

+ 0.2

+ 0.4

+ 0.8

dB

dB

Gain vs Level Pseudo Noise (A–Law Relative to – 10 dBm0)

CCITT G.714

– 10 to – 40 dBm0

– 40 to – 50 dBm0

– 50 to – 55 dBm0

—

—

—

— – 0.25 + 0.25 – 0.25 + 0.25

— – 0.30 + 0.30 – 0.30 + 0.30

— – 0.45 + 0.45 – 0.45 + 0.45

dB

Total Distortion – 1.02 kHz Tone (C–Message)

0 to – 30 dBm0 35

—

36

—

36

— dBC

– 40 dBm0 29

—

29

—

30

—

– 45 dBm0 24

—

24

—

25

—

Total Distortion With Pseudo Noise (A–Law)

CCITT G.714

– 3 dBm0 27.5 — 28 — 28.5 —

– 6 to – 27 dBm0 35

— 35.5 —

36

—

– 34 dBm0 33.1 — 33.5 — 34.2 —

– 40 dBm0 28.2 — 28.5 — 30.0 —

– 55 dBm0 13.2 — 13.5 — 15.0 —

dB

Idle Channel Noise (For End–End and A/D, See Note 1)

Mu–Law, C–Message Weighted —

15

—

15

—

9 dBrnC0

A–Law, Psophometric Weighted — – 69 — – 69 — – 78 dBm0p

Frequency Response (Relative to 1.02 kHz @ 0 dBm0)

15 to 60 Hz

300 to 3000 Hz

3400 Hz

4000 Hz

4600 Hz

—

– 0.3

– 1.6

—

—

– 23

+ 0.3

0

– 28

– 60

—

– 0.15

– 0.8

—

—

– 23

+ 0.15

0

– 14

– 32

—

– 0.15

– 0.8

—

—

0.15

+ 0.15

0

– 14

– 30

dB

Inband Spurious (1.02 kHz @ 0 dBm0, Transmit and RxO)

— — — – 43 — – 43 dBm0

300 to 3000 Hz

Out–of–Band Spurious at RxO (300 – 3400 Hz @ 0 dBm0 In)

dB

4600 to 7600 Hz — – 30 — — — – 30

7600 to 8400 Hz — – 40 — — — – 40

8400 to 100,000 Hz — – 30 — — — – 30

Idle Channel Noise Selective @ 8 kHz, Input = VAG, 30 Hz Bandwidth

Absolute Delay @ 1600 Hz (TDC = 2.048 MHz, TDE = 8 kHz)

— – 70 — — — – 70 dBm0

— — — 310 — 180 µs

Group Delay Referenced to 1600 Hz (TDC = 2048 kHz,

µs

TDE = 8 kHz)

500 to 600 Hz — — — 200 – 40 —

600 to 800 Hz — — — 140 – 40 —

800 to 1000 Hz — — — 70 – 30 —

1000 to 1600 Hz — — — 40 – 20 —

1600 to 2600 Hz —

—

—

75

—

90

2600 to 2800 Hz — — — 110 — 120

2800 to 3000 Hz — — — 170 — 160

Crosstalk of 1020 Hz @ 0 dBm0 From A/D or D/A (Note 2)

— — — – 75 — – 80 dB

Intermodulation Distortion of Two Frequencies of Amplitudes – 4 to

– 21 dBm0 from the Range 300 to 3400 Hz

— — — – 41 — – 41 dB

NOTES:

1. Extrapolated from a 1020 Hz @ – 50 dBm0 distortion measurement to correct for encoder enhancement.

2. Selectively measured while the A/D is stimulated with 2667 Hz @ – 50 dBm0.

Page 5 of 26

www.lansdale.com

Issue A

5 Page

ML145502, ML145503, ML145505

www.DataSheet4U.com

LANSDALE Semiconductor, Inc.

RxO, RxO

Receive Analog Outputs

These two complimentary outputs are generated from the out-

put of the receive filter. They are equal in magnitude and out of

phase. The maximum signal output of each is equal to the maxi-

mum peak–to–peak signal described with the reference. If a

3.15 V reference is used with RSI tied to VAG and a + 3 dBm0

sine wave is decoded, the RxO output will be a 6.3 V

peak–to–peak signal. RxO will also have an inverted signal out-

put of 6.3 V peak–to–peak. External loads may be connected

from RxO to RxO for a 6 dB push–pull signal gain or from

either RxO or RxO to VAG. With a 3.15 V reference each output

will drive 600 Ω to + 9 dBm. With RSI tied to VDD, each out-

put will drive 900 Ω to + 9 dBm.

RxG

Receive Output Gain Adjust (ML145502 Only)

The purpose of the RxG pin is to allow external gain adjust-

ment for the RxO pin. If RxG is left open, then the output signal

at RxO will be inverted and output at RxO. Thus the push–pull

gain to a load from RxO to RxO is two times the output level at

RxO. If external resistors are applied from RxO to RxG (RI)

and from RxG to RxO (RG), the gain of RxO can be set differ-

ently from inverting unity. These resistors should be in the range

of 10 kΩ. The RxO output level is unchanged by the resistors

and the RxO gain is approximately equal to minus RG/RI. The

actual gain is determined by taking into account the internal

resistors which will be in parallel to these external resistors. The

internal resistors have a large tolerance, but they match each

other very closely. This matching tends to minimize the effects

of their tolerance on external gain configurations. The circuit for

RxG and RxO is shown in the block diagram.

Txl

Transmit Analog Input

TxI is the input to the transmit filter. It is also the output of

the transmit gain amplifiers of the ML145502/03/05. The TxI

input has an internal gain of 1.0, such that a +3 dBm0 signal at

TxI corresponds to the peak converter reference voltage as

described in the Vref and RSI pin descriptions. For 3.15 V refer-

ence, the + 3 dBm0 input should be 6.3 V peak–to–peak.

+Tx/–Tx

Positive Tx Amplifier Input

Negative Tx Amplifier Input

The Txl pin is the input to the transmit band–pass filter. If

+Tx or –Tx is available, then there is an internal amplifier pre-

ceding the filter whose pins are +Tx, –Tx, and TxI. These pins

allow access to the amplifier terminals to tailor the input gain

with external resistors. The resistors should be in the range of

10 kΩ. If +Tx is not available, it is internally tied to VAG. If

–Tx and +Tx are not available, the TxI is a unity gain

high–impedance input.

POWER SUPPLIES

VDD

Most Positive Power Supply

VDD is typically 5 to 12 V.

VSS

Most Negative Power Supply

VSS is typically 10 to 12 V negative of VDD.

For a ±5 V dual–supply system, the typical power supply con-

figuration is VDD = + 5 V, VSS = – 5 V, VLS = 0 V (digital

ground accommodating TTL logic levels), and VAG = 0 V being

tied to system analog ground.

For single–supply applications, typical power supply configu-

rations include:

VDD = 10 V to 12 V

VSS = 0 V

VAG generates a mid supply voltage for referencing all analog

signals.

VLS controls the logic levels. This pin should be connected to

VDD for CMOS logic levels from VSS to VDD. This pin should

be connected to digital ground for true TTL logic levels refer-

enced to VLS.

TESTING CONSIDERATIONS (ML145502 ONLY)

An analog test mode is activated by connecting MSI and CCI

to 128 kHz. In this mode, the input of the A/D (the output of the

Tx filter) is available at the PDI pin. This input is direct coupled

to the A/D side of the codec. The A/D is a differential design.

This results in the gain of this input being effectively attenuated

by half. If monitored with a high–impedance buffer, the output

of the Tx low–pass filter can also be measured at the PDI pin.

This test mode allows independent evaluation of the transmit

low–pass filter and A/D side of the codec. The transmit and

receive channels of these devices are tested with the codec–filter

fully functional.

Page 11 of 26

www.lansdale.com

Issue A

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet ML145502.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ML145502 | (ML145502 - ML145505) PCM Codec-Filter Mono-Circuit | LANSDALE Semiconductor |

| ML145503 | (ML145502 - ML145505) PCM Codec-Filter Mono-Circuit | LANSDALE Semiconductor |

| ML145505 | (ML145502 - ML145505) PCM Codec-Filter Mono-Circuit | LANSDALE Semiconductor |

| ML145506 | PCM Codec-Filter Mono-Circuit | LANSDALE Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |