|

|

PDF W65C51S Data sheet ( Hoja de datos )

| Número de pieza | W65C51S | |

| Descripción | Asynchronous Communications Interface Adapter | |

| Fabricantes | WDC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W65C51S (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

W65C51S

Asynchronous Communications

Interface Adapter (ACIA)

3/7/2006

1 page

STATUS REGISTER

The Status Register indicates the state of interrupt conditions

and other non-interrupt status lines. The interrupt conditions

are the Data Set Ready, Data Carrier Detect, Transmitter

Data Register Empty and Receiver Data Register Full as

reported in bits 6 through 3, respectively. If any of these bits

are set the interrupt (IRQ) indicator (bit 7) is also set.

Overrun, Framing Error and Parity Error are also reported

(bits 2 through 0 respectively).

www.DataSheet4U.com

7 6 5 4 3 2 10

IRQ DSRB DCDB TDRE RDRF OVRN FE PE

Bit 7

0

1

Interrupt (IRQ)

No Interrupt

Interrupt has occurred

Bit 6

0

1

Data Set Ready (DSRB)

DSR low (ready)

DSR high (not ready)

Bit 5

0

1

Data Carrier Detect (DCDB)

DCD low (detected)

DCD high (not detected)

Bit 4

0

1

Transmitter Data Register Empty

Not Empty

Empty

Bit 3

0

1

Receiver Data Register Full

Not full

Full

Bit 2

0

1

Overrun*

No overrun

Overrun has occurred

Bit 1

0

1

Framing Error*

No framing error

Framing error detected

Bit 0

0

1

Parity Error*

No parity error

Parity error detected

*No interrupt occurrs for these conditions

Reset Initialization

76 5 4 3 2

0- - 1 0 0

-- - - - 0

1

0

-

0

0 Hardware reset

- Program reset

Parity error (Bit 0) Framing Error (Bit 1) and Overrun

(Bit 2)

None of these bits causes a processor interrupt to occur but,

they are normally checked at the time the Receiver Data

Register is read so that the validity of the data can be

verified. These bits are self clearing (i.e., they are

automatically cleared after a read of the Receiver Data

Register).

Receiver Data Register Full (Bit 3)

This bit goes to a 1 when the ACIA transfers data from the

Receiver Shift Register to the Receiver Data Register and

goes to a 0 (is cleared) when the processor reads the Receiver

Data Register.

Transmitter Data Register Empty (Bit 4)

This bit goes to a 1 when the ACIA transfers data from the

Transmitter Data Register to the Transmitter Shift Register

and goes to a 0 (is cleared) when the processor writes new

data onto the Transmitter Data Register.

Data Carrier Detect (Bit 5) and Data Set Ready (Bit 6)

These bits reflect the levels of the DCDB and DSRB inputs

to the ACIA. A 0 indicates a low level (true condition) and a

1 indicates a high level (false). Whenever either of these

inputs change state, an immediate processor interrupt (IRQ)

occurs, unless bit 1 of the Command Register (IRD) is set to

a 1 to disable IRQB. When the interrupt occurs, the status

bits indicate the levels of the inputs immediately after the

change of state occurred. Subsequent level changes will not

affect the status bits until the Status Register is interrogated

by the processor. At that time, another interrupt will

immediately occur and the status bits reflect the new input

levels. These bits are not automatically cleared (or reset) by

an internal operation.

Interrupt (Bit 7)

This bit goes to a 1 whenever an interrupt condition occurs

and goes to a 0 (is cleared) when the Status Register is read.

5

5 Page

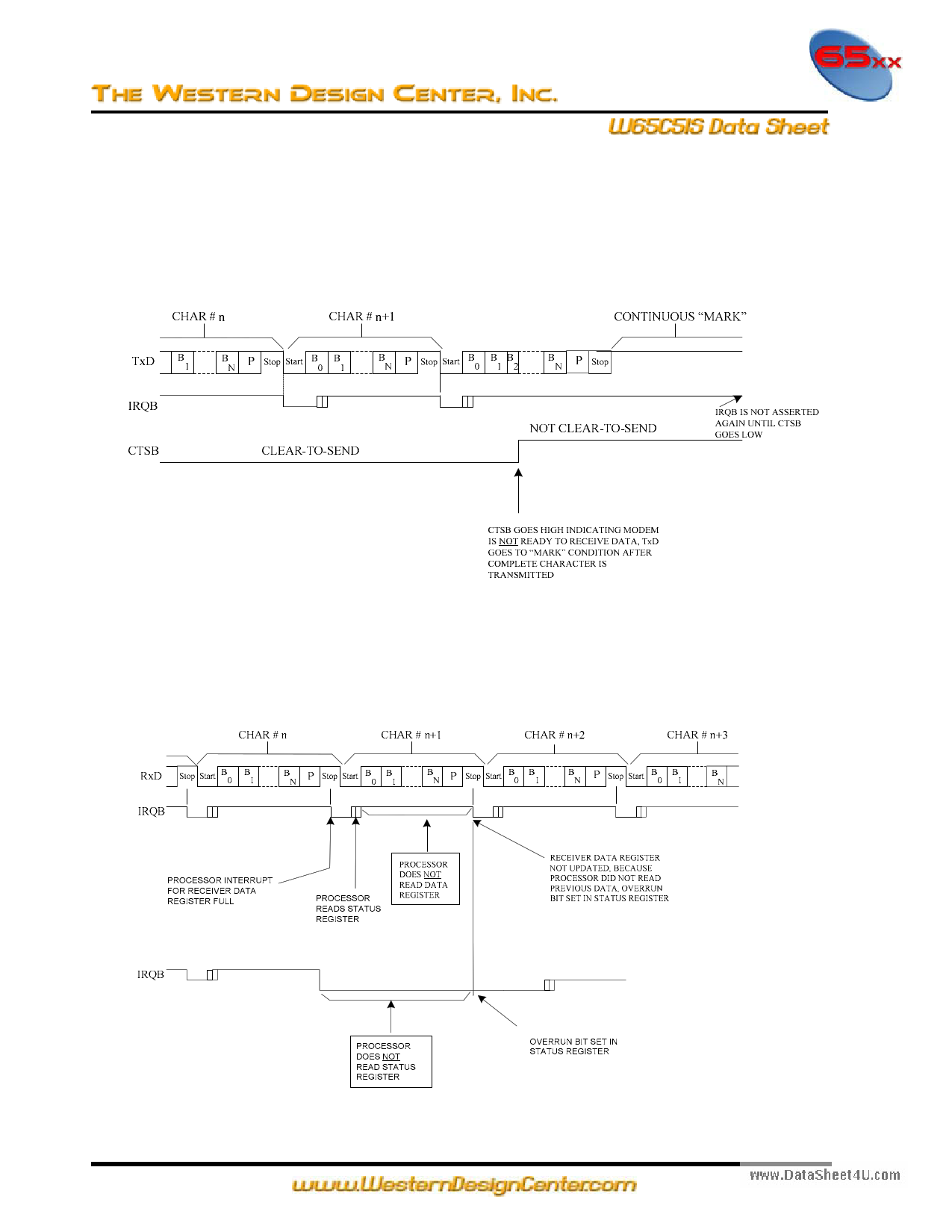

Effect of CTSB on Transmitter

CTSB is the Clear-to-Send signal generated by the modem.

It is normally low (true state) but may go high in the event of

some modem problems. When this occurs, the TxD line goes

to the “MARK” condition after the entire last character

(including parity and stop bit) have been transmitted. Bit 4

in the Status Register indicates that the Transmitter Data

Register is not empty and IRQB is not asserted. CTSB is

transmit control line only, and has not effect on the ACIA

Receiver Operation. Figure 8 shows the timing relationship

for this mode of operation.

www.DataSheet4U.com

Figure 9 Effect of CTS on Transmitter

Effect of Overrun on Receiver

If the processor does not read the Receiver Data Register in

the allocated time, then, when the following interrupt occurs,

the new data word is not transferred to the Receiver Data

Register, but the Overrun status bit is set. Thus, the

Data Register will contain the last valid data word received

and all following data is lost. Figure 9 shows the timing

relationship for this mode.

Figure 10 Effect of Overrun on Receiver

11

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet W65C51S.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W65C51S | Asynchronous Communications Interface Adapter | WDC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |