No Preview Available !

March 2001

Revised July 2002

www.DataSheet4U.com

SSTV16859

Dual Output 13-Bit Register with

SSTL-2 Compatible I/O and Reset

General Description

The SSTV16859 is a dual output 13-bit register designed

for use with 184 and 232 pin DDR-1 memory modules. The

device has a differential input clock, SSTL-2 compatible

data inputs and a LVCMOS compatible RESET input. The

device has been designed to meet the JEDEC DDR mod-

ule register specifications.

The device has been fabricated on an advanced sub-

micron CMOS process and is designed to operate at power

supplies of less than 3.6V’s.

Features

I Compliant with DDR-I registered module specifications

I Operates at 2.5V ± 0.2V VDD

I SSTL-2 compatible input structure

I SSTL-2 compliant output structure

I Differential SSTL-2 compatible clock inputs

I Low power mode when device is reset

I Industry standard 64 pin TSSOP package

I Also packaged in plastic Fine-Pitch Ball Grid Array

(FBGA)

Ordering Code:

Order Number Package Number

Package Description

SSTV16859G

(Note 1)(Note 2)

BGA96A

96-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide

SSTV16859MTD

(Note 2)

MTD64

64-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Note 1: Ordering code “G” indicates Trays.

Note 2: Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

© 2002 Fairchild Semiconductor Corporation DS500414

www.fairchildsemi.com

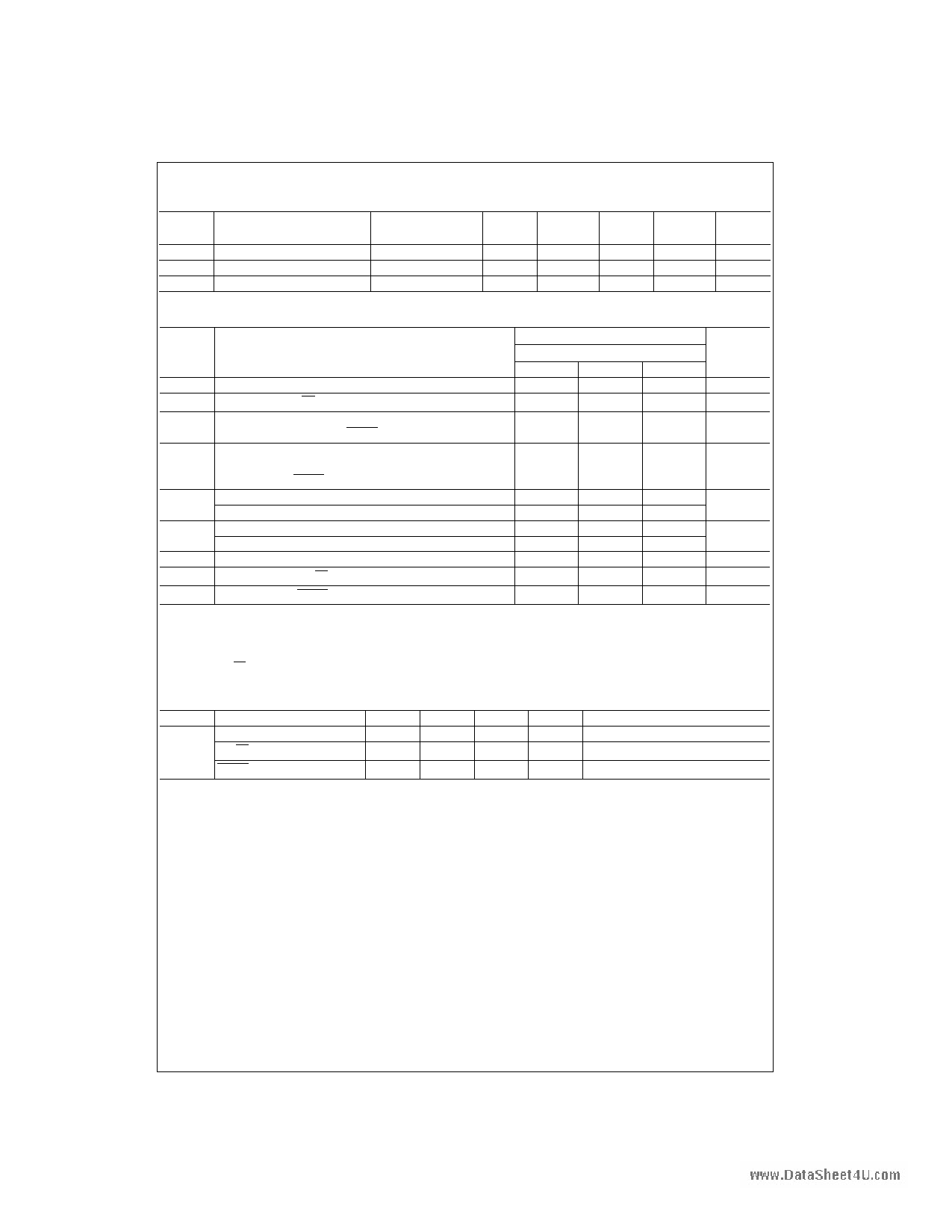

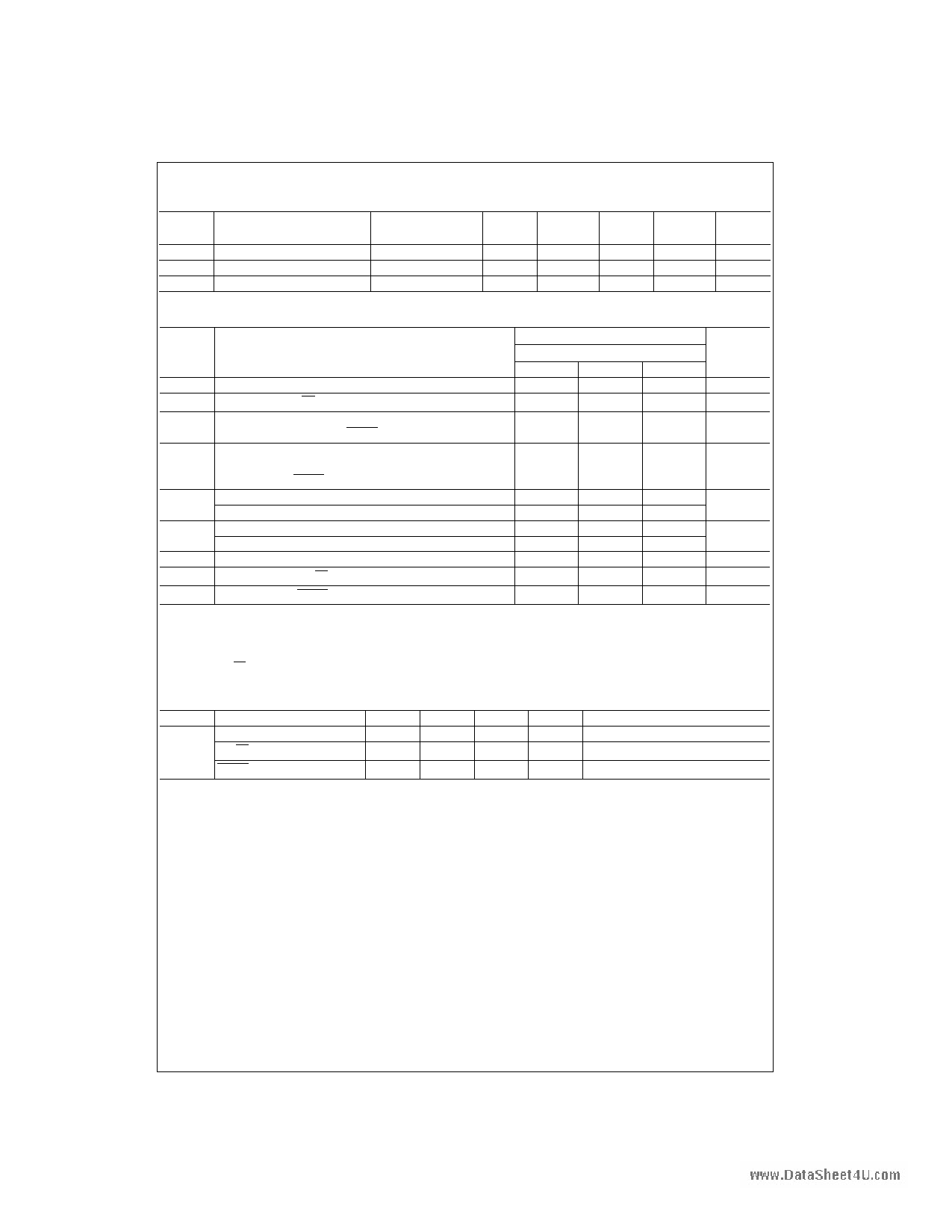

DC Electrical Characteristics (Continued)

www.DataSheet4U.com

Symbol

Parameter

Conditions

ROH

ROL

RO∆

Output HIGH On Resistance

Output LOW On Resistance

| ROH - ROL |

IOH = −20 mA

IOL = 20 mA

IO = 20 mA, TA = 25°C

AC Electrical Characteristics (Note 6)

Symbol

Parameter

fMAX

Maximum Clock Frequency

tW

tACT

(Note 7)

Pulse Duration, CK, CK HIGH or LOW (Figure 2)

Differential Inputs Activation Time,

data inputs must be LOW after RESET HIGH (Figure 3)

tINACT

(Note 7)

Differential Inputs De-activation Time,

data and clock inputs must be held at valid levels

(not floating) after RESET LOW

tS Setup Time, Fast Slew Rate (Note 8)(Note 9) (Figure 5)

Setup Time, Slow Slew Rate (Note 9)(Note 10) (Figure 5)

tH Hold Time, Fast Slew Rate (Note 8)(Note 10) (Figure 5)

Hold Time, Slow Slew Rate (Note 9)(Note 10) (Figure 5)

tREM

Reset Removal Time (Figure 7)

tPHL, tPLH Propagation Delay CK, CK to Qn (Figure 4)

tPHL Propagation Delay RESET to Qn (Figure 6)

Note 6: Refer to Figure 1 through Figure 7.

Note 7: This parameter is not production tested.

Note 8: For data signal input slew rate ≥ 1 V/ns.

Note 9: For data signal input slew rate ≥ 0.5 V/ns and < 1 V/ns.

Note 10: For CK, CK signals input slew rates are ≥ 1 V/ns.

Capacitance (Note 11)

Symbol

CIN

Parameter

Data Pin Input Capacitance

CK, CK - Input Capacitance

Min Typ

2.2

2.2

RESET

2.3

Note 11: TA = +25°C, f = 1 MHz, Capacitance is characterized but not tested.

VDD

Min

Typ

Max

Units

(V)

2.3 to 2.7

7

20 Ω

2.3 to 2.7

7

20 Ω

2.5 4 Ω

TA = 0°C to +70°C, CL = 30 pF, RL = 50Ω

VDD = 2.5V ± 0.2V; VDDQ = 2.5V ± 0.2V

Min Typ Max

200

2.5

22

Units

MHz

ns

ns

22

0.75

0.9

0.75

0.9

10

1.1

ns

ns

ns

ns

2.8 ns

5.0 ns

Max

3.2

3.2

3.3

Units

pF

pF

pF

Conditions

VDD = 2.5V, VI = VREF ± 310 mV

VDD = 2.5V, VICR = 1.25, VI(PP) = 360 mV

VDD = 2.5V, VI = VDD or GND

5 www.fairchildsemi.com