|

|

PDF ML22Q54 Data sheet ( Hoja de datos )

| Número de pieza | ML22Q54 | |

| Descripción | 2-Channel Mixing Oki ADPCM Algorithm-Based Speech Synthesis LSI | |

| Fabricantes | OKI electronic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ML22Q54 (archivo pdf) en la parte inferior de esta página. Total 31 Páginas | ||

|

No Preview Available !

OKI Semiconductor

ML2252/54-XXX, ML22Q54

2-Channel Mixing Oki ADPCM Algorithm-Based Speech Synthesis LSI

FEDL2250DIGEST-01

Issue Date: Oct. 15, 2002

This document contains minimum specifications. For full specifications, please contact your nearest Oki office or

representative.

GENERAL DESCRIPTION

www.DataSheet4U.com

The ML2250 family is a 2-channel mixing speech synthesis device with an on-chip voice data (i.e., phrases)

storing mask ROM and a flash memory. Besides playing the built-in voice data, this device can output voice data

that is input from outside the device. This ML2250 family allows to select the playback method from the 8-bit

PCM, non-linear 8-bit PCM, 16-bit PCM, 2-bit ADPCM2, and 4-bit ADPCM2 algorithms. And the sound volume

is adjustable as well.

The ML2250 family incorporates a 14-bit D/A converter, low-pass filter, and 1-bit DAC (PWM output).

It is easy to configure a speech synthesizer by externally connecting a power amplifier and a CPU to the ML2250

family.

The ML2250 family line-up includes 2 types of products: with on-chip mask ROM, and with on-chip flash

memory.

• ML2252/54-XXX

This is a CMOS single chip speech synthesis device with an on-chip mask ROM. Products with 2 types of mask

ROMs are available in the ML2250 family depending upon the total playback time length.

• ML22Q54

The ML22Q54 is a speech synthesis device with a 4-Mbit flash memory built in. The voice data can be easily

written to the flash memory using a special tool. The on-chip flash memory product is suitable for the diversified

low volume production or short delivery time applications that the on-chip mask ROM product cannot support.

The ML22Q54 is most suitable for evaluation because the circuit configuration is the same as the on-chip mask

ROM product.

A combination of fixed and variable messages can be written because it is easy to write to the built-in flash

memory. It is also possible to store and read data, other than voice, to/from an area in the flash memory not used

as voice data.

1/31

1 page

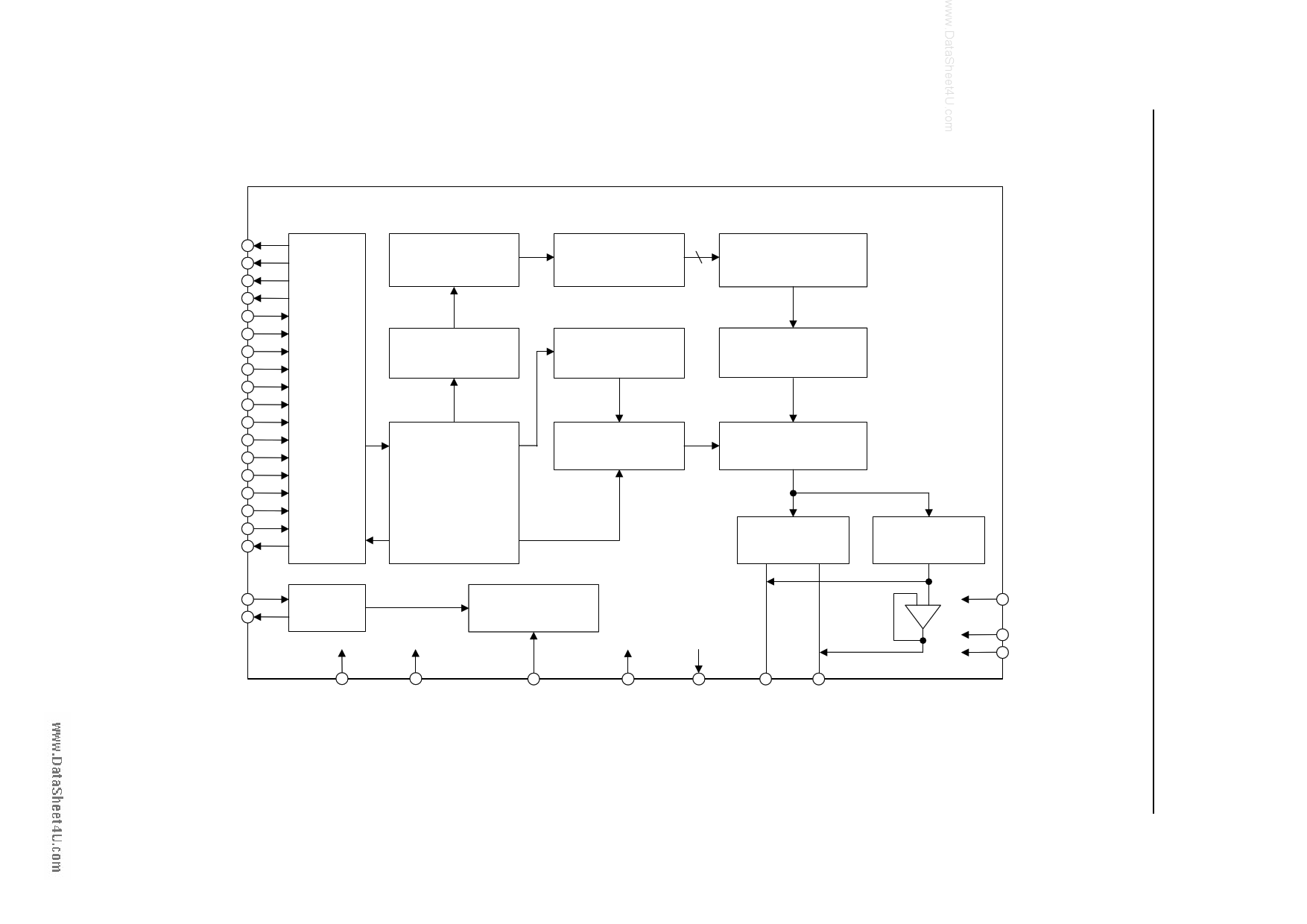

NCR1/NDR

NCR2/DL

BUSY1

BUSY2/ERR

SERIAL

D7/DI

D6/SCK

D5/DO

D4

D3

D2

D1

D0

WR

CS

DW

RD

RD/BY

XT

XT

18bit Multiplexer

CPU

Interface

18bit

Address Controller

Command

Controller

4Mbit Flash

ROM

16

2bit ADPCM2

/4bit ADPCM2

Synthesizer

Phrase Control

Table

8bit PCM

16bit PCM

Synthesizer & 2ch Mix

Loop Volume

Digital Filter

1bit DAC

14bit DAC

OSC

Timing Controller

DVDD

DGND

RESET

TEST

TESTO

OUT(+) OUT(–)

/DAO /AOUT

OPTANA

AVDD

AGND

5 Page

OKI Semiconductor

FEDL2250DIGEST-01

ML2252/54-XXX, ML22Q54

Pin

24

www.DataSheet4U.com

26

28

29

32

36

37

42

2

6

7

8

Symbol

D6/SCK

D7/DI

OUT(+)/DAO

OUT(–)/AOUT

SERIAL

CS

OPTANA

WR

DW

RD

TESTO

RD/BY

Type

I/O

I/O

O

O

I

I

I

I

I

I

O

O

Description

Works as CPU interface data bus pin in parallel input interface.

Works as flash memory data output pin when reading the built-in flash

memory data.

When RD is at “L” level other than when reading the flash memory data,

this D6/SCK pin usually outputs “L” level.

Works as serial clock input pin in the serial input interface.

When the SCK input is at “L” level on the falling edge of CS, the DI input

is captured in device on the rising edge of SCK clock. And when the

SCK input is at “H” level on the falling edge of CS, the DI input is

captured on the falling edge of SCK clock.

Works as CPU interface data bus pin in the parallel input interface.

Works as flash data output pin when reading the built-in flash memory

data.

When RD is at “L” level at times other than reading the flash memory

data, this D7/DI pin usually outputs “L” level.

Works as serial data input pin in the serial input interface.

When OPTANA pin is at “H” level, this OUT(+)/DAO pin outputs PWM

(positive phase) of 1-bit DAC.

And when OPTANA pin is at “L” level, the OUT(+)/DAO pin outputs the

14-bit DAC analog signal.

When OPTANA pin is at “H” level, this OUT(–)/AOUT pin outputs PWM

(reverse phase) of 1-bit DAC.

And when OPTANA pin is at “L” level, the OUT(–)/AOUT pin outputs the

14-bit DAC analog signal via voltage follower.

CPU interface switching pin.

At “H” level: Serial input interface. At “L” level: Parallel input interface.

CPU interface chip select pin.

When CS pin is at “H” level, the WR, DW, and RD signals cannot be

input to the device.

Analog output/PWM output select signal.

At OPTANA pin = “H” level, PWM of 1-bit DAC is output from

OUT(+)/DAO and OUT(–)/AOUT pins.

At OPTANA pin = “L” level, 14-bit DAC analog signal is output from

OUT(+)/DAO pin and 14-bit DAC analog signal is output from

OUT(–)/AOUT pin via the voltage follower.

CPU interface write signal.

When CS pin is at “H” level, the WR signal cannot be input to the device.

Data write signal at EXT command and Flash I/F command.

When the EXT and Flash I/F commands are not used, keep this pin at

“H” level.

When CS pin is at “H” level, the DW signal cannot be input to the device.

This pin has a pull-up resistor built in.

CPU interface read signal.

This pin is used when reading the status signal of each channel or when

reading data of the built-in flash memory.

When not in use, keep this pin to “H” level.

This pin has a pull-up resistor built in.

Output pin for testing.

Keep this pin open.

Output pin to indicate the automatic erase/write status of the built-in

flash memory.

Outputs “L” level during erase or programming cycle to indicate the

busy state. Goes to “H” level at the end of the erase or programming

cycle and enters into the ready state.

11/31

11 Page | ||

| Páginas | Total 31 Páginas | |

| PDF Descargar | [ Datasheet ML22Q54.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ML22Q54 | 2-Channel Mixing Oki ADPCM Algorithm-Based Speech Synthesis LSI | OKI electronic |

| ML22Q58 | 2-Channel Mixing Oki ADPCM Algorithm-Based Speech Synthesis LSI | OKI electronic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |