|

|

PDF WCSS0418V1P Data sheet ( Hoja de datos )

| Número de pieza | WCSS0418V1P | |

| Descripción | 256K x 18 Synchronous-Pipelined Cache RAM | |

| Fabricantes | Weida Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de WCSS0418V1P (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

Y7C1327

WCSS0418V1P

256K x 18 Synchronous-Pipelined Cache RAM

Features

• Supports 100-MHz bus for Pentium and PowerPC™

operations with zero wait states

• Fully registered inputs and outputs for pipelined

operation

• 256K by 18 common I/O architecture

• 3.3V core power supply

• 2.5V / 3.3V I/O operation

• Fast clock-to-output times

www.DataSheet4U.com

— 3.5 ns (for 166-MHz device)

— 4.0 ns (for 133-MHz device)

— 5.5 ns (for 100-MHz device)

• User-selectable burst counter supporting Intel

Pentium interleaved or linear burst sequences

• Separate processor and controller address strobes

• Synchronous self-timed writes

• Asynchronous Output Enable

• JEDEC-standard 100 TQFP pinout

• “ZZ” Sleep Mode option and Stop Clock option

Functional Description

The WCSS0418V1P is a 3.3V, 256K by 18 synchronous-pipe-

lined cache SRAM designed to support zero wait state sec-

ondary cache with minimal glue logic.

The WCSS0418V1P I/O pins can operate at either the 2.5V or

the 3.3V level. The I/O pins are 3.3V tolerant when VD-

DQ=2.5V.

All synchronous inputs pass through input registers controlled

by the rising edge of the clock. All data outputs pass through

output registers controlled by the rising edge of the clock. Max-

imum access delay from the clock rise is 3.5 ns (166-MHz

device).

The WCSS0418V1P supports either the interleaved burst se-

quence used by the Intel Pentium processor or a linear burst

sequence used by processors such as the PowerPC. The

burst sequence is selected through the MODE pin. Accesses

can be initiated by asserting either the Processor Address

Strobe (ADSP) or the Controller Address Strobe (ADSC) at

clock rise. Address advancement through the burst sequence

is controlled by the ADV input. A 2-bit on-chip wraparound

burst counter captures the first address in a burst sequence

and automatically increments the address for the rest of the

burst access.

Byte write operations are qualified with the four Byte Write

Select (BW[1:0]) inputs. A Global Write Enable (GW) overrides

all byte write inputs and writes data to all four bytes. All writes

are conducted with on-chip synchronous self-timed write cir-

cuitry.

Three synchronous Chip Selects (CE1, CE2, CE3) and an

asynchronous Output Enable (OE) provide for easy bank se-

lection and output three-state control. In order to provide prop-

er data during depth expansion, OE is masked during the first

clock of a read cycle when emerging from a deselected state.

Logic Block Diagram

CLK

ADV

ADSC

ADSP

A[17:0]

GW

BWE

BW 1

BW0

18

MODE

(A[1;0]) 2

BURST Q0

CE COUNTER

CLR

Q1

Q

ADDRESS

CE

D

REGISTER

16

D DQ[15:8], DP[1] Q

BYTEWRITE

REGISTERS

D DQ[7:0], DP[0] Q

BYTEWRITE

REGISTERS

16

18

256KX18

MEMORY

ARRAY

CE1

CE2

CE3

OE

ZZ

D

CE

ENABLE CE

REGISTER

Q

D ENABLE DELAY Q

REGISTER

SLEEP

CONTROL

Intel and Pentium are registered trademarks of Intel Corporation.

PowerPC is a trademark of IBM Corporation.

Document #: 38-05247

18 18

OUTPUT

REGISTERS

CLK

INPUT

REGISTERS

CLK

DQ[15:0]

DP[1:0]

Revised February 6, 2001

1 page

WCSS0418V1P

Because the WCSS0418V1P is a common I/O device, the

Output Enable (OE) must be deasserted HIGH before present-

ing data to the DQ[15:0] and DP[1:0] inputs. Doing so will

three-state the output drivers. As a safety precaution, DQ[15:0]

and DP[1:0] are automatically three-stated whenever a write

cycle is detected, regardless of the state of OE.

Single Write Accesses Initiated by ADSC

ADSC write accesses are initiated when the following condi-

tions are satisfied: (1) ADSC is asserted LOW, (2) ADSP is

deasserted HIGH, (3) CE1, CE2, CE3 are all asserted active,

and (4) the appropriate combination of the write inputs (GW,

BWE, and BW[1:0]) are asserted active to conduct a write to

the desired byte(s). ADSC-triggered write accesses require a

www.DataShseientg4lUe.ccolmock cycle to complete. The address presented to

A[17:0] is loaded into the address register and the address ad-

vancement logic while being delivered to the RAM core. The

ADV input is ignored during this cycle. If a global write is con-

ducted, the data presented to the DQ[15:0] and DP[1:0] is written

into the corresponding address location in the RAM core. If a

byte write is conducted, only the selected bytes are written.

Bytes not selected during a byte write operation will remain

unaltered. A synchronous self-timed write mechanism has

been provided to simplify the write operations.

Because the WCSS0418V1P is a common I/O device, the

Output Enable (OE) must be deasserted HIGH before present-

ing data to the DQ[15:0] and DP[1:0] inputs. Doing so will

three-state the output drivers. As a safety precaution, DQ[15:0]

and DP[1:0] are automatically three-stated whenever a write

cycle is detected, regardless of the state of OE.

Burst Sequences

The WCSS0418V1P provides a two-bit wraparound counter,

fed by A[1:0], that implements either an interleaved or linear

burst sequence. The interleaved burst sequence is designed

specifically to support Intel Pentium applications. The linear

burst sequence is designed to support processors that follow

ZZ Mode Electrical Characteristics

Parameter

IDDZZ

tZZS

tZZREC

Description

Snooze mode

standby current

Device operation to

ZZ

ZZ recovery time

Test Conditions

ZZ > VDD − 0.2V

ZZ > VDD − 0.2V

ZZ < 0.2V

a linear burst sequence. The burst sequence is user selectable

through the MODE input.

Asserting ADV LOW at clock rise will automatically increment

the burst counter to the next address in the burst sequence.

Both read and write burst operations are supported.

Interleaved Burst Sequence

First

Address

A[1:0]

00

01

10

11

Second

Address

A[1:0]

01

00

11

10

Third

Address

A[1:0]

10

11

00

01

Fourth

Address

A[1:0]

11

10

01

00

Linear Burst Sequence

First

Address

A[1:0]

00

01

10

11

Second

Address

A[1:0]

01

10

11

00

Third

Address

A[1:0]

10

11

00

01

Fourth

Address

A[1:0]

11

00

01

10

Sleep Mode

The ZZ input pin is an asynchronous input. Asserting ZZ plac-

es the SRAM in a power conservation “sleep” mode. Two clock

cycles are required to enter into or exit from this “sleep” mode.

While in this mode, data integrity is guaranteed. Accesses

pending when entering the “sleep” mode are not considered

valid nor is the completion of the operation guaranteed. The

device must be deselected prior to entering the “sleep” mode.

CE1, CE2, CE3, ADSP, and ADSC must remain inactive for the

duration of tZZREC after the ZZ input returns LOW.

Min.

2tCYC

Max.

3

2tCYC

Unit

mA

ns

ns

Document #: 38-05247

Page 5 of 17

5 Page

WCSS0418V1P

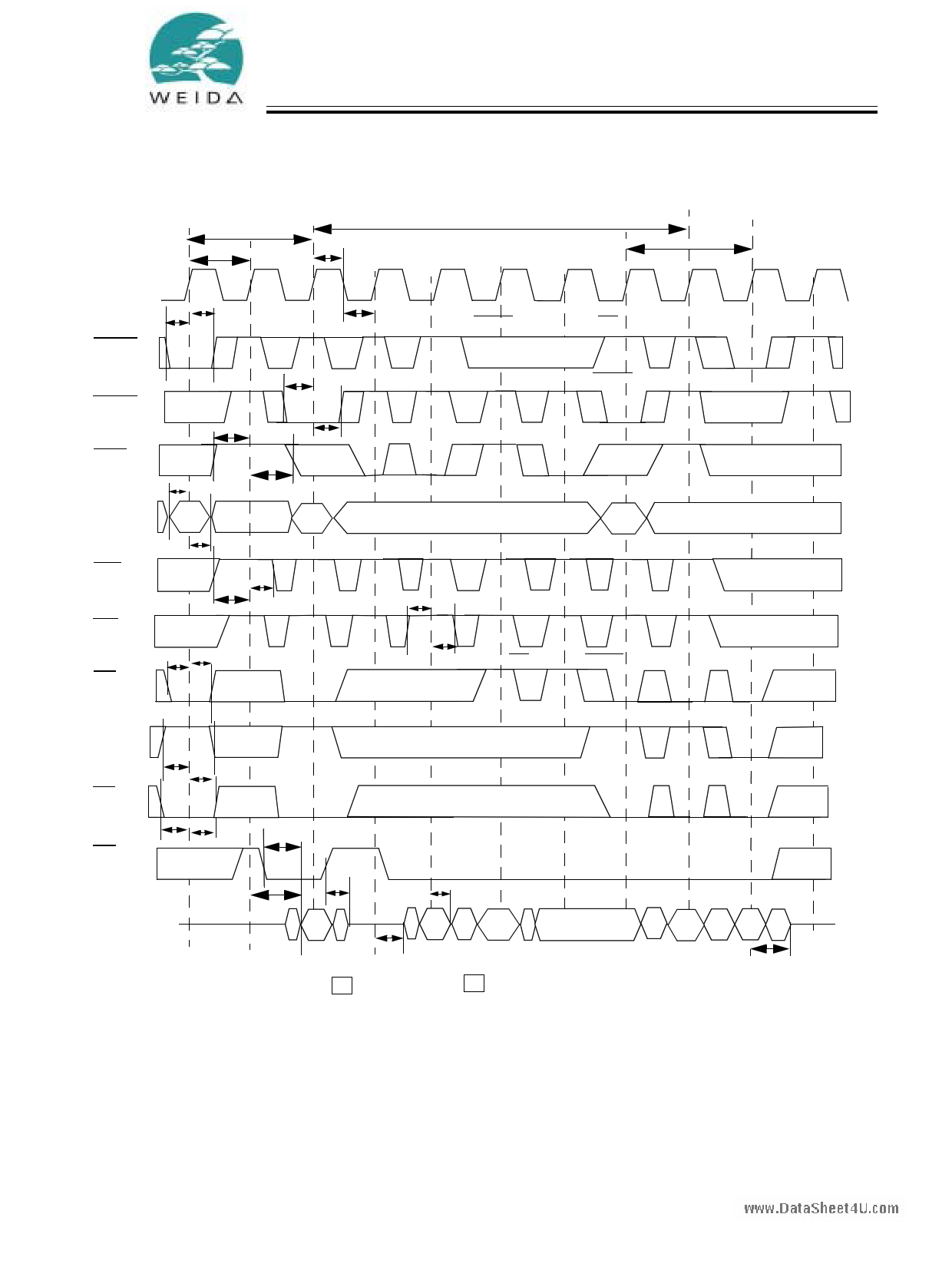

Switching Waveforms (continued)

Read Cycle Timing[14, 16]

CLK

Single Read

tCYC

tCH

Burst Read

Pipelined Read

Unselected

tADS

ADSP

www.DataSheet4U.com

tADH

tADS

tCL

ADSC

ADV

tADVS

tADH

tAS

ADD

RD1

tADVH

RD2

tAH

GW

tWS

tWH

WE

CE1

tCES tCEH

ADSP ignored with CE1 inactive

ADSC initiated read

Suspend Burst

RD3

tWS

tWH CE1 masks ADSP

CE2

tCES

CE3

tCES

OE

Data Out

tCEH

tCEH

tEOV

tOEHZ

tCO

11aa

tCLZ

tDOH

2a 2b

2c 2c

= DON’T CARE

= UNDEFINED

Unselected with CE2

2d 3a

tCHZ

Note:

16. RDx stands for Read Data from Address X.

Document #: 38-05247

Page 11 of 17

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet WCSS0418V1P.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| WCSS0418V1F | 256K x 18 Synchronous 3.3V Cache RAM | Weida Semiconductor |

| WCSS0418V1P | 256K x 18 Synchronous-Pipelined Cache RAM | Weida Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |