|

|

PDF AT17F16 Data sheet ( Hoja de datos )

| Número de pieza | AT17F16 | |

| Descripción | FPGA Configuration Flash Memory | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT17F16 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

Features

• Prowgwrwam.DmataaSbhleee1t46U,7.c7o7m,216 x 1-bit Serial Memories Designed to Store Configuration

Programs for Field Programmable Gate Arrays (FPGAs)

• 3.3V Output Capability

• 5V Tolerant I/O Pins

• Program Support using the Atmel ATDH2200E System or Industry Third-party

Programmers

• In-System Programmable (ISP) via 2-wire Bus

• Simple Interface to SRAM FPGAs

• Compatible with Atmel AT40K and AT94K Devices, Altera® FLEX®, APEX™ Devices,

Lucent® ORCA® FPGAs, Xilinx® XC3000, XC4000, XC5200, Spartan®, Virtex® FPGAs,

Motorola® MPA1000 FPGAs

• Cascadable Read-back to Support Additional Configurations or Higher-density Arrays

• Low-power CMOS FLASH Process

• Available in 6 mm x 6 mm x 1 mm 8-lead LAP (Pin-compatible with 8-lead SOIC/VOIC

Footprint Packages), 20-lead PLCC and 44-lead TQFP Packages

• Emulation of Atmel’s AT24CXXX Serial EEPROMs

• Low-power Standby Mode

• Single Device Capable of Holding 4-bit Stream Files Allowing Simple System

Reconfiguration

• Fast Serial Download Speeds up to 33 MHz

• Endurance: 10,000 Write Cycles Typical

• Green (Pb/Halide-free/RoHS Compliant) Package Options Available

FPGA

Configuration

Flash Memory

AT17F16

1. Description

The AT17F Series of In-System Programmable Configuration PROMs (Configurators)

provide an easy-to-use, cost-effective configuration memory for Field Programmable

Gate Arrays. The AT17F Series device is packaged in the 8-lead LAP, 20-lead PLCC

and 44-lead TQFP, see Table 1-1. The AT17F Series Configurator uses a simple

serial-access procedure to configure one or more FPGA devices.

The AT17F Series Configurators can be programmed with industry-standard program-

mers, Atmel’s ATDH2200E Programming Kit or Atmel’s ATDH2225 ISP Cable.

Table 1-1. AT17F Series Packages

Package

8-lead LAP

20-lead PLCC

44-lead TQFP

AT17F16

Yes

Yes

Yes

3392F–CNFG–2/08

1 page

AT17F16

5.4 PAGESEL[1:0](2)

www.DataSheet4U.com Page select inputs. Used to determine which of the 4 memory pages are targeted during a serial

configuration download. The address space for each of the pages is shown in Table 5-2. When

SER_EN is Low (ISP mode) these pins have no effect.

Table 5-2. Address Space

Paging Decodes

PAGESEL = 00, PAGE_EN = 1

PAGESEL = 01, PAGE_EN = 1

PAGESEL = 10, PAGE_EN = 1

PAGESEL = 11, PAGE_EN = 1

PAGESEL = XX, PAGE_EN = 0

AT17F16 (16 Mbits)

00000 – 3FFFFh

40000 – 7FFFFh

80000 – BFFFFh

C0000 – FFFFFh

00000 – FFFFFh

5.5 RESET/OE(1)

Output Enable (active High) and RESET (active Low) when SER_EN is High. A Low level on

RESET/OE resets both the address and bit counters. A High level (with CE Low) enables the

data output driver.

5.6 CE(1)

Chip Enable input (active Low). A Low level (with OE High) allows CLK to increment the address

counter and enables the data output driver. A High level on CE disables both the address and bit

counters and forces the device into a low-power standby mode. Note that this pin will not

enable/disable the device in the 2-wire Serial Programming mode (SER_EN Low).

5.7 GND

5.8 CEO

5.9 A2(1)

Ground pin. A 0.2 µF decoupling capacitor between VCC and GND is recommended.

Chip Enable Output (when SER_EN is High). This output goes Low when the internal address

counter has reached its maximum value. If the PAGE_EN input is set High, the maximum value

is the highest address in the selected partition. The PAGESEL[1:0] inputs are used to make the

4 partition selections. If the PAGE_EN input is set Low, the device is not partitioned and the

address maximum value is the highest address in the device, see Table 5-2 on page 5. In a

daisy chain of AT17F Series devices, the CEO pin of one device must be connected to the CE

input of the next device in the chain. It will stay Low as long as CE is Low and OE is High. It will

then follow CE until OE goes Low; thereafter, CEO will stay High until the entire EEPROM is

read again.

Device selection input, (when SER_EN Low). The input is used to enable (or chip select) the

device during programming (i.e., when SER_EN is Low). Refer to the AT17F Programming

Specification available on the Atmel web site for additional details.

Notes: 1. This pin has an internal 20 kΩ pull-up resistor.

2. This pin has an internal 30 kΩ pull-down resistor.

3392F–CNFG–2/08

5

5 Page

AT17F16

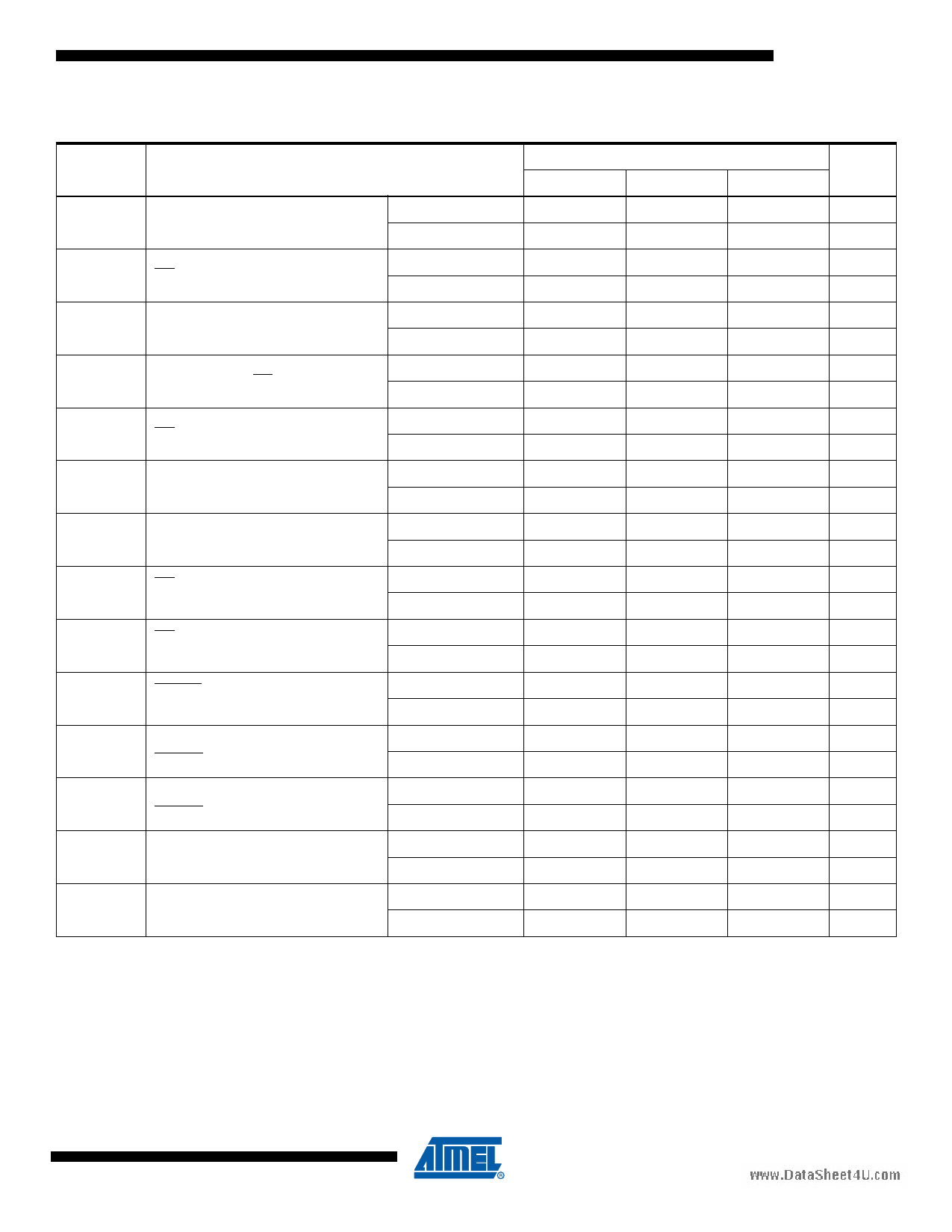

16. AC Characteristics

www.DataSheet4U.com

Symbol

TOE(2)

Description

OE to Data Delay

TCE(2)

CE to Data Delay

TCAC(2)

CLK to Data Delay

TOH Data Hold from CE, OE, or CLK

TDF(3)

CE or OE to Data Float Delay

TLC CLK Low Time

THC

TSCE

THCE

THOE

FMAX

FMAX

TWR

TEC

CLK High Time

CE Setup Time to CLK

(to guarantee proper counting)

CE Hold Time from CLK

(to guarantee proper counting)

RESET/OE Low Time

(guarantees counter is reset)

Maximum Input Clock Frequency

SEREN = 0

Maximum Input Clock Frequency

SEREN = 1

Write Cycle Time(4)

Erase Cycle Time(4)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

Commercial

Industrial(1)

AT17F16

Min Typ Max Units

50 ns

55 ns

55 ns

60 ns

3 30 ns

30 ns

0 ns

0 ns

15 ns

15 ns

15 ns

15 ns

15 ns

15 ns

20 ns

25 ns

0 ns

0 ns

20 ns

20 ns

10 MHz

10 MHz

33 MHz

33 MHz

12 µs

12 µs

25 s

25 s

Notes:

1. Preliminary specifications for military operating range only.

2. AC test lead = 50 pF.

3. Float delays are measured with 5 pF AC loads. Transition is measured ±200 mV from steady-state active levels.

4. See the AT17F Programming Specification for procedural information.

3392F–CNFG–2/08

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet AT17F16.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT17F16 | FPGA Configuration Flash Memory | ATMEL Corporation |

| AT17F16A | FPGA Configuration Flash Memory | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |