|

|

PDF PBL3798 Data sheet ( Hoja de datos )

| Número de pieza | PBL3798 | |

| Descripción | Subscriber Line Interface Circuit | |

| Fabricantes | Ericsson | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de PBL3798 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

March 1997

www.DataSheet4U.com

PBL 3798, PBL 3798/2

Subscriber Line

Interface Circuit

Description

PBL 3798 is an analog Subscriber Line Interface Circuit (SLIC), which is fabricated in

a 75 V bipolar, monolithic process.

The programmable, constant current feed circuit incorporates a switch mode

regulator to minimize on-chip power dissipation. A stand-by state further reduces idle

power dissipation, while allowing the supervisory functions to be active.

Tip-ring polarity is reversible without altering SLIC supervisory and voice frequency

(vf) functions. Tip and ring outputs can be set to high impedance states. These and

other operating states are activated via a parallel, four bit control word.

An external resistor controls the off-hook detector threshold current. A ground key

detector with internal reference reports tip/ring dc current unbalance. The ring trip

detector can operate with both balanced and unbalanced ringing systems. The three

detectors are read via a shared output.

Ring and test relay drivers with internal clamp diodes are provided.

The complex or real two-wire impedance is set by a scaled, lumped element

network.

Two- to four-wire and four- to two-wire signal conversion is provided by the SLIC in

conjunction with either a conventional or a programmable CODEC/filter.

Longitudinal line voltages are suppressed by a control loop within the SLIC.

The PBL 3798 package is 28-pin, dual-in-line; 32-pin or 44-pin j-leaded chip

carrier.

The difference between PBL 3798 and PBL 3798/2 is mainly the longitudinal

balance spec.

6/4

RINGRLY

7/5

TESTRLY

40/26

DR

38/25

DT

42/27

TIPX

34/22

HPT

35/23

HPR

43/28

RINGX

3/2

VREG

L 8/6

10/7

VBAT

GND2 2/1

Ring Relay

Driver

Test Relay

Driver

Ring Trip

Comparator

Two-wire

Interface

Input

Decoder

and

Control

Loop/Gnd key

Detector

VF Signal

Transmission

Line Feed

Controller and

Longitudinal

Suppression

Switching

Regulator

12/9 11/8 14/10

CHS VQBAT CHCLK

4/3

VCC

31/20

VEE

23/16

21/14

22/15

16/11

C1

C2

C3

C4

19/ E0

17/12

E1

20/13

DET

37/24

32/21

29/19

RD

VTX

RSN

26/17

15/

RDC

RSG

27/18

GND1

Key Features

• On-chip switch mode regulator to

minimize power dissipation

• Programmable, constant current feed

• Line feed characteristics independent

of battery variations

• Tip-ring polarity reversal function

• Tip and ring open circuit state;

tip open with ring active state

• Detectors:

- programmable loop current/ring

ground detector

- ground key detector

- ring trip detector

• Ring and test relay drivers

• Line terminating impedance, complex

or real, set by a simple external

network

• Hybrid function with conventional or

programmable CODEC/filters

• 70 dB longitudinal to metallic balance

• 79 mA peak longitudinal current

suppression

• Idle noise < 7 dBrnC; <-83 dBup

PBL 3798

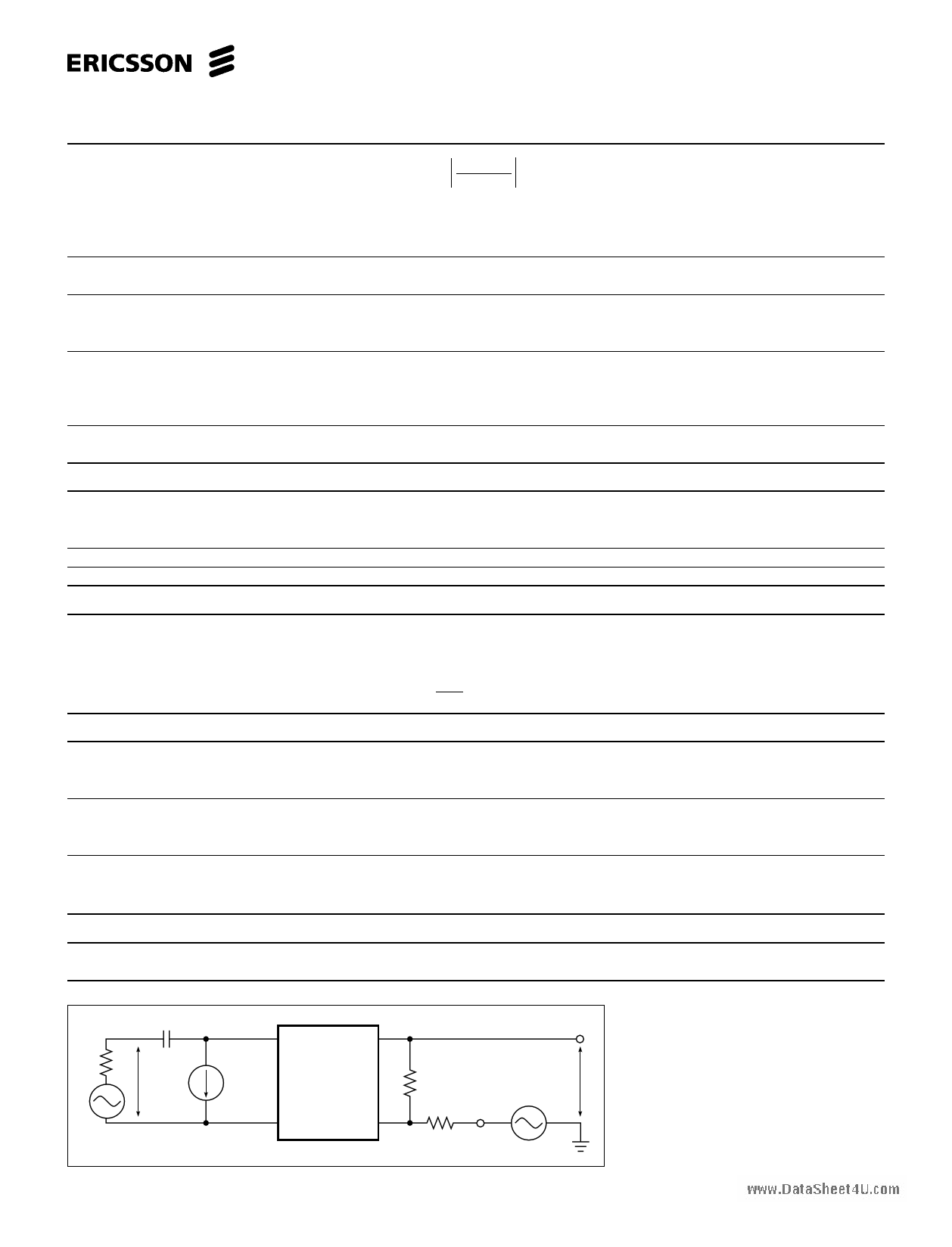

Figure 1. Block diagram.

4-127

1 page

Parawmwewte.Dr ataSheet4U.com

2-wire return loss, r

Polarity reversal time, tpol

TIPX idle voltage, V

Ti

TIPX to RINGX idle

voltage, VTro

Standard version

-/2 version

4-wire Transmit Port (VTX)

Overload level, VTXO

Output offset voltage, ∆VTX

Output impedance, z

TX

4-wire Receive Port (RSN)

RSN dc voltage, VRSN

RSN impedance, zRSN

RSN current (IRSN) to metallic

loop

current

(I )

L

gain,

αRSN

Frequency Response

Two-wire to four-wire, g2-4

Four-wire to two-wire, g

4-2

Four-wire to four-wire, g4-4

Insertion Loss

Two-wire to four-wire, G2-4

Ref

fig Conditions

r = 20 • log ZL + ZTR , Note 5

Z -Z

L TR

0.2kHz ≤ f < 0.5kHz

0.5kHz ≤ f < 1.0kHz

1.0kHz ≤ f ≤ 3.4kHz

Normal to reversed polarity or

reversed to normal polarity

Normal polarity, stand-by

V = -48V

Bat

VBat = -63V, Note 6

Active and standby

VBat = -48V, Rl = open loop

Normal polarity

Reversed polarity

Normal polarity

Reversed polarity

2 Load impedance > 20 kΩ,

f = 1 kHz, 1% THD, ERX = 0

Note 7

0.2kHz ≤ f ≤ 3.4kHz

IRSN = 0

0.2kHz ≤ f ≤ 3.4kHz

0.2kHz ≤ f ≤ 3.4kHz,

αRSN =

I

L

IRSN

6 0.3kHz ≤ f ≤ 3.4kHz

Relative to 1.0 kHz, 0 dBu

ERX = 0 V, (Notes 2, 8)

6 0.3kHz ≤ f ≤ 3.4kHz

Relative to 1.0 kHz, 0 dBu

EL = 0 V, (Notes 2, 9)

6 0.3kHz ≤ f ≤ 3.4kHz

Relative to 1.0 kHz, 0 dBu

EL = 0 V, (Notes 2, 9)

6 0 dBu, 1 kHz, ERX = 0

(Notes 8, 10)

PBL 3798

Min Typ Max Unit

30 32

dB

25 27

dB

15 17

dB

4 15 ms

-5.0 -3.5 -2.0 V

-5.0 -3.5 -2.0 V

42 V

-42 V

40 V

-40 V

3.1 3.5

9.0 10.1

VPk

dBu

-50 ±5

10

+50 mV

20 Ω

-10 0

3

40

+10 mV

20 ohm

dB

-0.1

±0.03 +0.1

dB

-0.1

±0.03 +0.1

dB

-0.1

±0.06 +0.1

dB

-0.15 ±0.1

+0.15 dB

C

+

RL

TIPX

42/27

VTX

32/21

TX

+

VTR

EL –

ILdc PBL 3798

RINGX

43/28

RSN

29/19

RT

RRX

RX

E RX

VTX

–

Figure 6. Frequency response, insertion

loss, gain tracking, idle channel noise,

THD, inter-modulation.

1/ωC << RL, RL = 600 Ω,

RT = 60 kΩ, RRX = 30 kΩ.

4-131

5 Page

PBL 3798

44PLwCwCw3.D2PaLtaCSChePeDt4IUP .coSmymbol

25 —

— RSG

26 19

17 RDC

27 20&21 18 GND1

28 —

— NC

29 22

19 RSN

30 —

31 23

32 24

— NC

20 VEE

21 VTX

33 —

34 25

35 26

36 —

— NC

22 HPT

23 HPR

— NC

Description

Saturation guard programming input. A resistor, RSG, between pins RSG and VEE

adjusts the saturation guard for operation with VBat from -64 V to -46 V. The PBL 3798 in dual-

in-line and 32 pin surface mount package have the saturation guard internally set for operation

with VBat = -48 V.

The constant dc loop current is programmed by two resistors connected in series from this pin

to the receive summing node (RSN). The resistor junction point is decoupled to GND1 to filter

noise and other disturbances before reaching the RSN input. VRDC polarity is negative for normal

tip-ring polarity and positive for reversed tip-ring polarity. |V | = 2.5V in the constant current

RDC

region.

Ground. No internal connection to GND2. Note 2.

No internal connection. Note 1.

Receive summing node. 100 times the current (dc and ac) flowing into this pin equals the

metallic (transversal) current flowing between the TIPX and RINGX terminals. Programming

networks for constant loop current, 2-wire impedance, and receive gain connect to the receive

summing node.

No internal connection. Note 1.

-5 V power supply.

Transmit vf output. The ac voltage difference between TIPX and RINGX, the ac metallic

voltage, is reproduced as an unbalanced GND1 referenced signal at VTX with a gain of one.

The two-wire impedance programming network connects between VTX and RSN.

No internal connection. Note 1.

Tip side (HPT) of ac/dc separation capacitor.

Ring side (HPR) of ac/dc separation capacitor.

No internal connection. Note 1.

TESTRLY 7

L8

NC 9

VBAT 10

VQBAT 11

CHS 12

NC 13

CHCLK 14

NC 15

E1 16

C4 17

39 NC

38 DT

37 RD

36 NC

35 HPR

34 HPT

33 NC

32 VTX

31 VEE

30 NC

29 RSN

GND 2 1

VREG 2

VCC 3

RINGRLY 4

TESTRLY 5

L6

VBAT 7

VQBAT 8

CHS 9

CHCLK 10

C4 11

E1 12

DET 13

C2 14

28 RINGX

27 TIPX

26 DR

25 DT

24 RD

23 HPR

22 HPT

21 VTX

20 VEE

19 RSN

18 GND 1

17 RDC

16 C 1

15 C 3

TP 5

TESTRLY 6

NC 7

VBAT 8

VQBAT 9

CHS 10

CHCLK 11

C4 12

E1 13

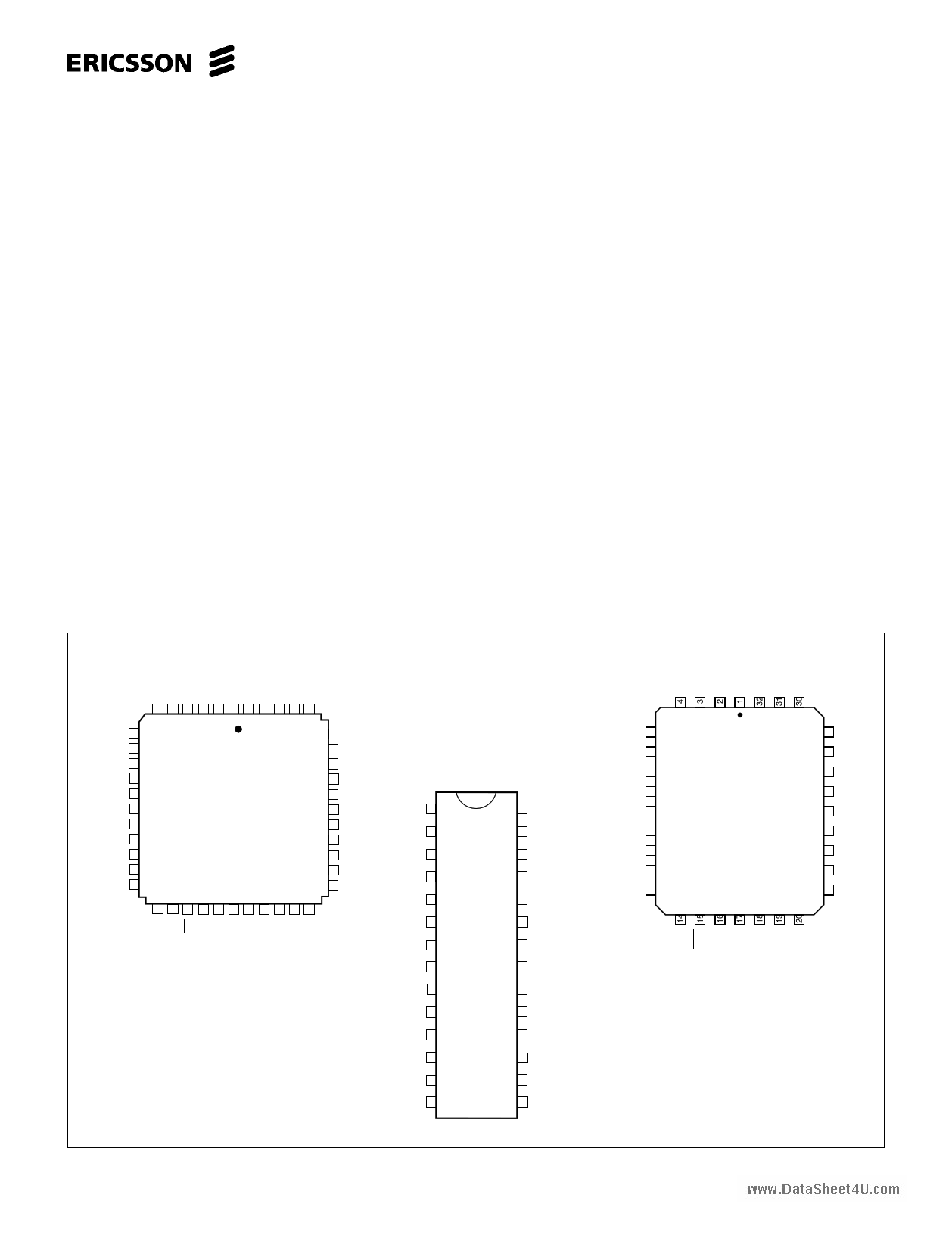

Figure 11. Pin configuration, 44-pin and 32-pin j-leaded chip carrier and 28-pin dual-in-line package, Top view.

29 TP

28 DT

27 RD

26 HPR

25 HPT

24 VTX

23 VEE

22 RSN

21 GND1

4-137

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet PBL3798.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PBL3796 | Subscriber Line Interface Circuit | Ericsson |

| PBL3796-2 | Subscriber Line Interface Circuit | Ericsson |

| PBL3798 | Subscriber Line Interface Circuit | Ericsson |

| PBL3798-2 | Subscriber Line Interface Circuit | Ericsson |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |