|

|

PDF ATTINY88 Data sheet ( Hoja de datos )

| Número de pieza | ATTINY88 | |

| Descripción | (ATTINY48 / ATTINY88) 8-bit Microcontroller | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ATTINY88 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

Features

• High Performance, Low Power AVR® 8-Bit Microcontroller

• Advanced RISC Architecture

– 123 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

www.da–taFshuelleyt4Sut.caotimc Operation

• High Endurance Non-volatile Memory Segments

– 4K/8K Bytes of In-System Self-Programmable Flash program memory(ATtiny48/88)

– 64/64 Bytes EEPROM (ATtiny48/88)

– 256/512 Bytes Internal SRAM (ATtiny48/88)

– Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

– Data retention: 20 years at 85°C / 100 years at 25°C

– Optional Boot Code Section with Indepentent Lock Bits

• In-System Programming by On-chip Boot Program

• True Read-While-Write Operation

– Programming Lock for Software Security

• Peripheral Features

– One 8-bit Timer/Counter with Separate Prescaler and Compare Mode

– One 16-bit Timer/Counter with Prescaler, and Compare and Capture Modes

– 8-channel 10-bit ADC in 32-lead TQFP and 32-pad QFN/MLF package

– 6-channel 10-bit ADC in 28-pin PDIP and 28-pad QFN/MLF package

– Master/Slave SPI Serial Interface

– Byte-oriented 2-wire Serial Interface (Philips I2C Compatible)

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

– Interrupt and Wake-up on Pin Change

• Special Microcontroller Features

– debugWIRE On-chip Debug System

– In-System Programmable via SPI Port

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated Oscillator

– External and Internal Interrupt Sources

– Three Sleep Modes: Idle, ADC Noise Reduction and Power-down

• I/O and Packages

– 28 Programmable I/O Lines in 32-lead TQFP and 32-pad QFN/MLF package

– 24 Programmable I/O Lines in 28-pin PDIP and 28-pad QFN/MLF package

– 28-pin PDIP, 32-lead TQFP, 28-pad QFN/MLF and 32-pad QFN/MLF

• Operating Voltage:

– 1.8 – 5.5V

• Temperature Range:

– -40°C to +85°C

• Speed Grade:

– 0 – 2 MHz @ 1.8 – 5.5V

– 0 – 6 MHz @ 2.7 – 5.5V

– 0 – 12 MHz @ 4.5 – 5.5V

• Low Power Consumption

– Active Mode: 1 MHz, 1.8V: 240µA

– Power-down Mode: 0.1µA at 1.8V

8-bit

Microcontroller

with 4/8K Bytes

In-System

Programmable

Flash

ATtiny48/88

Preliminary

Summary

Rev. 8008BS–AVR–06/08

1 page

ATtiny48/88

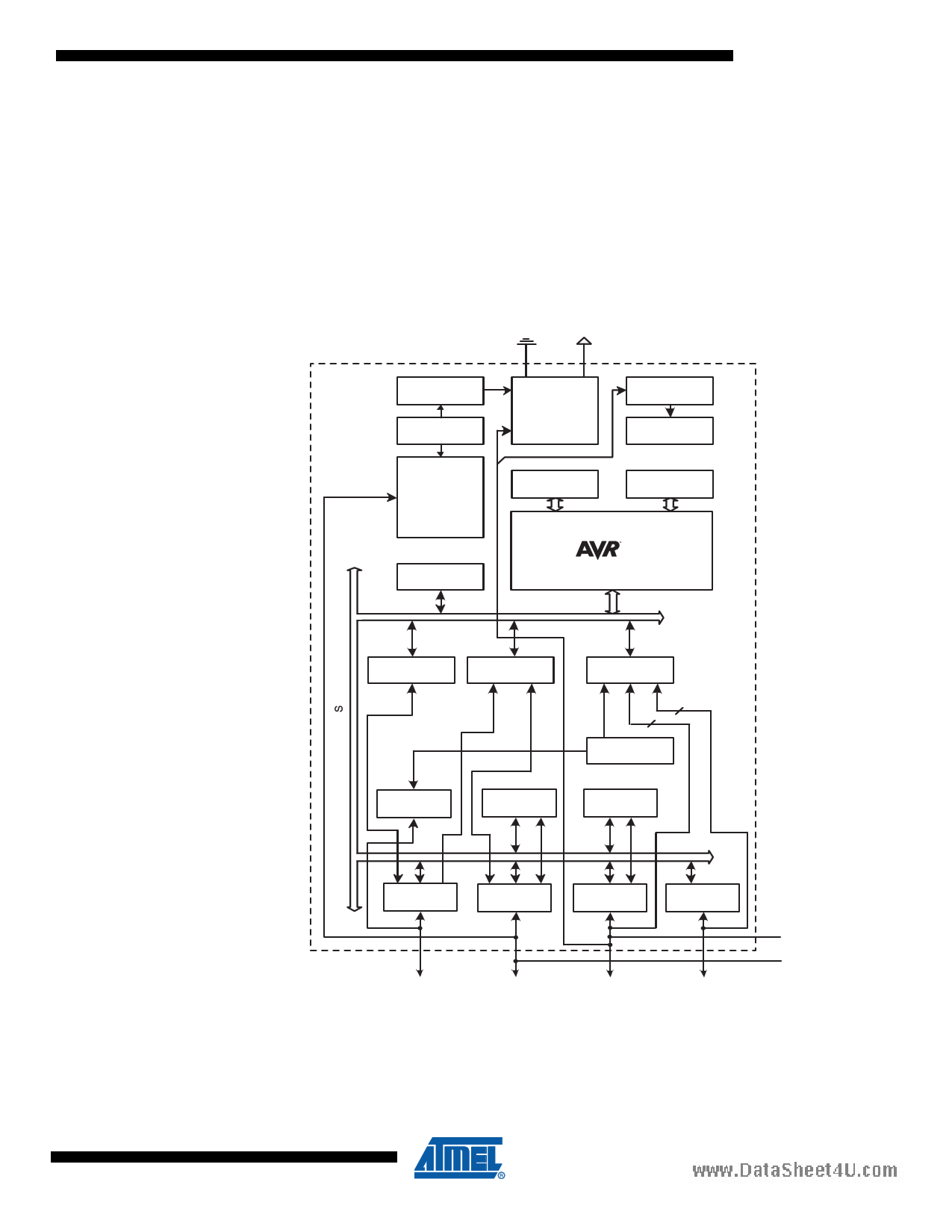

2. Overview

www.datasheet4u.com

The ATtiny48/88 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC

architecture. By executing powerful instructions in a single clock cycle, the ATtiny48/88 achieves

throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power con-

sumption versus processing speed.

2.1 Block Diagram

Figure 2-1. Block Diagram

Watchdog

Timer

Watchdog

Oscillator

Oscillator

Circuits /

Clock

Generation

EEPROM

Power

Supervision

POR / BOD &

RESET

Flash

debugWIRE

Program

Logic

SRAM

CPU

8008BS–AVR–06/08

8bit T/C 0

16bit T/C 1

Analog

Comp.

SPI

A/D Conv.

2

6

Internal

Bandgap

TWI

PORT D (8)

PORT B (8)

PORT C (8)

PORT A (4)

PD[0..7]

PB[0..7]

RESET

CLKI

PC[0..7] PA[0..3] (in TQFP and MLF)

The AVR core combines a rich instruction set with 32 general purpose working registers. All the

32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent

registers to be accessed in one single instruction executed in one clock cycle. The resulting

architecture is more code efficient while achieving throughputs up to ten times faster than con-

ventional CISC microcontrollers.

5

5 Page

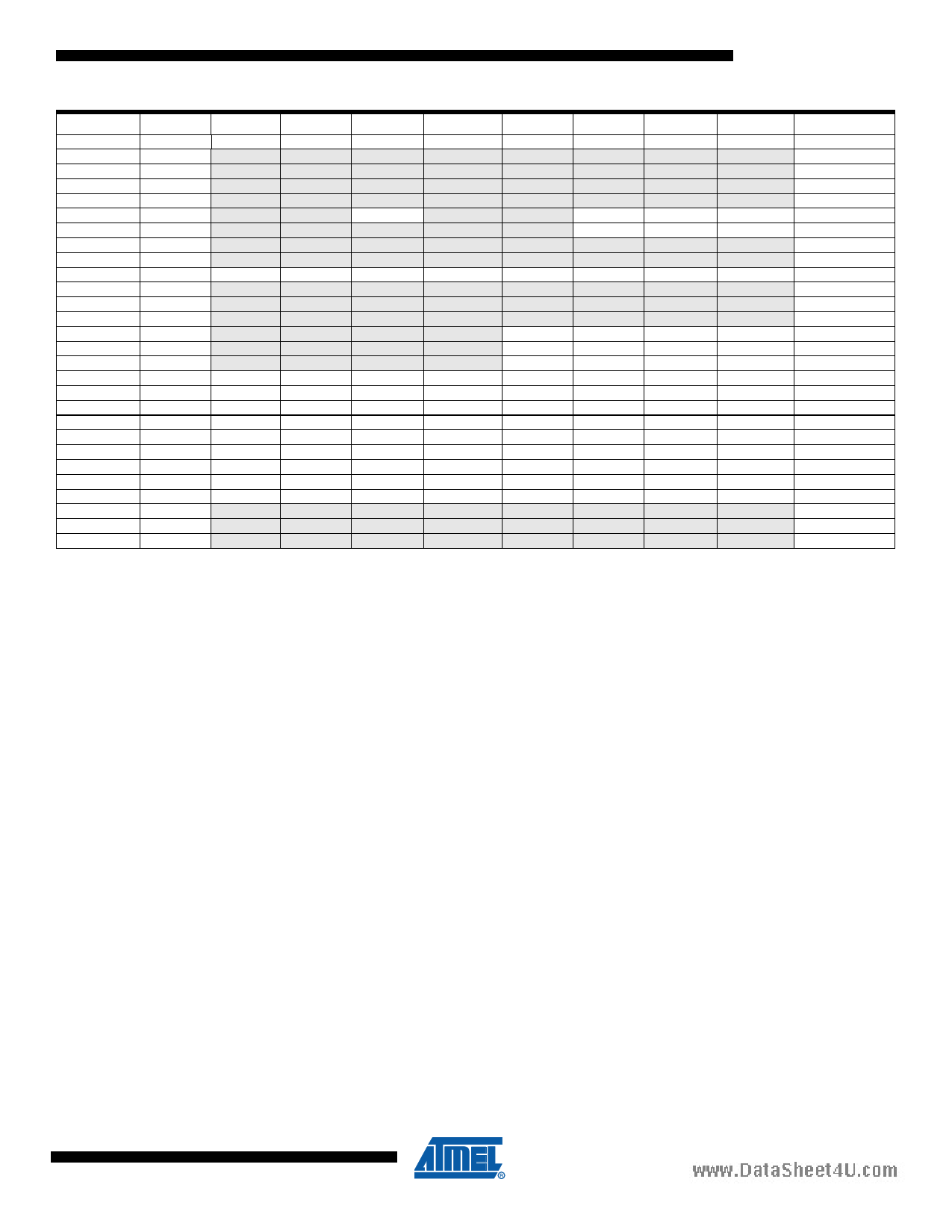

ATtiny48/88

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Page

0x1B (0x3B)

PCIFR

0x1A (0x3A)

Reserved

0x19 (0x39)

Reserved

0x18 (0x38)

Reserved

0x17 (0x37)

Reserved

0x16 (0x36)

TIFR1

www.0dxa15ta(0sxh3e5)et4u.comTIFR0

0x14 (0x34)

Reserved

0x13 (0x33)

Reserved

0x12 (0x32)

PORTCR

0x11 (0x31)

Reserved

0x10 (0x30)

Reserved

0x0F (0x2F)

Reserved

0x0E (0x2E)

PORTA

0x0D (0x2D)

DDRA

0x0C (0x2C)

PINA

0x0B (0x2B)

PORTD

0x0A (0x2A)

DDRD

0x09 (0x29)

PIND

0x08 (0x28)

PORTC

0x07 (0x27)

DDRC

0x06 (0x26)

PINC

0x05 (0x25)

PORTB

0x04 (0x24)

DDRB

0x03 (0x23)

PINB

0x02 (0x22)

Reserved

0x01 (0x21)

Reserved

0x00 (0x20)

Reserved

–

–

–

–

–

–

–

–

–

BBMD

–

–

–

–

–

–

PORTD7

DDD7

PIND7

PORTC7

DDC7

PINC7

PORTB7

DDB7

PINB7

–

–

–

–

–

–

–

–

–

–

–

–

BBMC

–

–

–

–

–

–

PORTD6

DDD6

PIND6

PORTC6

DDC6

PINC6

PORTB6

DDB6

PINB6

–

–

–

–

–

–

–

–

ICF1

–

–

–

BBMB

–

–

–

–

–

–

PORTD5

DDD5

PIND5

PORTC5

DDC5

PINC5

PORTB5

DDB5

PINB5

–

–

–

–

–

–

–

–

–

–

–

–

BBMA

–

–

–

–

–

–

PORTD4

DDD4

PIND4

PORTC4

DDC4

PINC4

PORTB4

DDB4

PINB4

–

–

–

PCIF3

–

–

–

–

–

–

–

–

PUDD

–

–

–

PORTA3

DDA3

PINA3

PORTD3

DDD3

PIND3

PORTC3

DDC3

PINC3

PORTB3

DDB3

PINB3

–

–

–

PCIF2

–

–

–

–

OCF1B

OCF0B

–

–

PUDC

–

–

–

PORTA2

DDA2

PINA2

PORTD2

DDD2

PIND2

PORTC2

DDC2

PINC2

PORTB2

DDB2

PINB2

–

–

–

PCIF1

–

–

–

–

OCF1A

OCF0A

–

–

PUDB

–

–

–

PORTA1

DDA1

PINA1

PORTD1

DDD1

PIND1

PORTC1

DDC1

PINC1

PORTB1

DDB1

PINB1

–

–

–

PCIF0

–

–

–

–

TOV1

TOV0

–

–

PUDA

–

–

–

PORTA0

DDA0

PINA0

PORTD0

DDD0

PIND0

PORTC0

DDC0

PINC0

PORTB0

DDB0

PINB0

–

–

–

53

110

82

72

74

74

74

74

74

74

73

73

74

73

73

73

Note: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses

should never be written.

2. I/O Registers within the address range 0x00 – 0x1F are directly bit-accessible using the SBI and CBI instructions. In these

registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

3. Some of the Status Flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI

instructions will only operate on the specified bit, and can therefore be used on registers containing such Status Flags. The

CBI and SBI instructions work with registers 0x00 to 0x1F only.

4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 – 0x3F must be used. When addressing I/O

Registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATtiny48/88 is a com-

plex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN

and OUT instructions. For the Extended I/O space from 0x60 – 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD

instructions can be used.

8008BS–AVR–06/08

11

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet ATTINY88.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ATtiny828 | 8-bit AVR Microcontroller | ATMEL Corporation |

| ATTINY84 | (ATTINYx4) 8-bit Microcontroller | ATMEL Corporation |

| ATtiny841 | 8-bit AVR Microcontroller | ATMEL Corporation |

| ATTINY84A | 8-bit Microcontroller | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |