|

|

PDF AT88SA10HS Data sheet ( Hoja de datos )

| Número de pieza | AT88SA10HS | |

| Descripción | Host Security Chip | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT88SA10HS (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

Features

• Secure key storage to complement AT88SA100S and AT88SA102S

Devices

• Superior SHA-256 Hash Algorithm

• Guaranteed Unique 48 bit Serial Number

• High speed single wire interface, optionally shared with client

• Supply Voltage: 2.5 – 5.5V

• 1.8V – 5.5V communications voltage

• <100nA Sleep Current

• 4KV ESD protection

• Multi-level hardware security

• Secure personalization

• Green compliant (exceeds RoHS) 3 pin SOT-23 package

Applications

• Consumable device (battery, toner, other supplies) authentication

• Network & Computer Access control

• Authenticated communications for control networks

• Anti-clone authentication for daughter cards

• Physical access control (electronic lock & key)

1. Introduction

The CryptoAuthentication family of chips are the first cost-effective

authentication devices to implement the SHA-256 hash algorithm,

which is part of the latest set of recommended algorithms by the US

Government. The 256 bit key space renders any exhaustive attacks

impossible.

The AT88SA10HS host version of CryptoAuthentication chips is

www.DataSheet4cUap.caobmle of validating the response coming from the SHA-256

engine within an authentic CryptoAuthentication client (SA100S or

SA102S), even if that response includes within the computation the

serial number of the client. For detailed information on the

cryptographic protocols, algorithm test values and usage models,

refer to “AT88SA100S” and “AT88SA102S” Datasheets, along with

the application notes dedicated to this product family.

The host CryptoAuthentication performs 3 separate operations

(named HOST0, HOST1 & HOST2) to implement this validation.

The AT88SA10HS chip takes both the challenge and response as

inputs and returns a single Boolean indicating whether or not the

response is valid, in order to prevent the host chip from being used

to model a valid client.

The host system is responsible for generating the random challenge

that is sent to both the client and host CryptoAuthentication devices

as the AT88SA10HS does not include a random number generator.

CryptoAuthentication™

Host Security Chip

AT88SA10HS

Preliminary

8595B–SMEM–09/09

1 page

AT88SA10HS Host Authentication Chip [Preliminary]

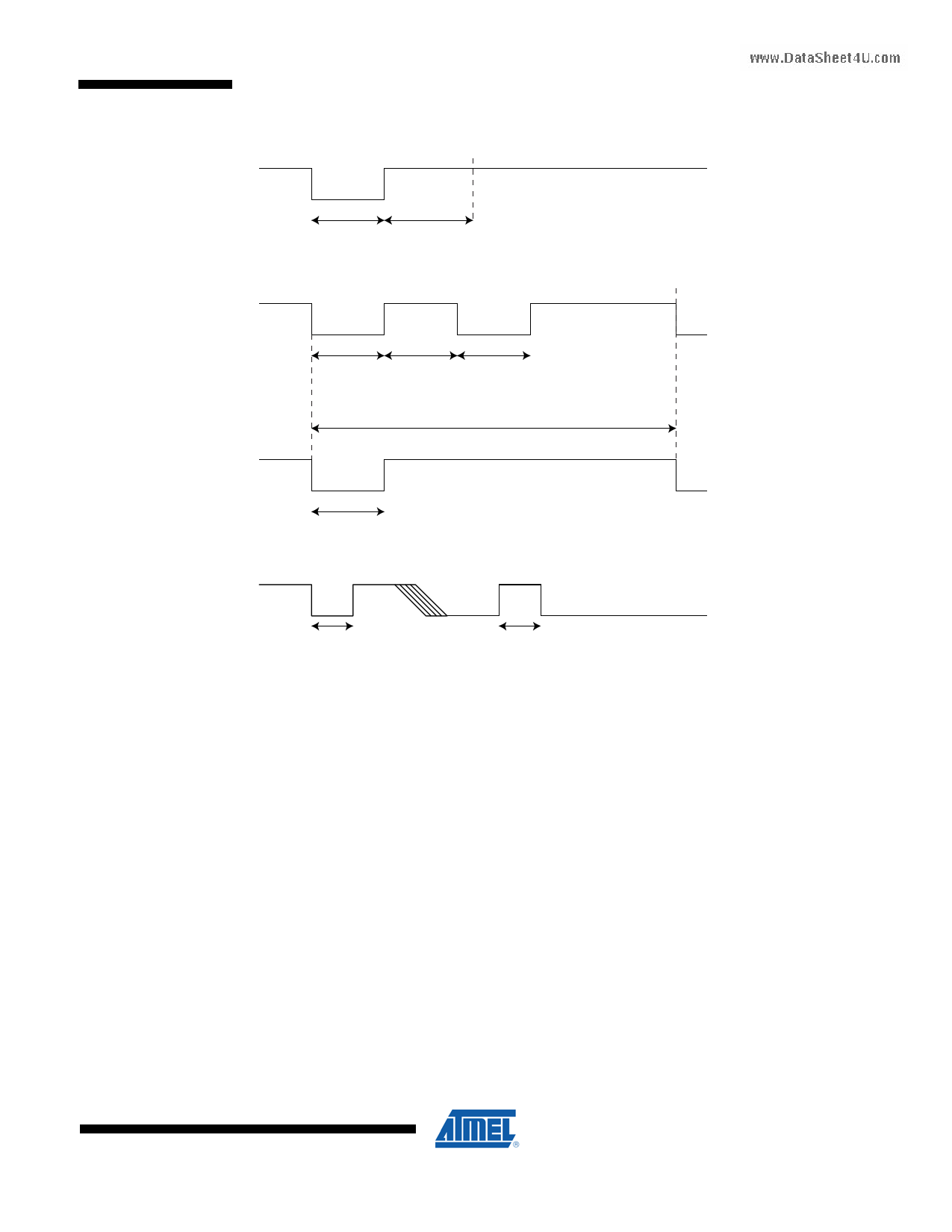

2.2. AC Parameters

WAKE

data comm

tWLO

tWHI

LOGIC Ø

LOGIC 1

NOISE

SUPPRESION

tSTART

tZHI

tZLO

tBIT

tSTART

tLIGNORE

tHIGNORE

www.DataSheet4U.com

8595B–SMEM–09/09

5

5 Page

AT88SA10HS Host Authentication Chip [Preliminary]

3.4.1.

IO Timeout

After a leading transition for any data token has been received, the AT88SA10HS will expect another token to be

transmitted within a tTIMEOUT interval. If the leading edge of the next token is not received within this period of time, the

AT88SA10HS assumes that the synchronization with the host is lost and transitions to a sleep state.

After the AT88SA10HS receives the last bit of a command block, this timeout circuitry is disabled. If the command is

properly formatted, then it is re-enabled with the first transmit token that occurs after tPARSE + tEXEC. If there is an error

in the command, then it is re-enabled with the first transmit token that occurs after tPARSE.

In order to limit the active current if the AT88SA10HS is inadvertently awakened, the IO timeout is also enabled when

the AT88SA10HS wakes up. If the first token does not come within the tTIMEOUT interval, then the AT88SA10HS will go

back to sleep without performing any operations.

3.4.2.

Synchronization Procedures

When the system and the AT88SA10HS fall out of synchronization, the system will ultimately end up sending a transmit

flag which will not generate a response from the AT88SA10HS. The system should implement its own timeout which

waits for tTIMEOUT during which time the AT88SA10HS should go to sleep automatically. At this point, the system should

send a Wake token and after tWLO + tWHI, a Transmit token. The 0x11 status indicates that the resynchronization was

successful.

It may be possible that the system does not get the 0x11 code from the AT88SA10HS for one of the following reasons:

1. The system did not wait a full tTIMEOUT delay with the IO signal idle in which case the AT88SA10HS may have

interpreted the Wake token and Transmit flag as data bits. Recommended resolution is to wait twice the tTIMEOUT

delay and re-issue the Wake token.

2. The AT88SA10HS went into the sleep mode for some reason while the system was transmitting data. In this case,

the AT88SA10HS will interpret the next data bit as a wake token, but ignore some of the subsequently transmitted

bits during its wake-up delay. If any bytes are transmitted after the wake-up delay, they may be interpreted as a

legal flag, though the following bytes would not be interpreted as a legal command due to an incorrect count or the

lack of a correct CRC. Recommended resolution is to wait the tTIMEOUT delay and re-issue the Wake token.

3. There are some internal error conditions within the AT88SA10HS which will be automatically reset after a t

WATCHDOG interval, see below. There is no way to externally reset the AT88SA10HS – the system should leave the

IO pin idle for this interval and issue the Wake token.

3.5. Watchdog Failsafe

www.DataSheet4AUft.ecromthe Wake token has been received by the AT88SA10HS, a watchdog counter is started within the chip. After

t WATCHDOG, the chip will enter sleep mode, regardless of whether it is in the middle of execution of a command and/or

whether some IO transmission is in progress. There is no way to reset the counter other than to put the chip to sleep

and wake it up again.

This is implemented as a fail-safe so that no matter what happens on either the system side or inside the various state

machines of the AT88SA10HS including any IO synchronization issue, power consumption will fall to the low sleep

level automatically.

3.6.

Byte & Bit Ordering

The AT88SA10HS is a little-endian chip:

• All multi-byte aggregate elements within this spec are treated as arrays of bytes and are processed in the order

received.

• Data is transferred to/from the AT88SA10HS least significant bit first on the bus.

• In this document, the most significant bit and/or byte appears towards the left hand side of the page.

8595B–SMEM–09/09

11

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet AT88SA10HS.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT88SA10HS | Host Security Chip | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |