|

|

PDF 74AVCH20T245 Data sheet ( Hoja de datos )

| Número de pieza | 74AVCH20T245 | |

| Descripción | 20-bit Dual Supply Translating Transceiver | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74AVCH20T245 (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

74AVCH20T245

20-bit dual supply translating transceiver with configurable

voltage translation; 3-state

Rev. 01 — 13 January 2010

Product data sheet

1. General description

The 74AVCH20T245 is a 20-bit, dual supply transceiver that enables bi-directional voltage

level translation. The device can be used as two 10-bit transceivers or as a single 20-bit

transceiver. It features four 10-bit input-output ports (1An, 1Bn and 2An, 2Bn), two output

enable inputs (nOE), two direction inputs (DIR) and dual supplies (VCC(A) and VCC(B)).

VCC(A) and VCC(B) can be independently supplied at any voltage between 0.8 V and 3.6 V

making the device suitable for bi-directional voltage level translation between any of the

low voltage nodes: 0.8 V, 1.2 V, 1.5 V, 1.8 V, 2.5 V and 3.3 V. The 1An and 2An ports, nOE

and nDIR are referenced to VCC(A), the 1Bn and 2Bn ports are referenced to VCC(B). A

HIGH on a 1DIR allows transmission from 1An to 1Bn and a LOW on 1DIR allows

transmission from 1Bn to 1An. A HIGH on nOE causes the outputs to assume a HIGH

impedance OFF-state.

The device is fully specified for partial power-down applications using IOFF. The IOFF

circuitry disables the output, preventing any damaging backflow current through the

device when it is powered down. In suspend mode when either VCC(A) or VCC(B) are at

GND level, all output ports will assume a high impedance OFF-state. The bus hold

circuitry on the powered-up side always stays active.

2. Features

www.DataSheet4U.com

Wide supply voltage range:

VCC(A): 0.8 V to 3.6 V

VCC(B): 0.8 V to 3.6 V

Complies with JEDEC standards:

JESD8-12 (0.8 V to 1.3 V)

JESD8-11 (0.9 V to 1.65 V)

JESD8-7 (1.2 V to 1.95 V)

JESD8-5 (1.8 V to 2.7 V)

JESD8-B (2.7 V to 3.6 V)

ESD protection:

HBM JESD22-A114E Class 3B exceeds 8000 V

MM JESD22-A115-A exceeds 200 V

CDM JESD22-C101C exceeds 1000 V

Maximum data rates:

380 Mbit/s (≥ 1.8 V to 3.3 V translation)

260 Mbit/s (≥ 1.1 V to 3.3 V translation)

260 Mbit/s (≥ 1.1 V to 2.5 V translation)

1 page

NXP Semiconductors

74AVCH20T245

20-bit dual supply translating transceiver; 3-state

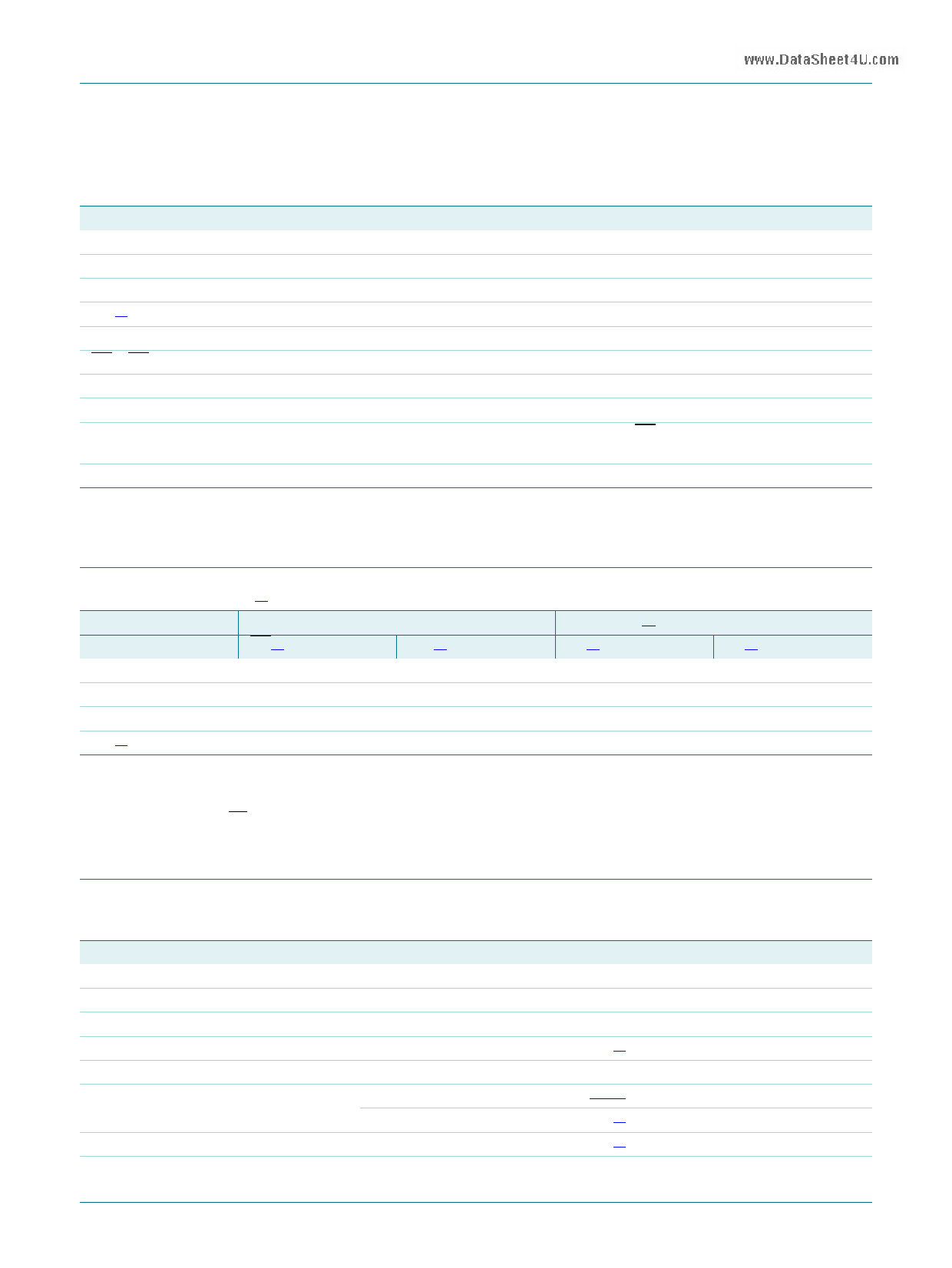

5.2 Pin description

Table 2. Pin description

Symbol

Pin

1DIR, 2DIR

1, 28

1B1 to 1B10

2, 3, 5, 6, 8, 9, 10, 12, 13, 14

2B1 to 2B10

15, 16, 17, 19, 20, 21, 23, 24, 26, 27

GND[1]

4, 11, 18, 25, 32, 39, 46, 53

VCC(B)

1OE, 2OE

7, 22

56, 29

1A1 to 1A10

55, 54, 52, 51, 49, 48, 47, 45, 44, 43

2A1 to 2A10

42, 41, 40, 38, 37, 36, 34, 33, 31, 30

VCC(A)

35, 50

n.c. -

[1] All GND pins must be connected to ground (0 V).

Description

direction control

data input or output

data input or output

ground (0 V)

supply voltage B (nBn inputs are referenced to VCC(B))

output enable input (active LOW)

data input or output

data input or output

supply voltage A (nAn, nOE and nDIR inputs are referenced

to VCC(A))

not connected

6. Functional description

Table 3. Function table[1]

Supply voltage

Input

VCC(A), VCC(B)

0.8 V to 3.6 V

nOE[3]

L

0.8 V to 3.6 V

L

0.8 V to 3.6 V

H

GND[2]

X

nDIR[3]

L

H

X

X

Input/output[2]

nAn[3]

nAn = nBn

input

Z

Z

nBn[3]

input

nBn = nAn

Z

Z

w w [w1] . HD= Ha IGt HavoSltaghe leeveel; Lt =4LOUW. vocltaogemlevel; X = don’t care; Z = high-impedance OFF-state.

[2] If at least one of VCC(A) or VCC(B) is at GND level, the device goes into suspend mode.

[3] The nAn, nDIR and nOE input circuit is referenced to VCC(A); The nBn input circuit is referenced to VCC(B).

7. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

Symbol Parameter

Conditions

Min Max Unit

VCC(A)

VCC(B)

IIK

VI

IOK

VO

supply voltage A

supply voltage B

input clamping current

input voltage

output clamping current

output voltage

VI < 0 V

VO < 0 V

Active mode

Suspend or 3-state mode

−0.5

−0.5

−50

[1] −0.5

−50

[1][2][3] −0.5

[1] −0.5

+4.6

+4.6

-

+4.6

-

VCCO + 0.5

+4.6

V

V

mA

V

mA

V

V

IO output current

ICC supply current

VO = 0 V to VCCO

ICC(A) or ICC(B)

[2] -

±50 mA

- 100 mA

74AVCH20T245_1

Product data sheet

Rev. 01 — 13 January 2010

© NXP B.V. 2010. All rights reserved.

5 of 25

5 Page

NXP Semiconductors

74AVCH20T245

20-bit dual supply translating transceiver; 3-state

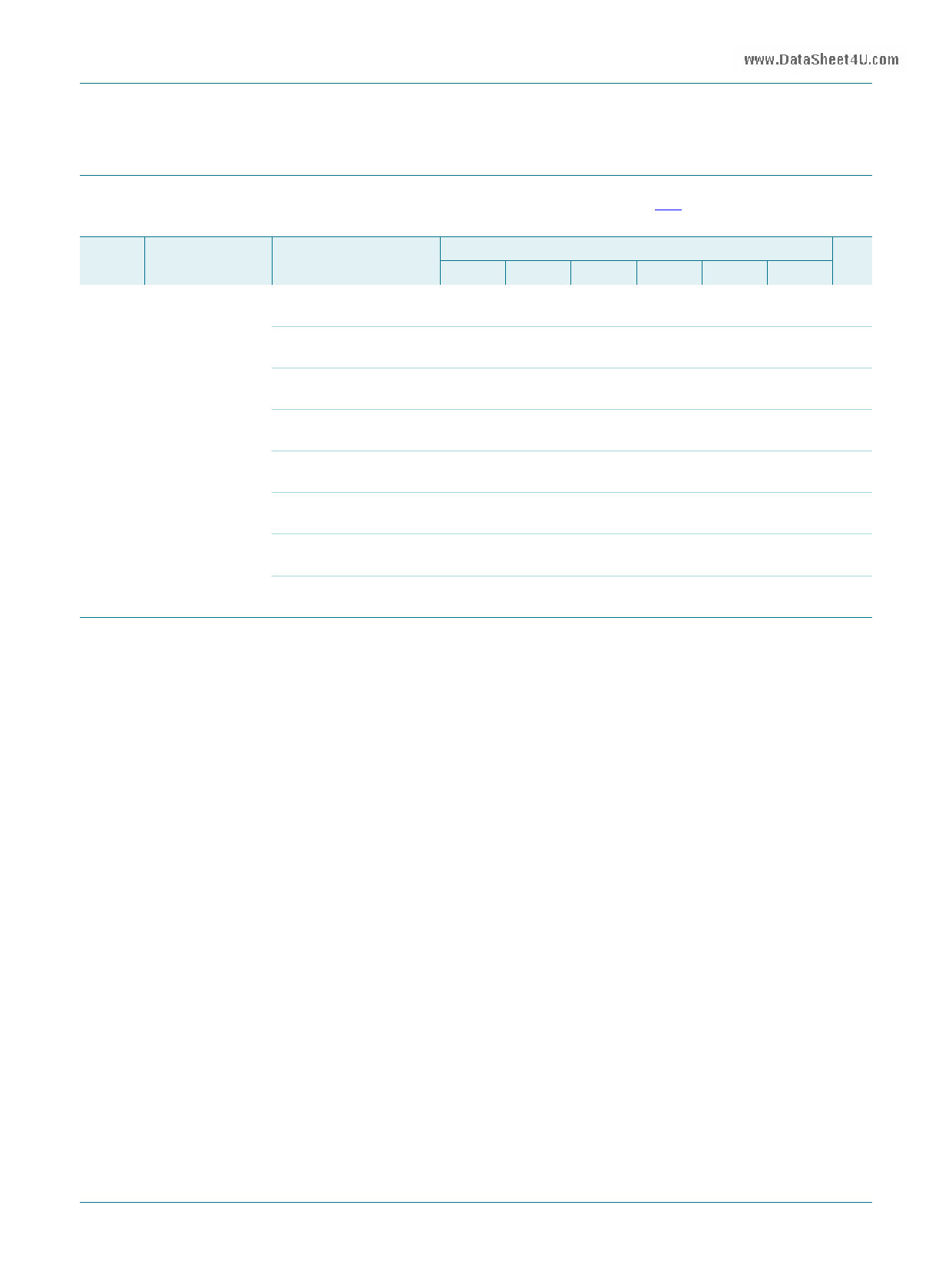

10. Dynamic characteristics

Table 9. Typical power dissipation capacitance at VCC(A) = VCC(B) and Tamb = 25 °C [1][2]

Voltages are referenced to GND (ground = 0 V).

Symbol Parameter

Conditions

0.8 V

1.2 V

VCC(A) = VCC(B)

1.5 V 1.8 V

CPD power dissipation A port: (direction A to B); 0.2 0.2 0.2 0.2

capacitance

output enabled

A port: (direction A to B); 0.2 0.2 0.2 0.2

output disabled

A port: (direction B to A); 9.5 9.7 9.8 9.9

output enabled

A port: (direction B to A); 0.6 0.6 0.6 0.6

output disabled

B port: (direction A to B); 9.5 9.7 9.8 9.9

output enabled

B port: (direction A to B); 0.6 0.6 0.6 0.6

output disabled

B port: (direction B to A); 0.2 0.2 0.2 0.2

output enabled

B port: (direction B to A); 0.2 0.2 0.2 0.2

output disabled

[1] CPD is used to determine the dynamic power dissipation (PD in μW).

PD = CPD × VCC2 × fi × N + Σ(CL × VCC2 × fo) where:

fi = input frequency in MHz;

fo = output frequency in MHz;

CL = load capacitance in pF;

VCC = supply voltage in V;

N = number of inputs switching;

www.DataSΣh(eCeLt4×UV.CcoC2m× fo) = sum of the outputs.

[2] fi = 10 MHz; VI = GND to VCC; tr = tf = 1 ns; CL = 0 pF; RL = ∞ Ω.

2.5 V

0.3

0.3

10.7

0.7

10.7

0.7

0.3

0.3

3.3 V

0.4

Unit

pF

0.4 pF

11.9 pF

0.7 pF

11.9 pF

0.7 pF

0.4 pF

0.4 pF

74AVCH20T245_1

Product data sheet

Rev. 01 — 13 January 2010

© NXP B.V. 2010. All rights reserved.

11 of 25

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet 74AVCH20T245.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74AVCH20T245 | 20-bit Dual Supply Translating Transceiver | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |