|

|

PDF HYS72T512341HKP-3.7-B Data sheet ( Hoja de datos )

| Número de pieza | HYS72T512341HKP-3.7-B | |

| Descripción | 240-Pin Registered DDR2 SDRAM Modules | |

| Fabricantes | Qimonda | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HYS72T512341HKP-3.7-B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

December 2006

www.DataSheet4U.com

HYS72T512341HHP–[3.7/5]–B

HYS72T512341HJP–[3.7/5]–B

HYS72T512341HKP–[3.7/5]–B

240-Pin Registered DDR2 SDRAM Modules

DDR2 SDRAM

RoHs Compliant Products

Internet Data Sheet

Rev. 1.0

1 page

Internet Data Sheet

www.DataSheet4U.com

HYS72T512341H[H/J/K]P-[3.7/5]-B

Registered DDR2 SDRAM Modules

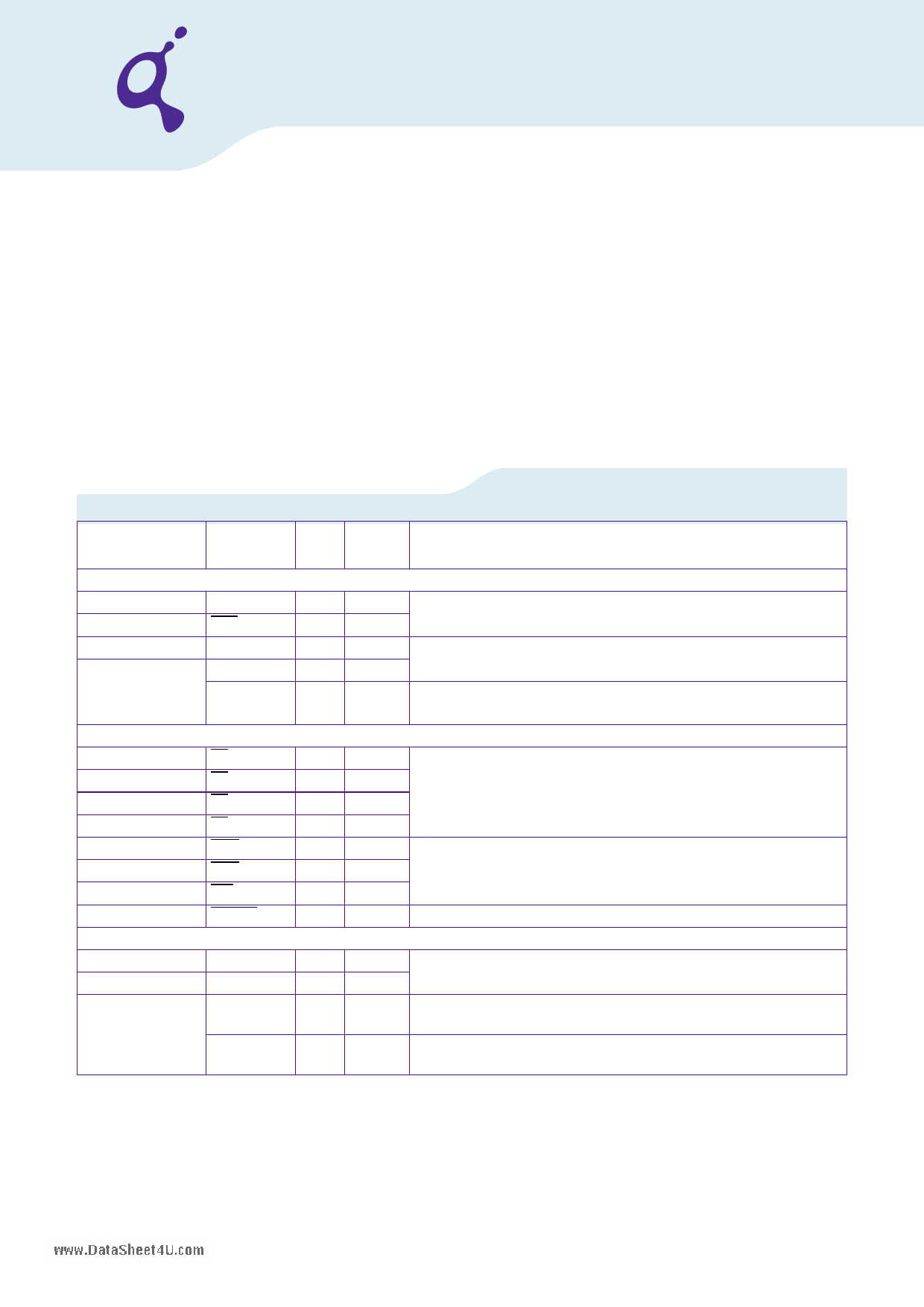

2 Pin Configuration

2.1 Pin Configuration

The pin configuration of the Registered DDR2 SDRAM DIMM

is listed by function in Table 5 (240 pins). The abbreviations

used in columns Pin and Buffer Type are explained in Table 6

and Table 7 respectively. The pin numbering is depicted in

Figure 1.

Pin No.

Name

Clock Signals

185

186

52

171

CK0

CK0

CKE0

CKE1

NC

Control Signals

193

76

220

221

192

74

73

18

Address Signals

71

190

54

S0

S1

S2

S3

RAS

CAS

WE

RESET

BA0

BA1

BA2

NC

Pin Buffer Function

Type Type

TABLE 5

Pin Configuration of RDIMM

I SSTL Clock Signal CK0, Complementary Clock Signal CK0

I SSTL

I SSTL Clock Enables 1:0

I SSTL Note: 2-Ranks module

NC —

Not Connected

Note: 1-Rank module

I SSTL Chip Select Rank 3:0

I SSTL

I SSTL

I SSTL

I SSTL Row Address Strobe (RAS), Column Address Strobe (CAS), Write

I SSTL Enable (WE)

I SSTL

I CMOS Register Reset

I SSTL Bank Address Bus 1:0

I SSTL

I SSTL Bank Address Bus 2

Greater than 512Mb DDR2 SDRAMS

I SSTL Not Connected

Less than 1Gb DDR2 SDRAMS

Rev. 1.0, 2006-12

11032006-VX0M-M6IH

5

5 Page

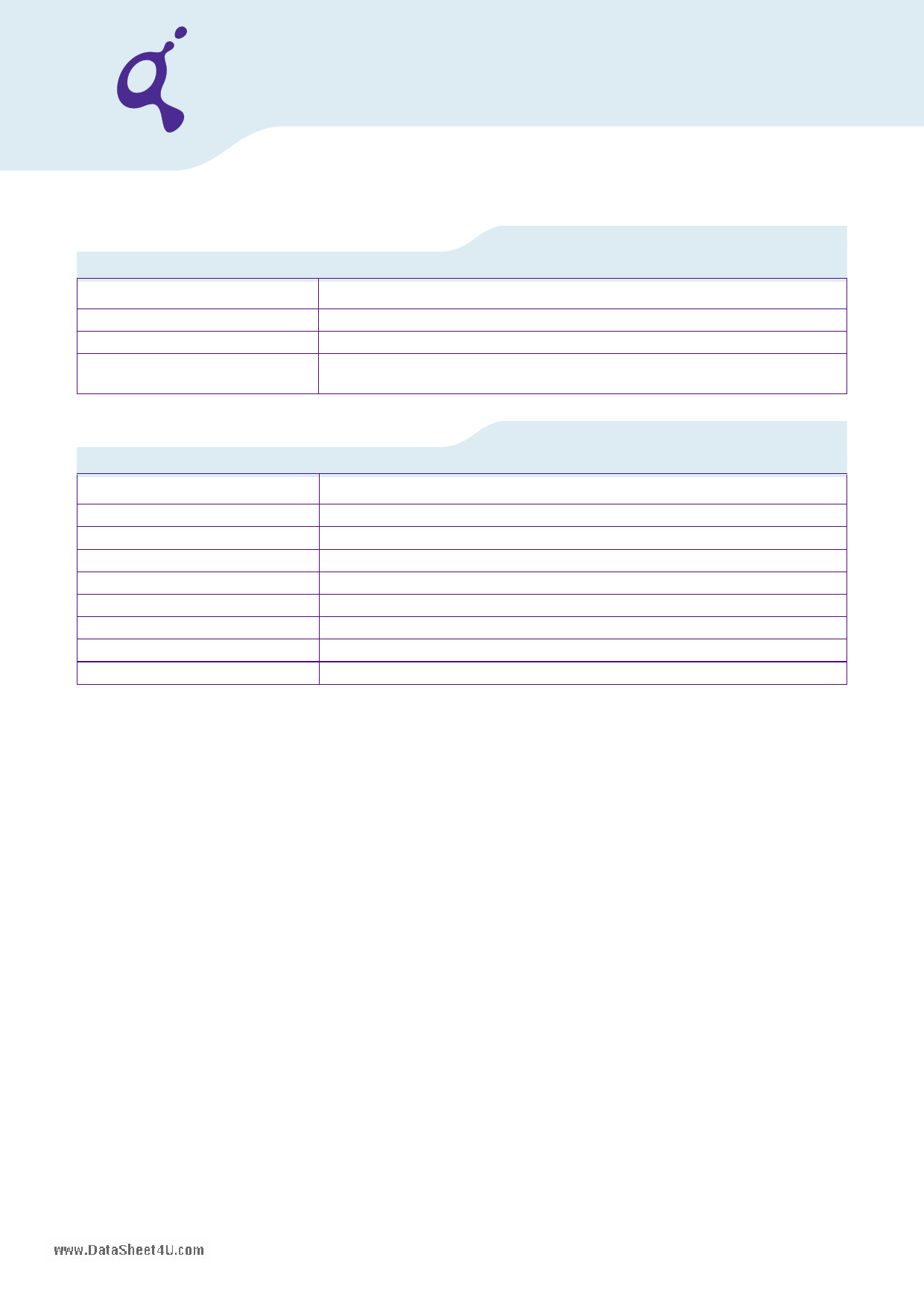

Abbreviation

SSTL

CMOS

OD

Abbreviation

I

O

I/O

AI

PWR

GND

NU

NC

Internet Data Sheet

www.DataSheet4U.com

HYS72T512341H[H/J/K]P-[3.7/5]-B

Registered DDR2 SDRAM Modules

TABLE 6

Abbreviations for Buffer Type

Description

Serial Stub Terminated Logic (SSTL_18)

CMOS Levels

Open Drain. The corresponding pin has 2 operational states, active low and tristate,

and allows multiple devices to share as a wire-OR.

Description

Standard input-only pin. Digital levels.

Output. Digital levels.

I/O is a bidirectional input/output signal.

Input. Analog levels.

Power

Ground

Not Usable

Not Connected

TABLE 7

Abbreviations for Pin Type

Rev. 1.0, 2006-12

11032006-VX0M-M6IH

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HYS72T512341HKP-3.7-B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HYS72T512341HKP-3.7-B | 240-Pin Registered DDR2 SDRAM Modules | Qimonda |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |