|

|

PDF PCA9510A Data sheet ( Hoja de datos )

| Número de pieza | PCA9510A | |

| Descripción | Hot swappable I2C-bus and SMBus bus buffer | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PCA9510A (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

PCA9510A

www.DataSheet4U.com

Hot swappable I2C-bus and SMBus bus buffer

Rev. 01 — 8 September 2005

Product data sheet

1. General description

The PCA9510A is a hot swappable I2C-bus and SMBus buffer that allows I/O card

insertion into a live backplane without corrupting the data and clock buses. Control

circuitry prevents the backplane from being connected to the card until a stop command or

bus idle occurs on the backplane without bus contention on the card. When the

connection is made, the PCA9510A provides bidirectional buffering, keeping the

backplane and card capacitances isolated.

The PCA9510A has no rise time accelerator circuitry to prevent interference when there

are multiple devices in the same system. The PCA9510A incorporates a digital ENABLE

input pin, which enables the device when asserted HIGH and forces the device into a Low

current mode when asserted LOW, and an open-drain READY output pin, which indicates

that the backplane and card sides are connected together (HIGH) or not (LOW).

During insertion, the PCA9510A SDAIN and SCLIN pins (inputs only) are precharged to

1 V to minimize the current required to charge the parasitic capacitance of the chip.

Remark: The dynamic offset design of the PCA9510A/11A/12A/13A/14A I/O drivers allow

them to be connected to another PCA9510A/11A/12A/13A/14A device in series or in

parallel and to the A side of the PCA9517. The PCA9510A/11A/12A/13A/14A cannot

connect to the static offset I/Os used on the PCA9515/15A/16/16A/18 or PCA9517 B side

or P82B96 Sx/y side.

2. Features

s Bidirectional buffer for SDA and SCL lines increases fanout and prevents SDA and

SCL corruption during live board insertion and removal from multi-point backplane

systems

s Compatible with I2C-bus Standard mode, I2C-bus Fast mode, and SMBus standards

s Active HIGH ENABLE input

s Active HIGH READY open-drain output

s High-impedance SDAn and SCLn pins for VCC = 0 V

s 1 V precharge on SDAIN and SCLIN inputs

s Supports clock stretching and multiple master arbitration and synchronization

s Operating power supply voltage range: 2.7 V to 5.5 V

s I/Os are not 5.5 V tolerant

s 0 Hz to 400 kHz clock frequency

s ESD protection exceeds 2000 V HBM per JESD22-A114, 200 V MM per

JESD22-A115, and 1000 V CDM per JESD22-C101

s Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

s Packages offered: SO8, TSSOP8 (MSOP8)

1 page

Philips Semiconductors

PCA9510Awww.DataSheet4U.com

Hot swappable I2C-bus and SMBus bus buffer

is activated during the initialization and is deactivated when the connection is made. The

precharge circuitry pulls up the SDAIN and SCLIN input pins to 1 V through individual

100 kΩ nominal resistors. This precharges the pins to 1 V to minimize the worst case

disturbances that result from inserting a card into the backplane where the backplane and

the card are at opposite logic levels.

8.2 Connect circuitry

Once the connection circuitry is activated, the behavior of SDAIN and SDAOUT as well as

SCLIN and SCLOUT become identical with each acting as a bidirectional buffer that

isolates the input capacitance from the output bus capacitance while communicating the

logic levels. A LOW forced on either SDAIN or SDAOUT will cause the other pin to be

driven to a LOW by the part. The same is also true for the SCLn pins. Noise between

0.7VCC and VCC is generally ignored because a falling edge is only recognized when it

falls below 0.7VCC with a slew rate of at least 1.25 V/µs. When a falling edge is seen on

one pin, the other pin in the pair turns on a pull-down driver that is referenced to a small

voltage above the falling pin. The driver will pull the pin down at a slew rate determined by

the driver and the load initially, because it does not start until the first falling pin is below

0.7VCC. The first falling pin may have a fast or slow slew rate, if it is faster than the

pull-down slew rate then the initial pull-down rate will continue. If the first falling pin has a

slow slew rate then the second pin will be pulled down at its initial slew rate only until it is

just above the first pin voltage then they will both continue down at the slew rate of the

first.

Once both sides are LOW they will remain LOW until all the external drivers have stopped

driving LOWs. If both sides are being driven LOW to the same value for instance, 10 mV

by external drivers, which is the case for clock stretching and is typically the case for

acknowledge, and one side external driver stops driving that pin will rise until the internal

driver pulls it down to the offset voltage. When the last external driver stops driving a

LOW, that pin will rise up and settle out just above the other pin as both rise together with

a slew rate determined by the internal slew rate control and the RC time constant. As long

as the slew rate is at least 1.25 V/µs, when the pin voltage exceeds 0.6 V for the

PCA9510A, the pull-down driver is turned off.

8.3 Maximum number of devices in series

Each buffer adds about 0.1 V dynamic level offset at 25 °C with the offset larger at higher

temperatures. Maximum offset (Voffset) is 0.150 V with a 10 kΩ pull-up resistor. The LOW

level at the signal origination end (master) is dependent upon the load and the only

specification point is the I2C-bus specification of 3 mA will produce VOL < 0.4 V, although if

lightly loaded the VOL may be ∼0.1 V. Assuming VOL = 0.1 V and Voffset = 0.1 V, the level

after four buffers would be 0.5 V, which is only about 0.1 V below the threshold of the

rising edge accelerator (about 0.6 V). With great care a system with four buffers may

work, but as the VOL moves up from 0.1 V, noise or bounces on the line will result in firing

the rising edge accelerator thus introducing false clock edges. Generally it is

recommended to limit the number of buffers in series to two, and to keep the load light to

minimize the offset.

The PCA9510A (rise time accelerator is permanently disabled) and the PCA9512A (rise

time accelerator can be turned off) are a little different with the rise time accelerator turned

off because the rise time accelerator will not pull the node up, but the same logic that turns

PCA9510A_1

Product data sheet

Rev. 01 — 8 September 2005

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

5 of 23

5 Page

Philips Semiconductors

PCA9510Awww.DataSheet4U.com

Hot swappable I2C-bus and SMBus bus buffer

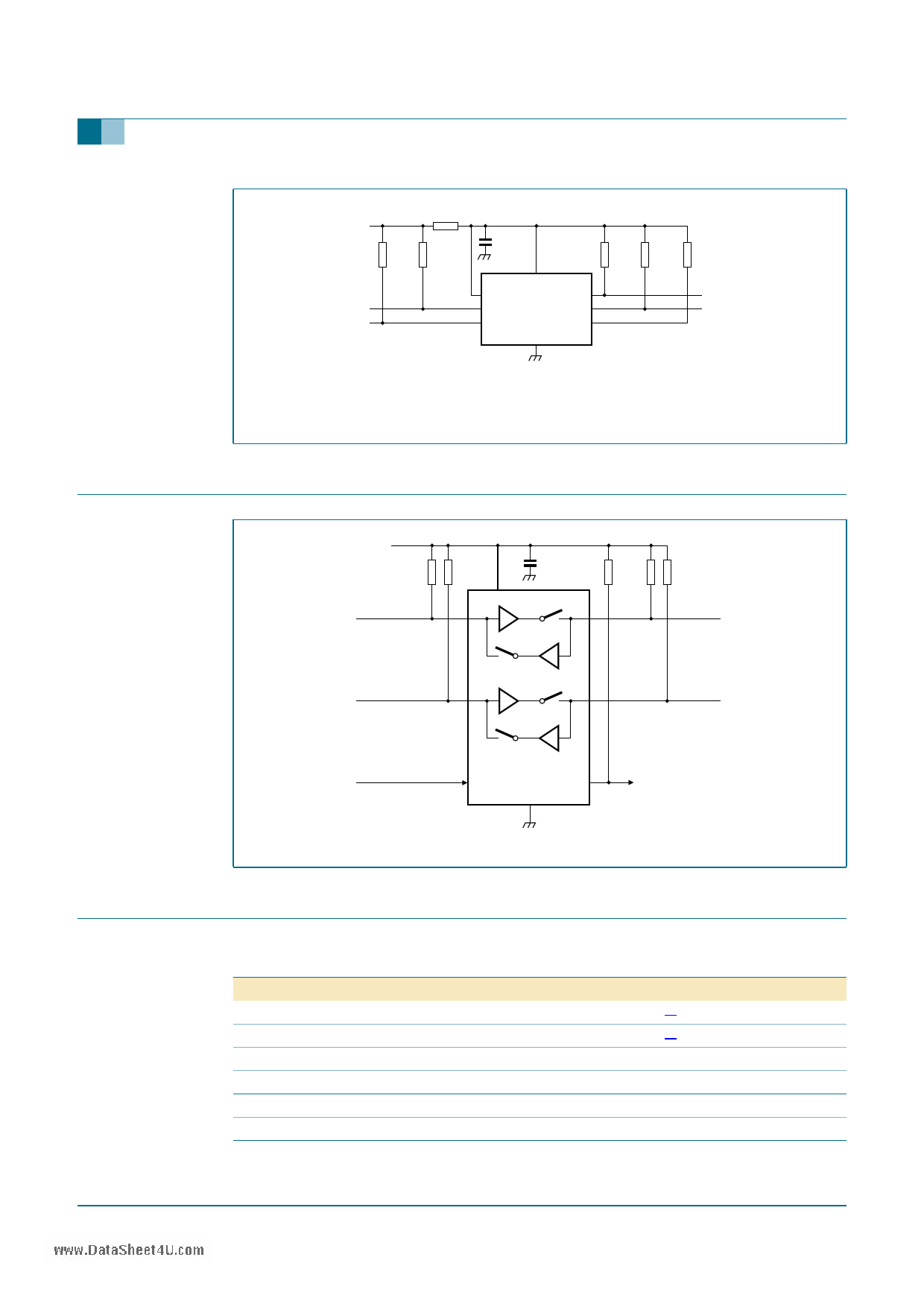

VCC

Rdrop

R1 R4

10 kΩ 10 kΩ

SDA

SCL

VCC_LOW

C2

0.01 µF

VCC

ENABLE SDAOUT

SDAIN

SCLOUT

SCLIN

READY

GND

R2 R3

R5

10 kΩ 10 kΩ 10 kΩ

SDA2

SCL2

002aab587

VCC > VCC_LOW

Rdrop is the line loss of VCC in the backplane.

Fig 10. System with disparate VCC voltages

9. Application design-in information

VCC

(2.7 V to 5.5 V)

R1

10 kΩ

SCLIN

R2

10 kΩ

8

3

C1

0.01 µF R5

10 kΩ

R3

10 kΩ

2

R4

10 kΩ

SCLOUT

SDAIN

6

7 SDAOUT

ENABLE

Fig 11. Typical application

1 ENABLE

READY 5

GND

4

002aab780

10. Limiting values

Table 4: Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter

Conditions

Min

VCC

Vn

Toper

Tstg

supply voltage

voltage on any other pin

operating temperature

storage temperature

[1] −0.5

[1] −0.5

−40

−65

Tsp solder point temperature

10 s maximum

-

Tj(max) maximum junction temperature

-

[1] Voltages with respect to pin GND.

Max

+7

+7

+85

+150

300

125

Unit

V

V

°C

°C

°C

°C

PCA9510A_1

Product data sheet

Rev. 01 — 8 September 2005

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

11 of 23

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet PCA9510A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PCA9510 | Hot swappable I2C and SMBus bus buffer | NXP Semiconductors |

| PCA9510A | Hot swappable I2C-bus and SMBus bus buffer | NXP Semiconductors |

| PCA9510D | Hot swappable I2C and SMBus bus buffer | NXP Semiconductors |

| PCA9510DP | Hot swappable I2C and SMBus bus buffer | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |