|

|

PDF TV00570003CDGB Data sheet ( Hoja de datos )

| Número de pieza | TV00570003CDGB | |

| Descripción | (TV00570002CDGB / TV00570003CDGB) Pseudo SRAM and NOR Flash Memory Mixed Multi-Chip Package | |

| Fabricantes | Toshiba | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TV00570003CDGB (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

TV00570002/003CDGB

TOSHIBA MULTI-CHIP INTEGRATED CIRCUIT SILICON GATE CMOS

TENTATIVE

Pseudo SRAM and NOR Flash Memory Mixed Multi-Chip Package

DESCRIPTION

The TV00570002/003CDGB is a mixed multi-chip package containing a 33,554,432-bit pseudo static RAM and a

134,217,728-bit Nor Flash Memory. The TV00570002/003CDGB is available in a 81-pin BGA package making it

suitable for a variety of applications.

MCP Features

• Power supply voltage of 2.7 to 3.3 V

• Operating temperature of −30° to 85°C

• Package

P-TFBGA81-0710-0.80BZ (Weight: 0.15 g)

Pseudo SRAM Features

• Organization : 2M × 16 bits

www.Da• taSPhoeweet4rUd.cisosmipation

Operating :

40 mA maximum

Standby :

150 μA maximum

Deep power-down standby : 5 μA maximum

• Access time :

Random / Page : 70 ns / 30 ns @CL=30pF

• Page read operation by 8 words

• Deep power-down mode : Memory cell data invalid

Nor Flash Memory Features

• Organization: 8M × 16 bits

• Power dissipation

Read operating :

55 mA maximum

Address Increment Read operation:

Page Read operating :

24mA maximum

5 mA maximum

Program / Erase operating: 15 mA maximum

Standby :

• Access time :

Random :

10 μA maximum

70 ns @CL=30pF

Page :

25 ns @CL=30pF

• Functions

Simultaneous Read/Write

Page read

Auto-Program , Auto Page Program

Auto Block Erase , Auto Chip Erase

Program Suspend / Resume

Erase Suspend/Resume

Data polling / Toggle bit

Password block protection

Block Protection/Boot Block Protection

Automatic Sleep, supports for hidden ROM Area

Common Flash Memory Interface (CFI)

• Block erase architecture

8 × 8 Kbytes / 127 × 64 Kbytes

• Bank architecture

16 Mbits × 8 Banks

• Boot block architecture

TV00570002CDGB : top boot block

TV00570003CDGB : bottom boot block

• Mode control

Compatible with JEDEC standard commands

• Erase/Program cycles

100,000 cycles typ.

2008-05-08 1/9

1 page

MODE SELECTION

Pseudo SRAM

MODE

Read(Word)

Read(Lower Byte)

Read(Upper Byte)

Write(Word)

Write(Lower Byte)

Write(Upper Byte)

Outputs Disabled

Standby

Deep Power-down Standby

CE1ps CE2ps

LH

HH

HL

OE

L

X

H

X

X

WE

H

L

H

X

X

LB

L

L

H

L

L

H

X

X

X

TV00570002/003CDGB

UB Add DQ0~DQ7 DQ8~DQ15

L DOUT

H DOUT

L High-Z

L

HX

DIN

DIN

L Invalid

X High-Z

X High-Z

X High-Z

DOUT

High-Z

DOUT

DIN

Invalid

DIN

High-Z

High-Z

High-Z

Nor Flash Memory

www.DataSheet4U.com

MODE

Read / Page Read

Standby

Output Disable

Write

Hardware Reset / Standby

Boot Block Protect

CEf

L

H

X

L

X

X

OE WE RESET

LH

H

XX

H

HH

X

H (1) H

XX

L

XX

X

WP

X

X

X

X

X

L

DQ0~DQ15

DOUT

High-Z

High-Z

DIN

High-Z

X

Notes: L = VIL; H = VIH; X = VIH or VIL

Does not apply when CEf = VIL and CE1ps

(1) Pulse input

= VIL and CE2ps = VIH at the same time.

2008-05-08 5/9

5 Page

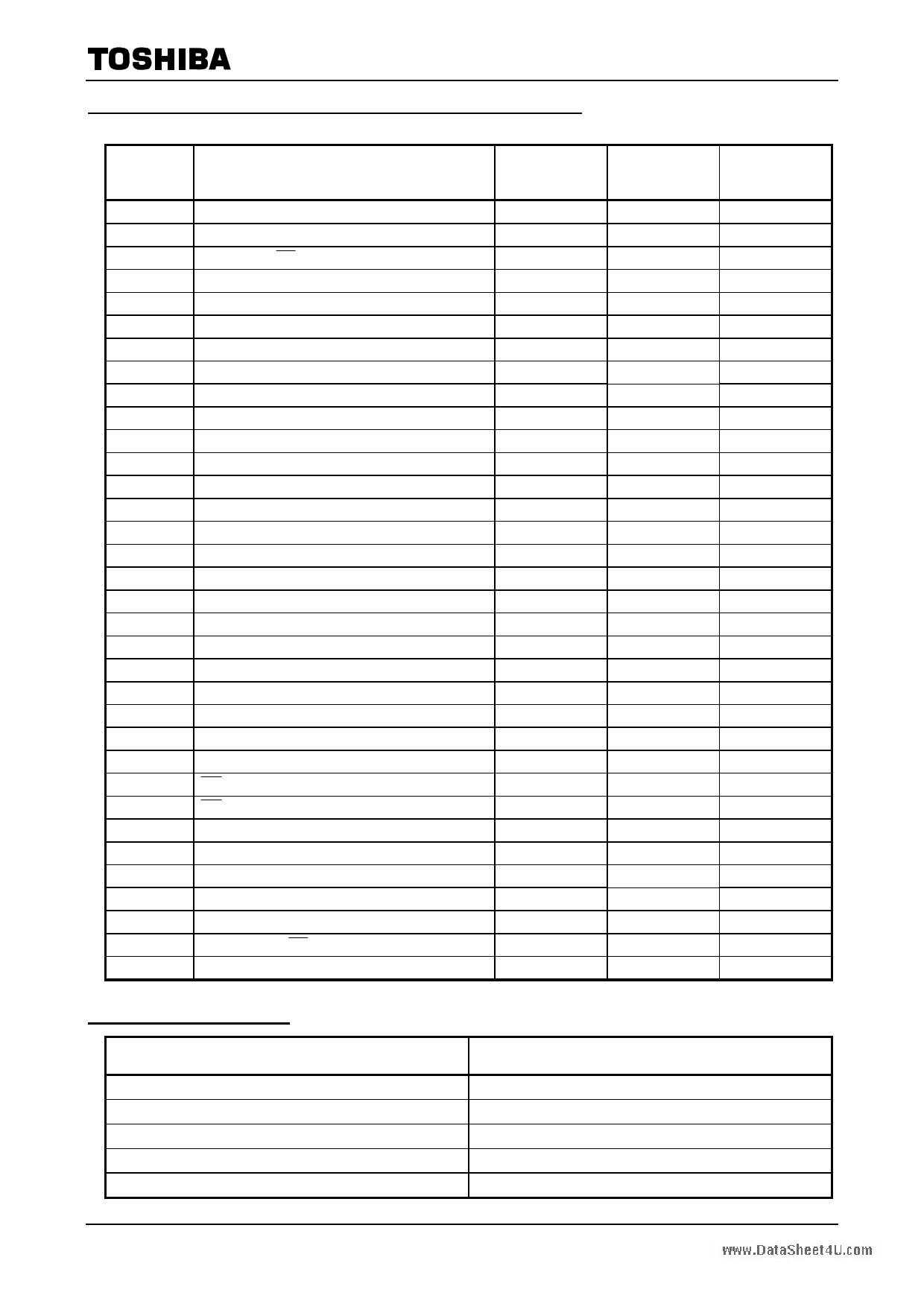

AC CHARACTERISTICS AND OPERATING CONDITIONS

(Ta = −30°C to 85°C, VDD = 2.7 to 3.3 V) (See Note 1 to 7)

TC51WHM516B

SYMBOL

PARAMETER

tRC Read Cycle Time

tACC

Address Access Time

tCO Chip Enable ( CE1 ) Access Time

tOE Output Enable Access Time

tBA Data Byte Control Access Time

tCOE

Chip Enable Low to Output Active

tOEE

Output Enable Low to Output Active

tBE Data Byte Control Low to Output Active

tOD Chip Enable High to Output High-Z

tODO

Output Enable High to Output High-Z

www.DataStBhDeet4U.com Data Byte Control High to Output High-Z

tOH Output Data Hold Time

tPM Page Mode Time

tPC Page Mode Cycle Time

tAA Page Mode Address Access Time

tAOH

Page Mode Output Data Hold Time

tWC Write Cycle Time

tWP Write Pulse Width

tCW Chip Enable to End of Write

tBW Data Byte Control to End of Write

tAW Address Valid to End of Write

tAS Address Set-up Time

tWR Write Recovery Time

tCEH

Chip Enable High Pulse Width

tWEH

Write Enable High Pulse Width

tODW

WE Low to Output High-Z

tOEW

WE High to Output Active

tDS Data Set-up Time

tDH Data Hold Time

tCS CE2 Set-up Time

tCH CE2 Hold Time

tDPD

CE2 Pulse Width

tCHC

CE2 Hold from CE1

tCHP

CE2 Hold from Power On

AC TEST CONDITIONS

PARAMETER

Output load

Input pulse level

Timing measurements

Reference level

tR, tF

MIN

MAX

UNIT

70 10000 ns

⎯ 70 ns

⎯ 70 ns

⎯ 25 ns

⎯ 25 ns

10 ⎯ ns

0 ⎯ ns

0 ⎯ ns

⎯ 20 ns

⎯ 20 ns

⎯ 20 ns

5 ⎯ ns

70 10000 ns

30 ⎯ ns

⎯ 30 ns

5 ⎯ ns

70 10000 ns

50 ⎯ ns

70 ⎯ ns

60 ⎯ ns

60 ⎯ ns

0 ⎯ ns

0 ⎯ ns

10 ⎯ ns

6 ⎯ ns

⎯ 20 ns

0 ⎯ ns

30 ⎯ ns

0 ⎯ ns

0 ⎯ ns

300 ⎯

μs

10 ⎯ ms

0 ⎯ ns

30 ⎯ μs

CONDITION

30 pF + 1 TTL Gate

VDD − 0.2 V, 0.2 V

VDD × 0.5

VDD× 0.5

5 ns

2007-03-12 P-2/6

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet TV00570003CDGB.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TV00570003CDGB | (TV00570002CDGB / TV00570003CDGB) Pseudo SRAM and NOR Flash Memory Mixed Multi-Chip Package | Toshiba |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |