|

|

PDF MPC8535E Data sheet ( Hoja de datos )

| Número de pieza | MPC8535E | |

| Descripción | PowerQUICC III Integrated Processor Hardware Specifications | |

| Fabricantes | Freescale Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de MPC8535E (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Freescale Semiconductor

Data Sheet: Product Preview

Document Number: MPC8535EEC

Rev. 2, 09/2009

MPC8535E

PowerQUICC™ III

Integrated Processor

Hardware Specifications

FC-PBGA–783

29 mm × 29 mm

• High-performance, 32-bit e500 core, scaling up to

1.25 GHz, that implements the Power Architecture™

www.DattaeSchheneotl4oUg.ycom

– 36-bit physical addressing

– Double-precision embedded floating point APU using

64-bit operands

– Embedded vector and scalar single-precision

floating-point APUs using 32- or 64-bit operands

– Memory management unit (MMU)

• Integrated L1/L2 cache

– L1 cache—32-Kbyte data and 32-Kbyte instruction

– L2 cache—512-Kbyte (8-way set associative)

• DDR2/DDR3 SDRAM memory controller with full ECC

support

– One 64-bit/32-bit data bus

– Up to 250-MHz clock (500-MHz data rate)

– Supporting up to 16 Gbytes of main memory

– Using ECC, detects and corrects all single-bit errors and

detects all double-bit errors and all errors within a nibble

– Invoke a level of system power management by

asserting MCKE SDRAM signal on-the-fly to put the

memory into a low-power sleep mode

– Both hardware and software options to support

battery-backed main memory

• Integrated security engine (SEC) optimized to process all

the algorithms associated with IPsec, IKE, SSL/TLS,

iSCSI, SRTP, IEEE Std 802.16e™, and 3GPP.

– XOR engine for parity checking in RAID storage

applications

• Enhanced Serial peripheral interfaces (eSPI)

– Support boot capability from eSPI

• Two enhanced three-speed Ethernet controllers (eTSECs)

with SGMII support

– Three-speed support (10/100/1000 Mbps)

– Two IEEE Std 802.3™, IEEE 802.3u, IEEE 802.3x,

IEEE 802.3z, IEEE 802.3ac, IEEE 802.3ab, and

IEEE Std 1588™-compatible controllers

– Support for various Ethernet physical interfaces: GMII,

TBI, RTBI, RGMII, MII, RGMII, RMII, and SGMII

– Support TCP/IP acceleration and QOS features

– MAC address recognition and RMON statistics support

– Support ARP parsing and generating wake-up events

based on the parsing results while in deep sleep mode

– Support accepting and storing packets while in deep

sleep mode

• High-speed interfaces (multiplexed) supporting:

– Two PCI Express interfaces

– PCI Express 1.0a compatible

– One x4/x2/x1 PCI Express interface

– Two x2/x1 ports

– One SGMII interface

– One Serial ATA (SATA) Controller supports SATA I and

SATA II data rates

• PCI 2.2 compatible PCI controller

• Two universal serial bus (USB) dual-role controllers

comply with USB specification revision 2.0

• 133-MHz, 32-bit, enhanced local bus (eLBC) with memory

controller

• Enhanced secured digital host controller (eSDHC) used for

SD/MMC card interface

– Support boot capability from eSDHC

• Integrated four-channel DMA controller

• Dual I2C and dual universal asynchronous

receiver/transmitter (DUART) support

• Programmable interrupt controller (PIC)

• Power management, low standby power

– Support Doze, Nap, Sleep, Jog, and Deep Sleep mode

– PMC wake on: LAN activity, USB connection or remote

wakeup, GPIO, internal timer, or external interrupt event

• System performance monitor

• IEEE Std 1149.1™-compatible, JTAG boundary scan

• 783-pin FC-PBGA package, 29 mm × 29 mm

This document contains information on a product under development. Freescale reserves the

right to change or discontinue this product without notice.

© Freescale Semiconductor, Inc., 2009. All rights reserved.

1 page

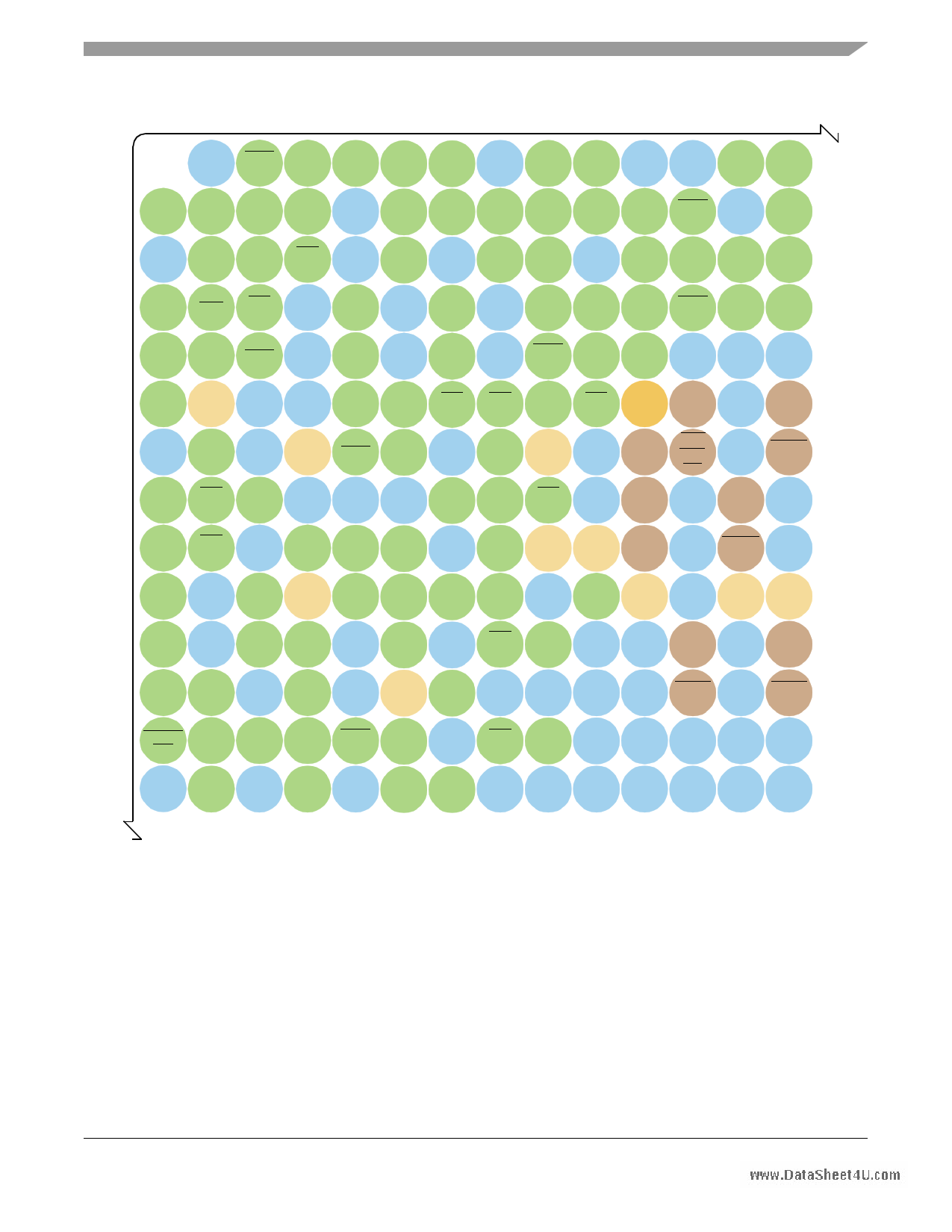

Pin Map

A BCDE FGH J K LMNP

1

GVDD

MDQS

[5]

MDQ

[32]

MDQ

[46]

MDQ

[47]

MDQ

[34]

GND

MDQ

[56]

MDQ

[57]

GND

GVDD

MDQS

[7]

MDQ

[58]

2

MDQ

[44]

MDQ

[40]

MDM

[5]

MDQS

[5]

GVDD

MDQ

[42]

MDQ

[43]

MDQ

[35]

MDQ

[60]

MDQ

[61]

MDM

[7]

MDQS

[7]

GND

MDM

[62]

3

GND

MDQ

[45]

MDQ

[41]

MCS

[0]

GND

MDQ

[33]

GVDD

MDQ

[38]

MDQ

[52]

GVDD

MDM

[6]

MDQS

[6]

MDQ

[50]

MDQ

[51]

4

MBA

[0]

MWE

MCS

[2]

GVDD

MDQ

[36]

GND

MDM

[4]

GND

MDQ

[39]

MDQ

[53]

MDQ MDQS MDQ

[49] [6] [54]

MDQ

[55]

5

MA

[10]

MBA

[1]

www.DataSh6eetM4UAOP.UcATRo_m NC

7 GND

MA

[0]

8

MCK

[3]

MCK

[3]

MRAS

GND

MODT

[0]

GVDD

MDQ

[37]

GVDD

MDQS

[4]

MDQS

[4]

MDQ

[48]

GND GVDD GND

GND

GVDD

MODT

[2]

MODT

[3]

MCS

[3]

MCS

[1]

MCK

[2]

GVDD

NC

MCAS

MA

[13]

GVDD

MODT

[1]

NC

MA

[2]

GND GVDD GND

MA

[1]

MCK

[5]

MCK

[5]

MCK

[2]

SD2_

IMP_CAL

SD2_

REF_

_TX CLK

S2GND SD2_RX

[0]

GND

SD2_

PLL_

TPD

SD2_

REF_

CLK

S2VDD

SD2_RX

[0]

GND

Rsvd S2GND SD2_RX S2GND

[1]

9

MCK

[0]

MCK

[0]

GVDD

MA

[4]

MA

[8]

MA

[7]

GVDD

MCKE

[3]

NC

NC

Rsvd

S2VDD

SD2_RX

[1]

S2GND

10

MA

[3]

GND

MA

[5]

NC

MA

[14]

MA

[15]

MCKE

[2]

MCKE

[0]

GVDD

MCKE

[1]

NC X2GND NC

NC

11

MA

[6]

GVDD

MECC

[3]

MA

[12]

GVDD

MECC

[2]

GVDD

MCK

[1]

MCK

[1]

GND

X2VDD

SD2_TX

[1]

X2GND

SD2_TX

[0]

12

MA

[11]

MA

[9]

GND

MECC

[7]

GND

NC

MECC

[0]

GVDD

GND

GVDD

X2GND

SD2_TX

[1]

X2VDD

SD2_TX

[0]

13

MAPAR_

ERR

MBA

[2]

MECC MDQS MDQS

[6] [8] [8]

MDM

[8]

GND

MCK

[4]

MCK

[4]

VDD_

CORE

GND

VDD_

CORE

GND

VDD_

CORE

14

GND

MDQ

[27]

GVDD

MECC

[1]

GVDD

MECC

[5]

MECC

[4]

GVDD

GND

GVDD

VDD_

CORE

GND

VDD_

CORE

GND

DETAIL A

Figure 3. MPC8535E Pin Map Detail A

MPC8535E PowerQUICC™ III Integrated Processor Hardware Specifications, Rev. 2

Freescale Semiconductor

5

5 Page

Signal

LAD[0:31]

LDP[0:3]

LA[27]

LA[28:31]

www.DaLtCaSSh[0e:e4t]4U.com

LCS5/DMA_DREQ2

LCS6/DMA_DACK2

LCS7/DMA_DDONE2

LWE0/LBS0/LFWE

LWE[1:3]/LBS[1:3]

LBCTL

LALE

LGPL0/LFCLE

LGPL1/LFALE

LGPL2/LOE/LFRE

LGPL3/LFWP

LGPL4/LGTA/LUPWAIT

/LPBSE/LFRB

LGPL5

LCLK[0:2]

LSYNC_IN

LSYNC_OUT

DMA_DACK[0:1]

/GPIO[10:11]

Table 1. MPC8535E Pinout Listing

Signal Name

Package Pin Number Pin Type

Muxed data / address

Data parity

Burst address

K22,L21,L22,K23,K24,

L24,L25,K25,L28,L27,

K28,K27,J28,H28,H27,

G27,G26,F28,F26,F25,

E28,E27,E26,F24,E24,

C26,G24,E23,G23,F22,

G22,G21

K26,G28,B27,E25

L19

Port address

K16,K17,H17,G17

Chip selects

K18,G19,H19,H20,G16

Chips selects / DMA Request H16

Chips selects / DMA Ack

J16

Chips selects / DMA Done

Write enable / Byte select

Write enable / Byte select

L18

J22

H22,H23,H21

Buffer control

J25

Address latch enable

J26

UPM general purpose line 0 / J20

FLash command latch enable

UPM general purpose line 1 / K20

Flash address latch enable

UPM general purpose line 2 / G20

Output enable/Flash read

enable

UPM general purpose line 3 / H18

Flash write protect

UPM general purpose line 4 / L20

Target Ack/Wait/SDRAM

parity byte select/Flash

Ready-busy

UPM general purpose line 5 / K19

Amux

Local bus clock

H24,J24,H25

Synchronization

D27

Local bus DLL

D28

DMA

DMA Acknowledge

AD6,AE10

I/O

I/O

O

O

O

I/O

O

O

O

O

O

O

O

O

O

O

I/O

O

O

I

O

O

Power

Supply

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

BVDD

OVDD

Pin Map

Notes

5,9,29

29

5,9,29

5,7,9,29

29

1,29

1,29

1,29

5,9,29

5,9,29

5,8,9,29

5,8,9,29

5,9,29

5,9,29

5,8,9,29

5,9,29

29

5,9,29

29

29

29

—

MPC8535E PowerQUICC™ III Integrated Processor Hardware Specifications, Rev. 2

Freescale Semiconductor

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet MPC8535E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MPC8535E | PowerQUICC III Integrated Processor Hardware Specifications | Freescale Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |