|

|

PDF CS42L51 Data sheet ( Hoja de datos )

| Número de pieza | CS42L51 | |

| Descripción | Stereo CODEC | |

| Fabricantes | Cirrus Logic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CS42L51 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CS42L51

Low-Power, Stereo Codec with Headphone Amp

DIGITAL-TO-ANALOG FEATURES

98-dB dynamic range (A-weighted)

-86-dB THD+N

Headphone amplifier - GND centered

– On-chip charge pump provides –VA_HP

– No DC-blocking capacitor required

– 46-mW power into stereo 16 @ 1.8 V

– 88-mW power into stereo 16 @ 2.5 V

– -75 dB THD+N

Digital signal processing engine

– Bass & treble tone control, de-emphasis

– PCM + ADC mix with independent volume

control

– Master digital volume control

– Soft ramp & zero-cross transitions

Beep generator

– Tone selections across two octaves

– Separate volume control

– Programmable on & off time intervals

– Continuous, periodic or one-shot beep

selections

Programmable peak-detect and limiter

Pop and click suppression

ANALOG-TO-DIGITAL FEATURES

98-dB dynamic range (A-weighted)

-88-dB THD+N

Analog gain controls

– +32-dB or +16-dB mic preamplifiers

– Analog programmable gain amplifier (PGA)

+20-dB digital boost

Programmable automatic level control (ALC)

– Noise gate for noise suppression

– Programmable threshold and

attack/release rates

Independent channel control

Digital volume control

High-pass filter disable for DC measurements

Stereo 3:1 analog input MUX

Dual mic inputs

– Programmable, low noise mic bias levels

– Differential mic mix for common mode

noise rejection

Very low 64 Fs oversampling clock reduces

power consumption

1.8 V to 3.3 V

1.8 V to 2.5 V

1.8 V to 2.5 V

1.8 V to 2.5 V

Serial Audio

Input

Hardware Mode

or I2C & SPI

Software Mode

Control Data

Reset

Serial Audio

Output

Beep

Generator

High Pass

Filters

Register

Configuration

Digital

Signal

Processing

Engine

MUX Switched

Capacitor DAC

Multibit

and Filter

Modulator

Switched

Capacitor DAC

MUX and Filter

ALC

Multibit

Oversampling MUX PGA

Volume

ADC

Controls

Multibit

Oversampling MUX PGA

ADC

ALC

Headphone

Amp ‐ GND

Centered

Headphone

Amp ‐ GND

Centered

Charge

Pump

MUX

+32 dB

+32 dB

MIC

Bias

Left HP Out

Right HP Out

Stereo Input 1

Stereo Input 2

Stereo Input 3 /

Mic Input 1 & 2

http://www.cirrus.com

Copyright Cirrus Logic, Inc. 2005–2015

(All Rights Reserved)

DS679F2

AUG ‘15

1 page

CS42L51

THERMAL CHARACTERISTICS .......................................................................................................... 82

13. REFERENCES .................................................................................................................................... 82

14. ORDERING INFORMATION ............................................................................................................. 83

15. REVISION HISTORY ......................................................................................................................... 83

LIST OF FIGURES

Figure 1.Typical Connection Diagram (Software Mode) ............................................................................. 9

Figure 2.Typical Connection Diagram (Hardware Mode) .......................................................................... 10

Figure 3.Headphone Output Test Load ..................................................................................................... 18

Figure 4.Serial Audio Interface Slave Mode Timing .................................................................................. 20

Figure 5.Serial Audio Interface Master Mode Timing ................................................................................ 20

Figure 6.Control Port Timing - I²C ............................................................................................................. 21

Figure 7.Control Port Timing - SPI Format ................................................................................................ 22

Figure 8.Analog Input Architecture ............................................................................................................ 27

Figure 9.MIC Input Mix with Common Mode Rejection ............................................................................. 29

Figure 10.Differential Input ........................................................................................................................ 29

Figure 11.ALC ........................................................................................................................................... 31

Figure 12.Noise Gate Attenuation ............................................................................................................. 32

Figure 13.Output Architecture ................................................................................................................... 33

Figure 14.De-Emphasis Curve .................................................................................................................. 34

Figure 15.Beep Configuration Options ...................................................................................................... 35

Figure 16.Peak Detect & Limiter ............................................................................................................... 36

Figure 17.Master Mode Timing ................................................................................................................. 38

Figure 18.Tri-State Serial Port .................................................................................................................. 39

Figure 19.I²S Format ................................................................................................................................. 39

Figure 20.Left-Justified Format ................................................................................................................. 40

Figure 21.Right-Justified Format (DAC only) ............................................................................................ 40

Figure 22.Initialization Flowchart ............................................................................................................... 42

Figure 23.Control Port Timing in SPI Mode .............................................................................................. 43

Figure 24.Control Port Timing, I²C Write ................................................................................................... 43

Figure 25.Control Port Timing, I²C Read ................................................................................................... 44

Figure 26.AIN & PGA Selection ................................................................................................................ 55

Figure 27.THD+N vs. Output Power per Channel at 1.8 V (16 load) .................................................... 73

Figure 28.THD+N vs. Output Power per Channel at 2.5 V (16 load) .................................................... 73

Figure 29.THD+N vs. Output Power per Channel at 1.8 V (32 load) .................................................... 74

Figure 30.THD+N vs. Output Power per Channel at 2.5 V (32 load) .................................................... 74

Figure 31.Power Dissipation vs. Output Power into Stereo 16

Figure 32.Power Dissipation vs. Output Power into Stereo 16 (Log Detail) .......................................... 75

Figure 33.ADC THD+N vs. Frequency with Capacitor Effects .................................................................. 76

Figure 34.ADC Passband Ripple .............................................................................................................. 80

Figure 35.ADC Stopband Rejection .......................................................................................................... 80

Figure 36.ADC Transition Band ................................................................................................................ 80

Figure 37.ADC Transition Band Detail ...................................................................................................... 80

Figure 38.DAC Passband Ripple .............................................................................................................. 80

Figure 39.DAC Stopband .......................................................................................................................... 80

Figure 40.DAC Transition Band ................................................................................................................ 80

Figure 41.DAC Transition Band (Detail) .................................................................................................... 80

LIST OF TABLES

Table 1. I/O Power Rails ............................................................................................................................. 8

Table 2. Hardware Mode Feature Summary ............................................................................................. 26

Table 3. MCLK/LRCK Ratios .................................................................................................................... 38

DS679F2

5

5 Page

CS42L51

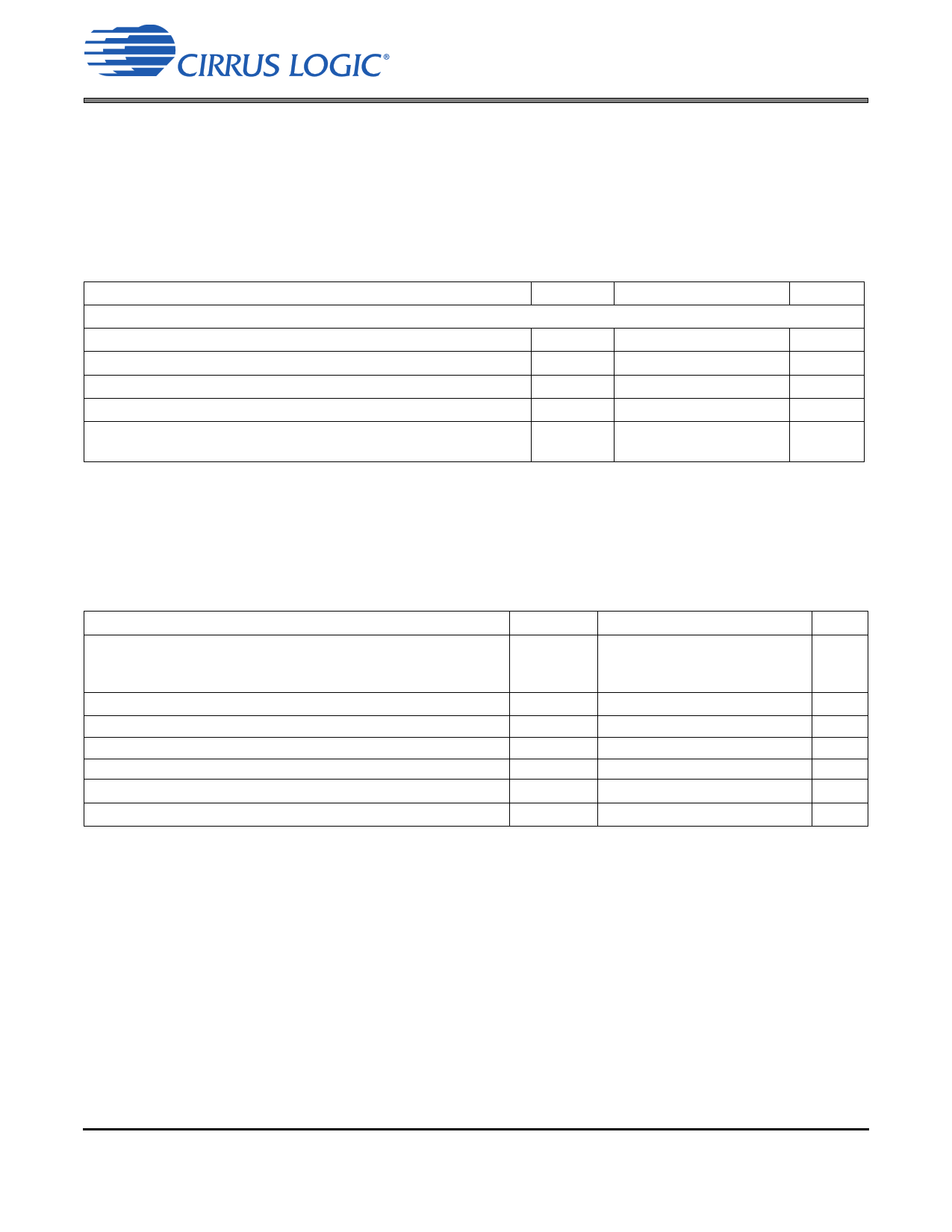

3. CHARACTERISTIC AND SPECIFICATION TABLES

(All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical per-

formance characteristics and specifications are derived from measurements taken at nominal supply voltages and

TA = 25° C.)

SPECIFIED OPERATING CONDITIONS

(AGND=DGND=0 V, all voltages with respect to ground.)

Parameters

DC Power Supply (Note 1)

Analog Core

Headphone Amplifier

Digital Core

Serial/Control Port Interface

Ambient Temperature

Commercial - CNZ

Automotive - DNZ

Symbol

VA

VA_HP

VD

VL

TA

Min

1.65

1.65

1.65

1.65

-10

-40

Max

2.63

2.63

2.63

3.47

+70

+85

Units

V

V

V

V

C

C

Note:

1. The device will operate properly over the full range of the analog, headphone amplifier, digital core and

serial/control port interface supplies.

ABSOLUTE MAXIMUM RATINGS

(AGND = DGND = 0 V; all voltages with respect to ground.)

Parameters

Symbol

Min

Max Units

DC Power Supply

Analog VA, VA_HP

Digital

VD

Serial/Control Port Interface

VL

Input Current

External Voltage Applied to Analog Input

External Voltage Applied to Analog Output

External Voltage Applied to Digital Input

Ambient Operating Temperature (power applied)

Storage Temperature

(Note 2)

(Note 3)

(Note 3)

Iin

VIN

VIN

VIND

TA

Tstg

-0.3

-0.3

-0.3

-

AGND-0.3

-VA_HP - 0.3

-0.3

-50

-65

3.0

3.0

4.0

±10

VA+0.3

+VA_HP + 0.3

VL+ 0.3

+115

+150

V

V

V

mA

V

V

V

°C

°C

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation

is not guaranteed at these extremes.

Notes:

2.

3.

Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause

SCR latch-up.

The maximum over/under voltage is limited by the input current.

DS679F2

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CS42L51.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CS42L50 | Low Voltage/ Stereo CODEC with headphone Amp | Cirrus Logic |

| CS42L50-KN | Low Voltage/ Stereo CODEC with headphone Amp | Cirrus Logic |

| CS42L51 | Stereo CODEC | Cirrus Logic |

| CS42L51 | Stereo CODEC | Cirrus Logic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |