|

|

PDF A2S56D30CTP Data sheet ( Hoja de datos )

| Número de pieza | A2S56D30CTP | |

| Descripción | (A2S56D20CTP - A2S56D40CTP) 256Mb DDR SDRAM | |

| Fabricantes | Powerchip Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de A2S56D30CTP (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

256Mb DDR SDRAM Specification

A2S56D20CTP

A2S56D30CTP

A2S56D40CTP

Powerchip Semiconductor Corp.

No.12, Li-Hsin Rd.1, Science-based Industrial Park, Hsin-Chu

Taiwan, R.O.C.

TEL: 886-3-5795000

FAX: 886-3-5792168

1 page

Powerchip Semiconductor Corp.

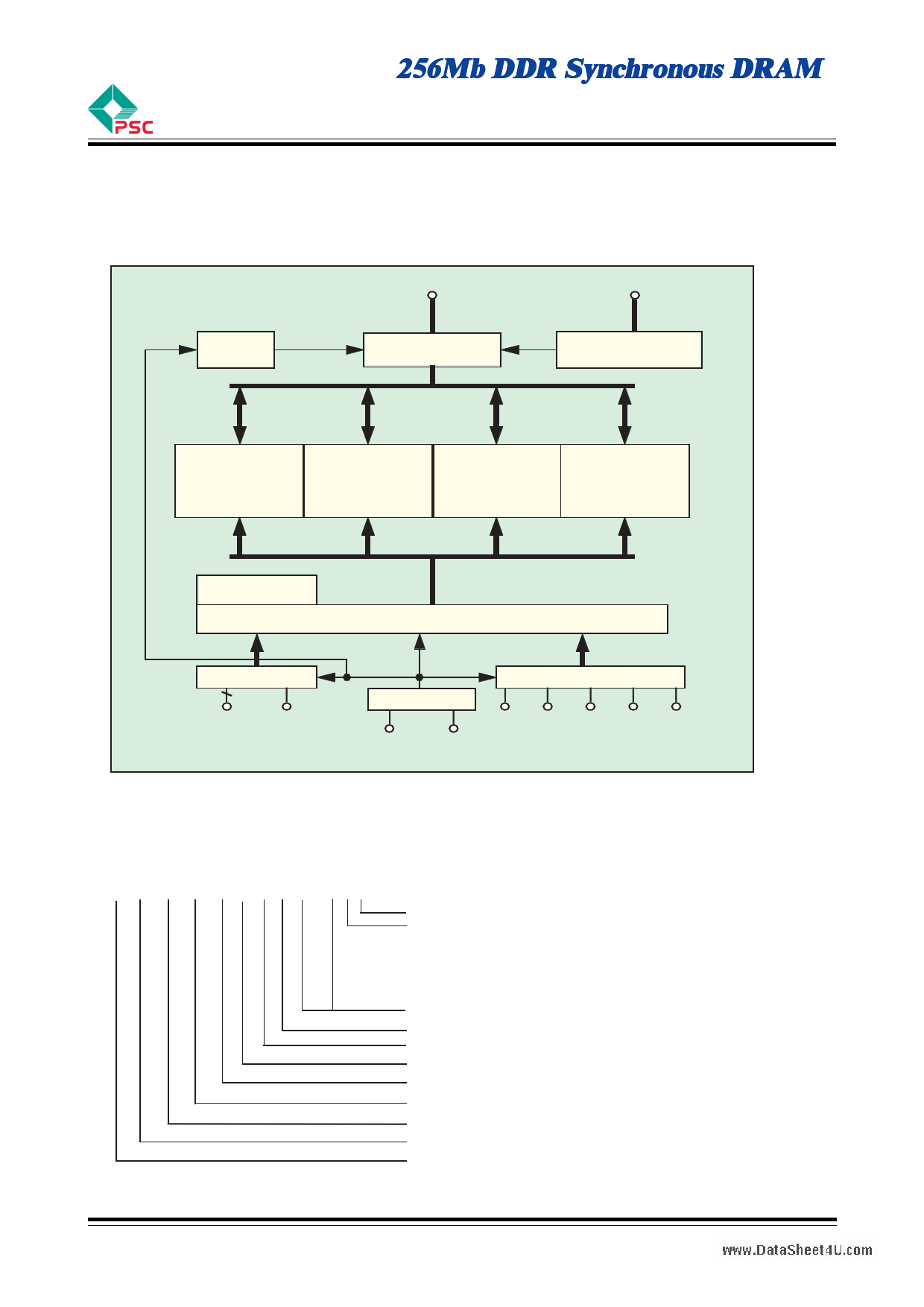

BLOCK DIAGRAM

DLL

256Mb DDR Synchronous DRAMwww.DataSheet4U.com

A2S56D20CTP (4-bank x 16,777,216 - word x 4-bit)

A2S56D30CTP (4-bank x 8,388,608 - word x 8-bit)

A2S56D40CTP (4-bank x 4,194,304 - word x 16-bit)

DQ0-7

I/O Buffer

DQS

QS Buffer

Memory

Array

Bank#0

Memory

Array

Bank#1

Memory

Array

Bank#2

Memory

Array

Bank#3

Mode Register

Control Circuitry

Address Buffer

A0-12 BA0,1

Clock Buffer

CLK, /CLK CKE

Control Signal Buffer

/CS /RAS /CAS /WE DM

Type Designation Code

A 2 S 56 D 3 0 C TP - G 5 L

Special Function

Access Item

L : Low Power , Blank : Standard

-5 : 200MHz@CL=2.5;3 and 133MHz @CL=2

-6 : 166MHz@CL=2.5 and 133MHz @CL=2

-75 : 133MHz@CL=2.5 and 100MHz @CL=2

Package Type

TP : TSOP(II) ; G : Pb - Free

Process Generation

Function

C : 4th generation

0 : Random Column

Organization

2 : x4, 3 : x8, 4: x16

DDR Synchronous DRAM

Density

56 : 256Mbit

Interface

V : LVTTL ; S : SSTL_3,_2

Memory Style (DRAM)

PSC DRAM

Jun.2004

Page- 3

Rev.1.0

5 Page

Powerchip Semiconductor Corp.

256Mb DDR Synchronous DRAMwww.DataSheet4U.com

A2S56D20CTP (4-bank x 16,777,216 - word x 4-bit)

A2S56D30CTP (4-bank x 8,388,608 - word x 8-bit)

A2S56D40CTP (4-bank x 4,194,304 - word x 16-bit)

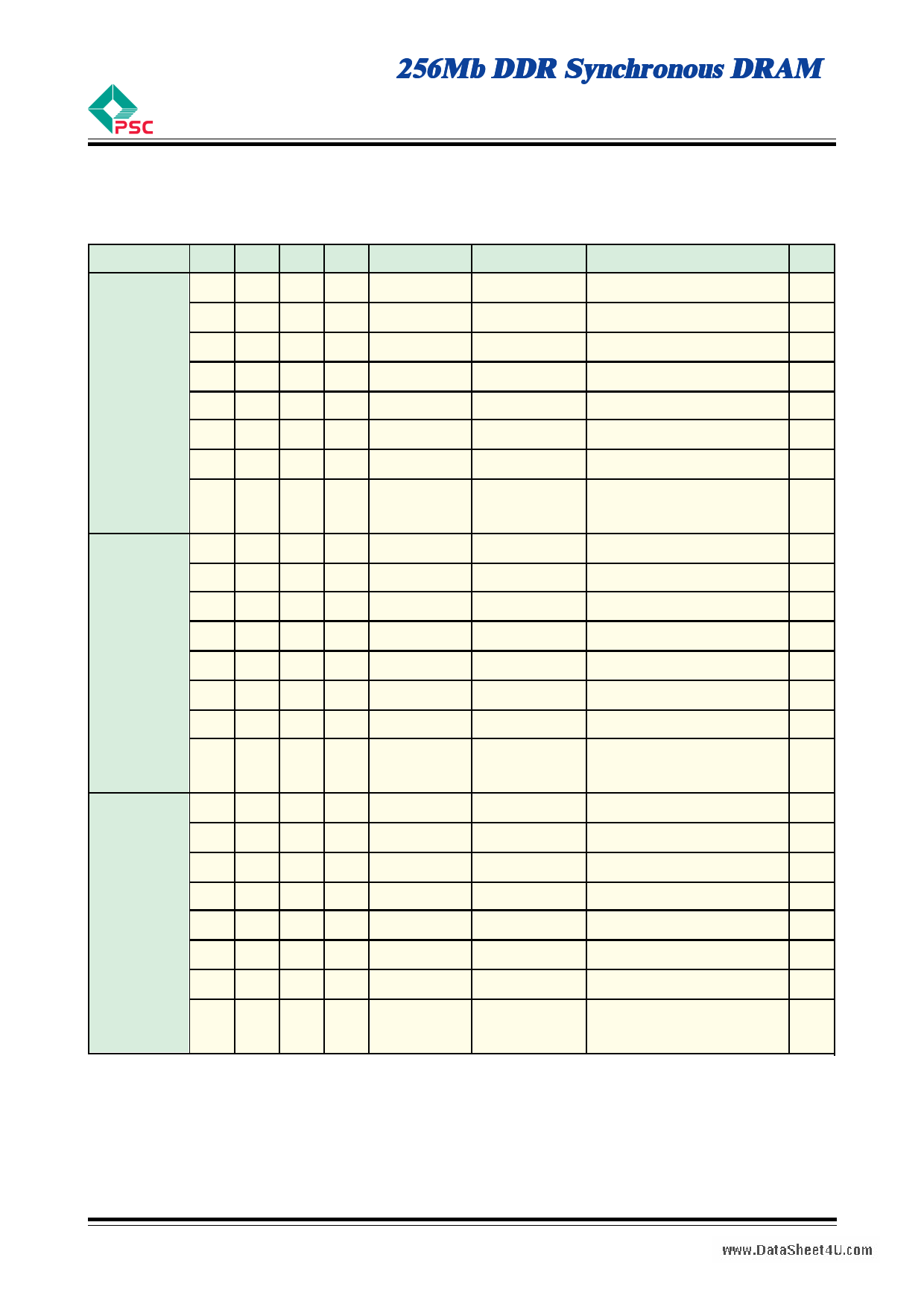

FUNCTION TRUTH TABLE (continued)

Current State /CS /RAS /CAS /WE Address

PRE -

H X X XX

CHARGING L H H H X

L H H L BA

L H L X BA, CA, A10

L L H H BA, RA

L L H L BA, A10

L L L HX

Op-Code,

LLLL

Mode-Add

ROW

H X X XX

ACTIVATING L H H H X

L H H L BA

L H L X BA, CA, A10

L L H H BA, RA

L L H L BA, A10

L L L HX

Op-Code,

LLLL

Mode-Add

WRITE RE- H X X X X

COVERING L H H H X

L H H L BA

L H L X BA, CA, A10

L L H H BA, RA

L L H L BA, A10

L L L HX

Op-Code,

LLLL

Mode-Add

Command

Action

DESEL NOP (Idle after tRP)

NOP NOP (Idle after tRP)

TERM ILLEGAL

READ / WRITE ILLEGAL

ACT ILLEGAL

PRE / PREA NOP (Idle after tRP)

REFA ILLEGAL

Notes

2

2

2

4

MRS

ILLEGAL

DESEL NOP (Row Active after tRCD)

NOP NOP (Row Active after tRCD)

TERM ILLEGAL

READ / WRITE ILLEGAL

ACT ILLEGAL

PRE / PREA ILLEGAL

REFA ILLEGAL

2

2

2

2

MRS

ILLEGAL

DESEL NOP

NOP NOP

TERM ILLEGAL

READ / WRITE ILLEGAL

ACT ILLEGAL

PRE / PREA ILLEGAL

REFA ILLEGAL

2

2

2

2

MRS

ILLEGAL

Jun.2004

Page- 9

Rev.1.0

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet A2S56D30CTP.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| A2S56D30CTP | (A2S56D20CTP - A2S56D40CTP) 256Mb DDR SDRAM | Powerchip Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |