|

|

PDF ADP4100 Data sheet ( Hoja de datos )

| Número de pieza | ADP4100 | |

| Descripción | Programmable Multi-Phase Synchronous Buck Converter | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ADP4100 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

ADP4100

www.DataSheet4U.com

Product Preview

Programmable Multi-Phase

Synchronous Buck

Converter

The ADP4100 is an integrated power control IC for VR11.1

applications. The ADP4100 can be programmed for 1−, 2−, 3−, 4−, 5−

or 6−phase operation, allowing for the construction of up to six

complementary buck switching stages. The ADP4100 supports PSI,

which is a power state indicator and can be used to reduce number of

operating phases at light loads.

The ADP4100 is optimized for converting a 12 V main supply into

the core supply voltage required by high performance Intel processors.

It uses an internal 8−bit DAC to read the voltage identification (VID)

code directly from the processor, which is used to set the output

voltage between 0.375 V and 1.6 V.

Features

• Supports Both VR11 and VR11.1 Specifications

• Digitally Programmable 0.375 V to 1.6 V Output

• Selectable 1−, 2−, 3−, 4−, 5− or 6−Phase Operation

• Fast−Enhanced PWM FlexModet

• TRDET to Improve Load Release

• Active Current Balancing Between All Output Phases

• Supports On−The−Fly (OTF) VID Code Changes

• Supports PSI − Power Saving Mode

• Short Circuit Protection with Latchoff Delay

• This is a Pb−Free Device

Typical Applications

• Servers

• Desktop PC’s

• POLs (Memory)

http://onsemi.com

LFCSP48

CASE 932AD

MARKING

DIAGRAM

ADP4100

JCPZ

#YYWW

XXXXX

CCCCC

xx = Device Code

# = Pb−Free Package

YYWW = Date Code

XXX = Assembly Lot

CCC = Country of Origin

PIN ASSIGNMENT

NC 1

NC 2

NC 3

NC 4

EN 5

GND 6

PSI_SET 7

LLSET 8

IMON 9

TTSENSE 10

VRHOT 11

IREF 12

PIN 1

INDICATOR

ADP4100

TOP VIEW

(Not to Scale)

36 PWM1

35 PWM2

34 PWM3

33 PWM4

32 PWM5

31 PWM6

30 SW1

29 SW2

28 SW3

27 SW4

26 SW5

25 SW6

This document contains information on a product under development. ON Semiconductor

reserves the right to change or discontinue this product without notice.

© Semiconductor Components Industries, LLC, 2008

March, 2008 − Rev. P0

1

ORDERING INFORMATION

Device*

Package

Shipping†

ADP4100JCPZ−REEL LFCSP48 2500/Tape & Reel

ADP4100JCPZ−RL7 LFCSP48 750/Tape & Reel

*The “Z’ suffix indicates Pb−Free package.

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specifications

Brochure, BRD8011/D.

Publication Order Number:

ADP4100/D

1 page

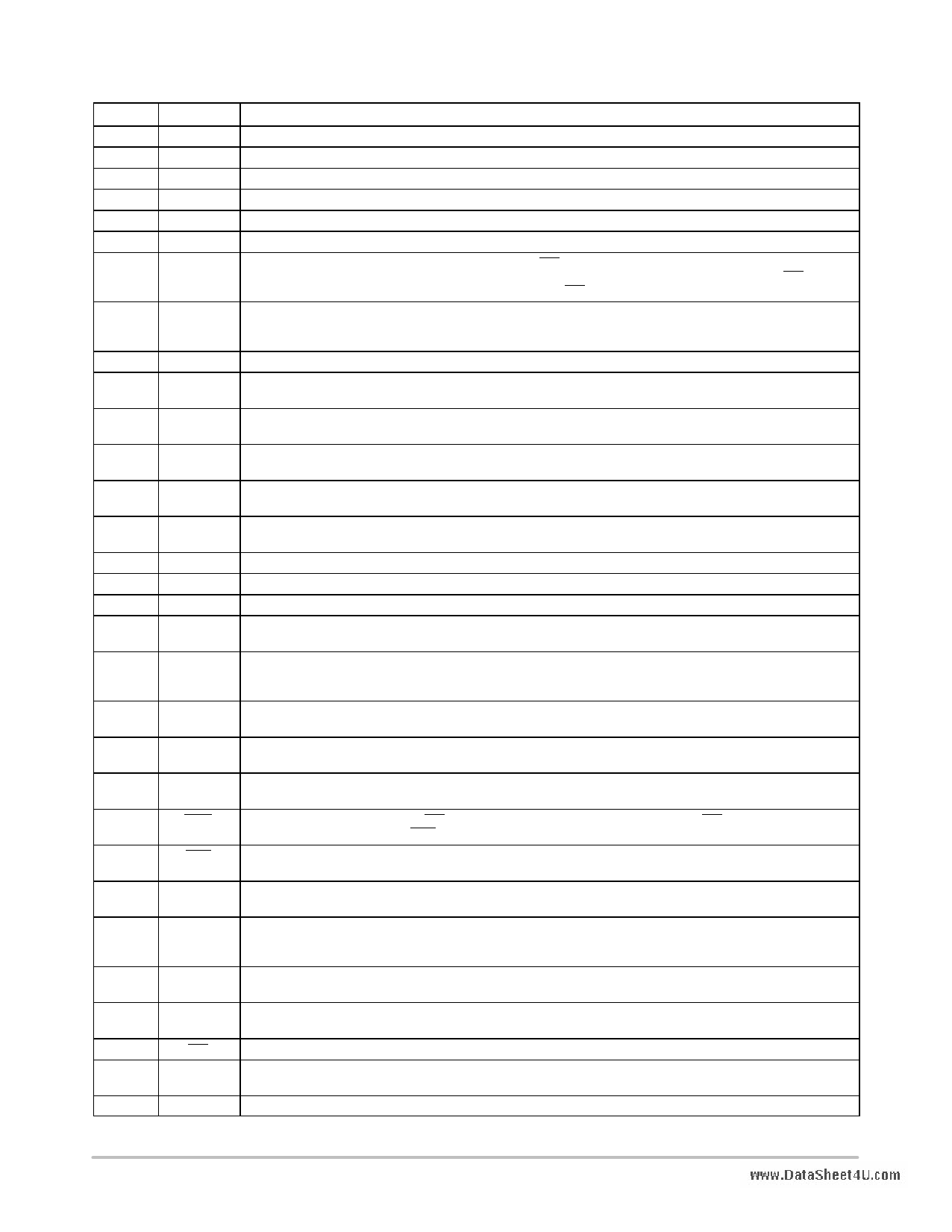

PIN ASSIGNMENT

Pin No. Pin Name

1 NC

2 NC

3 NC

4 NC

5 EN

6 GND

7 PSI_SET

8 LLSET

9 IMON

10 TTSENSE

11 VRHOT

12 IREF

13 RT

14 RAMPADJ

15 TRDET

16 FBRTN

17 COMP

18 FB

19 CSREF

20 CSSUM

21 CSCOMP

22 ILIMFS

23 ODN

24 OD1

25 to 30

31 to 36

SW6 to

SW1

PWM6 to

PWM1

37

38 to 45

46

47

VCC

VID7 to

VID0

PSI

PWRGD

48 VCC3

ADP4100

www.DataSheet4U.com

Description

No Connect

No Connect

No Connect

No Connect

Power Supply Enable Input. Pulling this pin to GND disables the PWM outputs and pulls the PWRGD output low.

Ground. All internal biasing and the logic output signals of the device are referenced to this ground.

This input sets the number of phases enabled during PSI. Pulling this input high means that two phases,

Phases 1 and Phase 4 (when 6 phases are enabled during normal operation), are enabled during PSI.

Grounding this pin means only Phase 1 is enabled during PSI.

Output Loadline Programming Input. This pin can be connected directly to CSCOMP or it can be connected to

the centerpoint of a resistor divider between CSCOMP and CSREF. Connecting LLSET to CSREF disables

the loadline.

Total Current Output Pin.

VR Temperature Sense Input. An NTC thermistor between this pin and GND is used to remotely sense the

temperature at the desired thermal monitoring point.

VR HOT Output. Open drain output that signals when the temperature at the monitoring point connected to

TTSENSE exceeds the VRHOT temperature threshold.

Current Reference Input. An external resistor from this pin to ground sets the reference current for IFB,

IILIMFS, and ITH(X).

Frequency Setting Resistor Input. An external resistor connected between this pin and GND sets the oscillator

frequency of the device.

PWM Ramp Current Input. An external resistor from the converter input voltage to this pin sets the internal

PWM ramp.

Transient Detect. This output is asserted low whenever a load release is detected

Feedback Return. VID DAC and error amplifier reference for remote sensing of the output voltage.

Error Amplifier Output and Compensation Point.

Feedback Input. Error amplifier input for remote sensing of the output voltage. An external resistor between

this pin and the output voltage sets the no load offset point.

Current Sense Reference Voltage Input. The voltage on this pin is used as the reference for the current sense

amplifier and the power−good and crowbar functions. This pin should be connected to the common point of

the output inductors.

Current Sense Summing Node. External resistors from each switch node to this pin sum the average inductor

currents together to measure the total output current.

Current Sense Compensation Point. A resistor and capacitor from this pin to CSSUM determines the gain of

the current sense amplifier and the positioning loop response time.

Current Sense and Limit Scaling Pin. An external resistor from this pin to CSCOMP sets the internal current

sensing signal for current−limit and IMON.

Output Disable Logic Output for PSI operation. This pin is actively pulled low when PSI is low, otherwise it

functions in the same way as OD1.

Output Disable Logic Output. This pin

UVLO threshold to signal to the Driver

iIsCatchtaivtetlhyepdurllievedrlohwighw−hseidnethaendENlowin−psuidt eisolouwtpuotrswshheonulVdCgCo

is below

low.

its

Current Balance Inputs. Inputs for measuring the current level in each phase. The SW pins of unused phases

should be left open.

Logic−Level PWM Outputs. Each output is connected to the input of an external MOSFET driver such as the

ADP3121. Connecting PWM6 to VCC disables PWM6, connecting PWM5 to VCC disables PWM5 and PWM6,

etc. This means the ADP4100 can be setup to operate as a 1− 2−, 3−, 4−, 5−, or 6−phase controller.

Supply Voltage for the Device. A 340 W resistor should be placed between the 12 V system supply and the

VCC pin. The internal shunt regulator maintains VCC = 5.0 V.

Voltage Identification DAC Inputs. These eight pins are pulled down to GND, providing a logic zero if left open.

When in normal operation mode, the DAC output programs the FB regulation voltage from 0.375 V to 1.6 V.

Power State Indicator. Pulling this pin low places the controller in lower power state operation.

Power−Good Output. Open−drain output that signals when the output voltage is outside of the proper

operating range.

3.3 V Power Supply Output. A capacitor from this pin to ground provided decoupling for the interval 3.3V LDO.

http://onsemi.com

5

5 Page

ADP4100

Theory of Operation

The ADP4100 is a 6−Phase VR11.1 regulator. A typical

application circuits is shown in Figure 2.

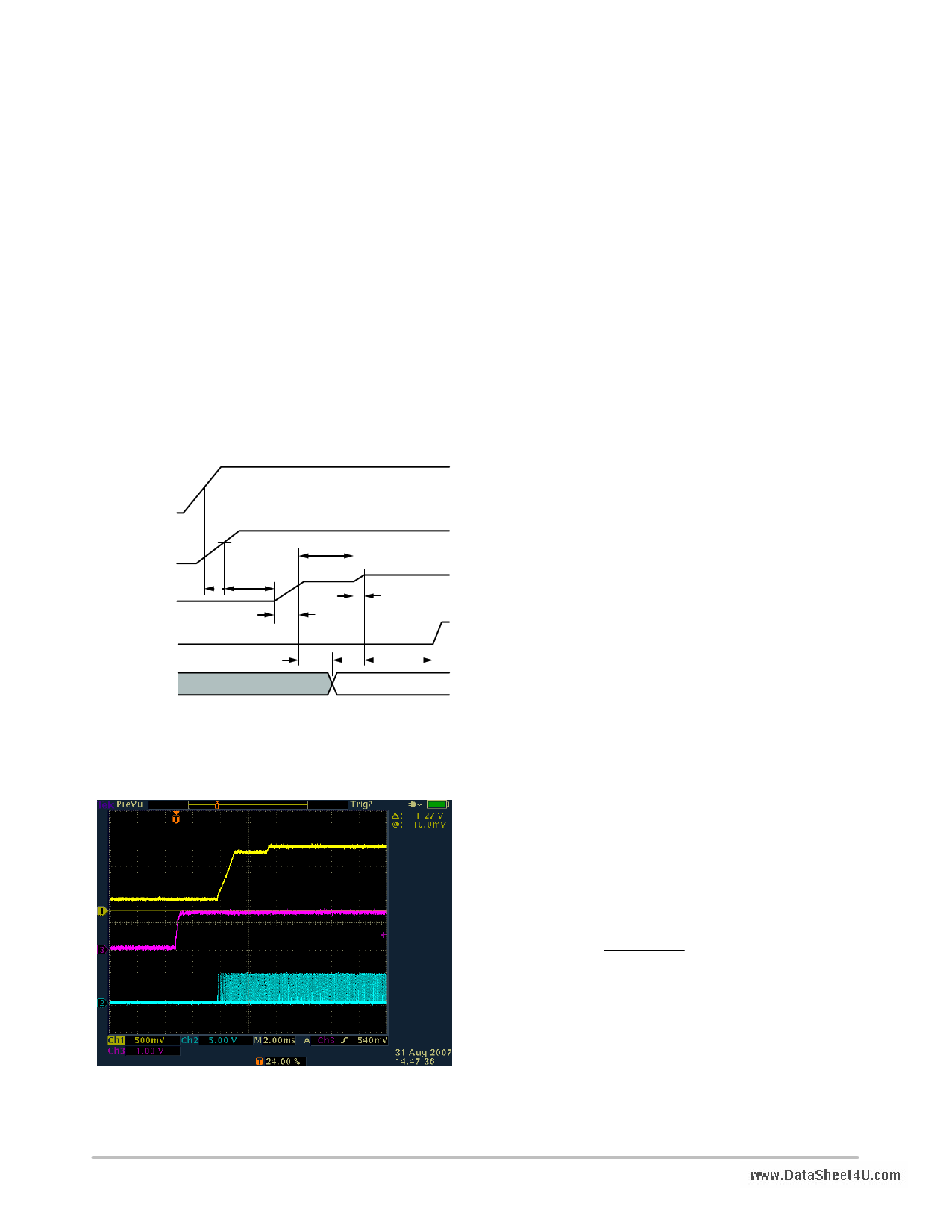

Startup Sequence

The ADP4100 follows the VR11 startup sequence shown

in Figure 7. After both the EN and UVLO conditions are

met, an internal timer goes through one delay cycle

TD1 (= 2ms). The first six clock cycles of TD2 are blanked

from the PWM outputs and used for phase detection as

explained in the following section. Then the internal

soft−start ramp is enabled (TD2) and the output comes up to

the boot voltage of 1.1V. The voltage is held at 1.1V for the

2 ms, also known as the Boot Hold time or TD3. During TD3

the processor VID pins settle to the required VID code.

When TD3 is over, the ADP4100 reads the VID inputs and

soft−starts either up or down to the final VID voltage (TD4).

After TD4 has been completed and the PWRGD masking

time (equal to VID on the fly masking) is finished, a third

cycle of the internal timer sets the PWRGD blanking (TD5).

5V

SUPPLY

UVLO

THRESHOLD

VTT I/O

(ADP4100 EN)

VCC_CORE

VR READY

(ADP4100 PWRGD)

CPU

VID INPUTS

0.85V

TD1

TD3

VBOOT

(1.1V)

TD2

VVID

TD4

VID INVALID

50ms

TD5

VID VALID

Figure 7. System Startup Sequence for VR11

Figure 8 shows typical startup waveforms for the

ADP4100.

Figure 8 typical startup waveforms:

Channel 1: CSREF

Channel 2: PWM1

Channel 3 : Enable

www.DataSheet4U.com

Phase Detection

During startup, the number of operational phases and their

phase relationship is determined by the internal circuitry that

monitors the PWM outputs. Normally, the ADP4100

operates as a 6−Phase PWM controller.

To operate as a 5−Phase Controller connect PWM6 to VCC.

To operate as a 4−Phase Controller connect PWM5 and

PWM6 to VCC.

To operate as a 3−Phase Controller connect PWM4, PWM5

and PWM6 to VCC.

To operate as a 2−Phase Controller connect PWM3, PWM4,

PWM5 and PWM6 to VCC.

To operate as a single phase controller connect PMW2,

PWM3, PWM4, PWM5 and PWM6 to VCC.

Prior to soft−start, while EN is high the PWM6, PWM5,

PWM4 PWM3 and PWM2 pins sink approximately 100 mA

each. An internal comparator checks each pin’s voltage vs.

a threshold of 3.0 V. If the pin is tied to VCC, it is above the

threshold. Otherwise, an internal current sink pulls the pin

to GND, which is below the threshold. PWM1 is low during

the phase detection interval that occurs during the first six

clock cycles of TD2. After this time, if the remaining PWM

outputs are not pulled to VCC, the 100 mA current sink is

removed, and they function as normal PWM outputs. If they

are pulled to VCC, the 100 mA current source is removed, and

the outputs are put into a high impedance state.

The PWM outputs are logic−level devices intended for

driving fast response external gate drivers such as the

ADP3121. Because each phase is monitored independently,

operation approaching 100% duty cycle is possible. In

addition, more than one output can be on at the same time to

allow overlapping phases.

Master Clock Frequency

The clock frequency of the ADP4100 is set with an

external resistor connected from the RT pin to ground. The

frequency follows the graph in Figure 3. To determine the

frequency per phase, the clock is divided by the number of

phases in use. If all phases are in use, divide by 6. If 4 phases

are in use then divide by 4.

RT + n

1

fsw

Cr * RTO

(eq. 1)

Where: CT = 2.2 pF and RTO = 21 K

Figure 8. Shows Typical Startup Waveforms for

the ADP4100

Output Voltage Differential Sensing

The ADP4100 combines differential sensing with a high

accuracy VID DAC and reference, and a low offset error

amplifier. This maintains a worst−case specification of

±7 mV differential sensing error over its full operating

output voltage and temperature range. The output voltage is

sensed between the FB pin and FBRTN pin. FB is connected

http://onsemi.com

11

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet ADP4100.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADP4100 | Programmable Multi-Phase Synchronous Buck Converter | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |