|

|

PDF PACVGA100 Data sheet ( Hoja de datos )

| Número de pieza | PACVGA100 | |

| Descripción | VGA Port ESD Protection and Termination Network | |

| Fabricantes | California Micro Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de PACVGA100 (archivo pdf) en la parte inferior de esta página. Total 5 Páginas | ||

|

No Preview Available !

PACVGA100/101

VGA Port ESD Protection and Termination Network

Features

• Seven channel ESD protection

• +15 kV ESD protection per channel, connector

side (HBM)

• +8 kV contact, 15 kV air discharge ESD protection

per channel, connector side (IEC 61000-4-2 Level

4 standard)

• Low loading capacitance—4.5pF typical

• 16-pin QSOP package

Applications

• ESD protection and termination resistors for VGA

(video) port interfaces

• Desktop PCs

• Notebook computers

• LCD monitors

Product Description

The PACVGA100/101 functions as a transmission line

termination and ESD protection device for video appli-

cations. It provides 75 ohm parallel terminations for

video R, G, and B lines and series terminations for the

Horizontal Sync, Vertical Sync and the two DDC lines

which serve as Plug and Play logic signals. In addition,

all interface lines provide Level 4 ESD protection per

the IEC 61000-4-2 contact discharge specification. The

PACVGA100 provides internal pull-up resistors (R3) for

the two DDC lines whereas the PACVGA101 omits

these internal pull-ups so that different pull-up resistor

values can be added externally.

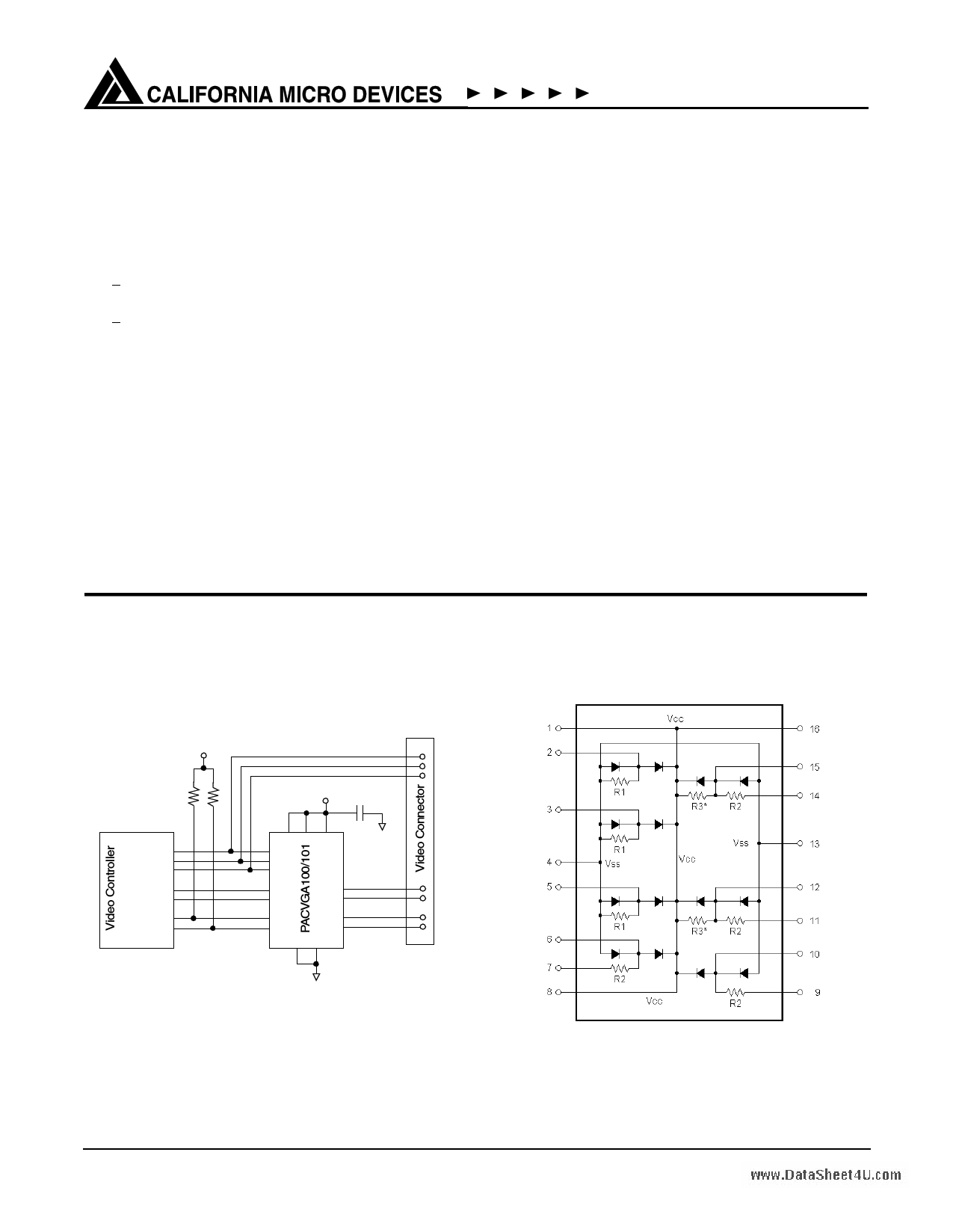

Typical Application Circuit

Simplified Electrical Schematic

VCC

R1, R2 required

only for VGA101 R1 R2

Red

Grn

Blue

H-Sync

V-Sync

DDC_Data

DDC_Clk

(See Note 1)

VCC CBYPASS

1 8 16 0.2uF

2

3

5

76

9 10

11 12

14 15

4 13

R

G

B

H-Sync

V-Sync

DDC_Data

DDC_Clk

www.DatNaSohteee1t:4FUor.cboemst ESD protection, minimize R/G/B trace lengths

between the PACVGA100/101 device and the video

connector.

R1 = 75Ω, R2 = 33Ω

R3 = 2.2KΩ (for PACVGA100 only)

* R3 omitted for PACVGA101

© 2002 California Micro Devices Corp. All rights reserved.

02/14/02 215 Topaz Street, Milpitas, California 95035 L Tel: (408) 263-3214 L Fax: (408) 263-7846 L www.calmicro.com

1

1 page

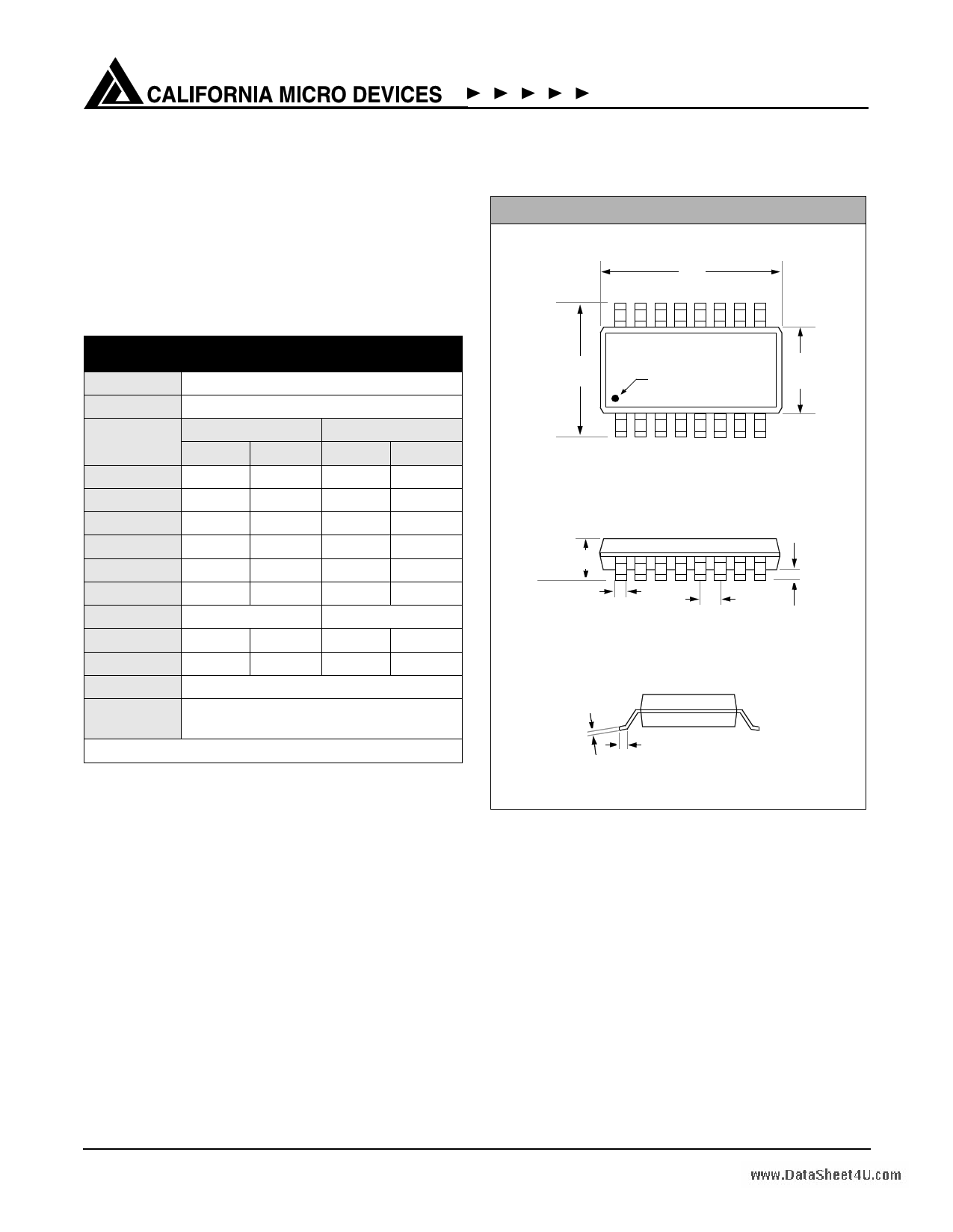

Mechanical Details

QSOP Mechanical Specifications

PACVGA100/101 devices are packaged in 16-pin

QSOP packages. Dimensions are presented below.

For complete information on the QSOP-16 package,

see the California Micro Devices QSOP Package Infor-

mation document.

PACKAGE DIMENSIONS

Package

QSOP (JEDEC name is SSOP)

Pins

16

Dimensions

Millimeters

Min Max

Inches

Min Max

A

1.35

1.75

0.053 0.069

A1

0.10

0.25

0.004 0.010

B

0.20

0.30

0.008 0.012

C

0.18

0.25

0.007 0.010

D

4.80

5.00

0.189 0.197

E

3.81

3.98

0.150 0.157

e

0.64 BSC

0.025 BSC

H

5.79

6.19

0.228 0.244

L

0.40

1.27

0.016 0.050

# per tube

100 pieces*

# per tape

and reel

2500 pieces

Controlling dimension: inches

* This is an approximate number which may vary.

PACVGA100/101

Mechanical Package Diagrams

TOP VIEW

D

16 15 14 13 12 11 10 9

H

Pin 1 Marking

E

1 2 3 4 5 6 78

A

SEATING

PLANE

B

SIDE VIEW

e

A1

END VIEW

C

L

Package Dimensions for QSOP-16

www.DataSheet4U.com

© 2002 California Micro Devices Corp. All rights reserved.

02/14/02 215 Topaz Street, Milpitas, California 95035 L Tel: (408) 263-3214 L Fax: (408) 263-7846 L www.calmicro.com

5

5 Page | ||

| Páginas | Total 5 Páginas | |

| PDF Descargar | [ Datasheet PACVGA100.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PACVGA100 | VGA Port ESD Protection and Termination Network | California Micro Devices |

| PACVGA101 | VGA Port ESD Protection and Termination Network | California Micro Devices |

| PACVGA105 | VGA Port Companion Circuit | California Micro Devices |

| PACVGA105 | VGA Port Companion Circuit | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |