|

|

PDF CY14E101J Data sheet ( Hoja de datos )

| Número de pieza | CY14E101J | |

| Descripción | 1-Mbit (128 K X 8) Serial (I2C) nvSRAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY14E101J (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CY14C101J

PRELIMINARY

CY14B101J, CY14E101J

1 Mbit (128 K × 8) Serial (I2C) nvSRAM

Features

■ 1-Mbit nonvolatile static random access memory (nvSRAM)

❐ Internally organized as 128 K × 8

❐ STORE to QuantumTrap nonvolatile elements initiated

automatically on power-down (AutoStore) or by using I2C

command (Software STORE) or HSB pin (Hardware STORE)

❐

RECALL

CALL) or

to

by

IS2CRAcMomimniatiantded(SoofntwpaoreweRrE-uCpA(LPLo)wer-Up

RE-

❐ Automatic STORE on power-down with a small capacitor (ex-

cept for CY14X101J1)

■ High reliability

❐ Infinite read, write, and RECALL cycles

❐ 1 million STORE cycles to QuantumTrap

❐ Data retention: 20 years at 85 °C

■ High speed I2C interface

❐ Industry standard 100 kHz and 400 kHz speed

❐ Fast-mode Plus: 1 MHz speed

❐ High speed: 3.4 MHz

❐ Zero cycle delay reads and writes

■ Write protection

❐ Hardware protection using Write Protect (WP) pin

❐ Software block protection for 1/4, 1/2, or entire array

■ I2C access to special functions

❐ Nonvolatile STORE/RECALL

❐ 8 byte serial number

❐ Manufacturer ID and Product ID

❐ Sleep mode

■ Industry standard configurations

❐ Operating voltages:

• CY14C101J: VCC = 2.4 V to 2.6 V

• CY14B101J: VCC = 2.7 V to 3.6 V

• CY14E101J: VCC = 4.5 V to 5.5 V

❐ Industrial temperature

❐ 8- and 16-pin small outline integrated circuit (SOIC) package

❐ Restriction of hazardous substances (RoHS) compliant

Overview

The Cypress CY14C101J/CY14B101J/CY14E101J combines a

1-Mbit nvSRAM[1] with a nonvolatile element in each memory

cell. The memory is organized as 128 K words of 8 bits each. The

embedded nonvolatile elements incorporate the QuantumTrap

technology, creating the world’s most reliable nonvolatile

memory. The SRAM provides infinite read and write cycles, while

the QuantumTrap cells provide highly reliable nonvolatile

storage of data. Data transfers from SRAM to the nonvolatile

elements (STORE operation) takes place automatically at

power-down (except for CY14X101J1). On power-up, data is

restored to the SRAM from the nonvolatile memory (RECALL

operation). The STORE and RECALL operations can also be

initiated by the user through I2C commands.

Configuration

Feature

AutoStore

Software

STORE

CY14X101J1

No

Yes

CY14X101J2

Yes

Yes

CY14X101J3

Yes

Yes

■ Low power consumption

Hardware

No

No

Yes

❐ Average active current of 1 mA at 3.4 MHz operation

STORE

❐ Average standby mode current of 150 uA

❐ Sleep mode current of 8 uA

Logic Block Diagram

VCC VCAP

Serial Number

8x8

Manufacture ID/

Product ID

Power Control

Block

Sleep

Memory Control Register

Command Register

Quantrum Trap

128 K x 8

www.DataSSDheAet4U.com 2

SCL I C Control Logic

A2, A1

Slave Address

Decoder

WP

Control Registers Slave

Memory Slave

Memory

Address and Data

Control

SRAM

128 K x 8

STORE

RECALL

Note

1. Serial (I2C) nvSRAM is referred to as nvSRAM throughout the datasheet.

Cypress Semiconductor Corporation • 198 Champion Court

Document #: 001-54050 Rev. *D

• San Jose, CA 95134-1709 • 408-943-2600

Revised January 19, 2011

[+] Feedback

1 page

PRELIMINARY

CY14C101J

CY14B101J, CY14E101J

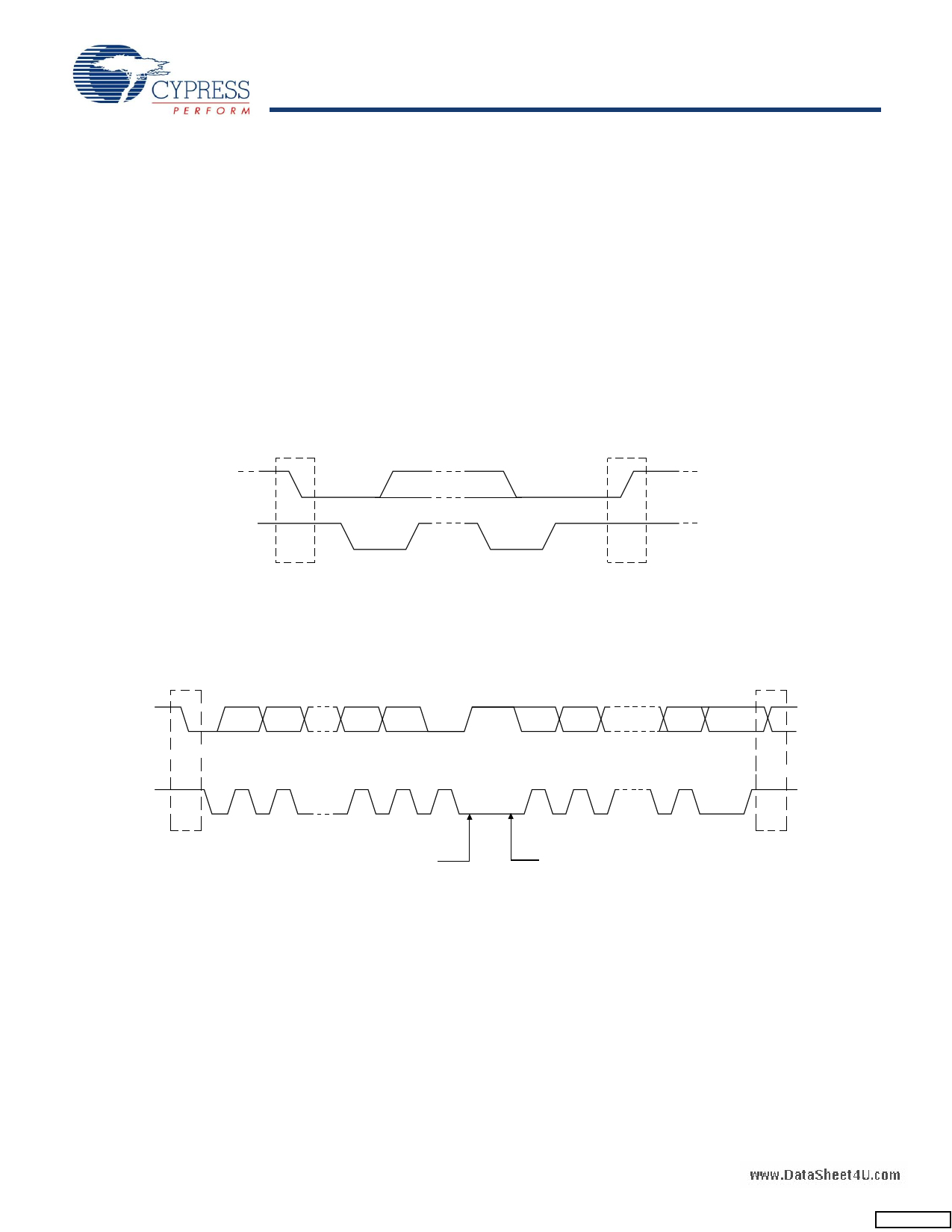

Data Validity

The data on the SDA line must be stable during the HIGH period

of the clock. The state of the data line can only change when the

clock on the SCL line is LOW for the data to be valid. There are

only two conditions under which the SDA line may change state

with SCL line held HIGH, that is, START and STOP condition.

The START and STOP conditions are generated by the master

to signal the beginning and end of a communication sequence

on the I2C bus.

START Condition (S)

A HIGH to LOW transition on the SDA line while SCL is HIGH

indicates a START condition. Every transaction in I2C begins

with the master generating a START condition.

STOP Condition (P)

A LOW to HIGH transition on the SDA line while SCL is HIGH

indicates a STOP condition. This condition indicates the end of

the ongoing transaction.

START and STOP conditions are always generated by the

master. The bus is considered to be busy after the START

condition. The bus is considered to be free again after the STOP

condition.

Repeated START (Sr)

If an Repeated START condition is generated instead of a Stop

condition the bus continues to be busy. The ongoing transaction

on the I2C lines is stopped and the bus waits for the master to

send a slave ID for communication to restart.

Figure 4. START and STOP Conditions

full pagewidth

SDA

SDA

SCL

S

START Condition

P

STOP Condition

SCL

handbook, full pagewidth

SDA

MSB

SCL

S

or

Sr

1

START or

Repeated START

condition

2

Figure 5. Data Transfer on the I2C Bus

Acknowledgement

signal from slave

P

Acknowledgement Sr

signal from receiver

789

ACK

Byte complete,

interrupt within slave

1 2 3-8 9

ACK

Clock line held LOW while

interrupts are serviced

Sr

or

P

STOP or

Repeated START

condition

Byte Format

Each operation in I2C is done using 8 bit words. The bits are sent in MSB first format on SDA line and each byte is followed by an

ACK signal by the receiver.

wwwASnD.DAoaptliaenSreahtmeioeunt4sUct or.ecnomtimnauinessttailbl lae

NACK is sent by the receiver or STOP or Repeated START

when the clock (SCL) is HIGH except for a START or STOP

condition

condition.

is

generated

by

the

master

The

Document #: 001-54050 Rev. *D

Page 5 of 32

[+] Feedback

5 Page

PRELIMINARY

CY14C101J

CY14B101J, CY14E101J

Figure 11. Single-Byte Write into nvSRAM (except Hs-mode)

By Master

SDA Line

By nvSRAM

S

T

A

R Memory Slave Address

T

S 1 0 1 0 A2 A1 A16 0

Address MSB

Address LSB

A AA

Figure 12. Multi-Byte Write into nvSRAM (except Hs-mode)

By Master

SDA Line

By nvSRAM

S

T

A

R Memory Slave Address

T

S 1 0 1 0 A2 A1 A16 0

Address MSB

Address LSB

Data Byte 1

A AA

Figure 13. Single-Byte Write into nvSRAM (Hs-mode)

A

Data Byte

S

T

0

P

P

A

Data Byte N

S

T

0

P

P

A

By Master

SDA Line

By nvSRAM

S

T

A

R Hs-mode command

T

S00 0 01 XX X

Memory Slave Address

Sr 1 0 1 0 A2 A1 A16 0

Address MSB

Address LSB

A AA

Figure 14. Multi-Byte Write into nvSRAM (Hs-mode)

A

Data Byte

S

T

0

P

P

A

By Master

SDA Line

By nvSRAM

S

T

A

R Hs-mode command

T

S00 0 01 XX X

Memory Slave Address

Sr 1 0 1 0 A2 A1 A16 0

AA

Address MSB

A

By Master

SDA Line

Data Byte 2

Data Byte 3

Data Byte N

Address LSB

S

T

0

P

P

A

Data Byte 1

A

wwwBy.DnvaSRtAaMSheet4U.com

A

A

Current nvSRAM Read

Each read operation starts with the master transmitting the

nvSRAM slave address with the LSB set to ‘1’ to indicate “Read”.

The reads start from the address on the address counter. The

address counter is set to the address location next to the last

accessed with a “Write” or “Read” operation. The master may

A

terminate a read operation after reading 1 byte or continue

reading addresses sequentially till the last address in the

memory after which the address counter rolls back to the

address 0x00000. The valid methods of terminating read access

are described in Section “Read Operation” on page 10.

Note A16-bit is ignored while using the current nvSRAM read.

Document #: 001-54050 Rev. *D

Page 11 of 32

[+] Feedback

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CY14E101J.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY14E101I | 1 Mbit (128K x 8) Serial (I2C) nvSRAM | Cypress Semiconductor |

| CY14E101I | 1-Mbit (128 K X 8) Serial (I2C) nvSRAM | Cypress Semiconductor |

| CY14E101J | 1-Mbit (128 K X 8) Serial (I2C) nvSRAM | Cypress Semiconductor |

| CY14E101PA | 1-Mbit (128 K X 8) Serial (SPI) nvSRAM | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |