|

|

PDF K7K3236U2C Data sheet ( Hoja de datos )

| Número de pieza | K7K3236U2C | |

| Descripción | 1Mx36 & 2Mx18 DDRII CIO b2 SRAM | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K7K3236U2C (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

K7K3236U2C

K7K3218U2C

1Mx36 & 2Mx18 DDRII+ CIO b2 SRAM

36Mb DDRII+ SRAM Specification

165 FBGA with Pb & Pb-Free

(RoHS compliant)

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,

AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY.

ALL INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or simi-

lar applications where Product failure couldresult in loss of life or personal or physical harm, or any military

or defense application, or any governmental procurement to which special terms or provisions may apply.

* Samsung Electronics reserves the right to change products or specification without notice.

www.DataSheet4U.com

- 1 - Rev. 1.0 August 2008

1 page

K7K3236U2C

K7K3218U2C

1Mx36 & 2Mx18 DDRII+ CIO b2 SRAM

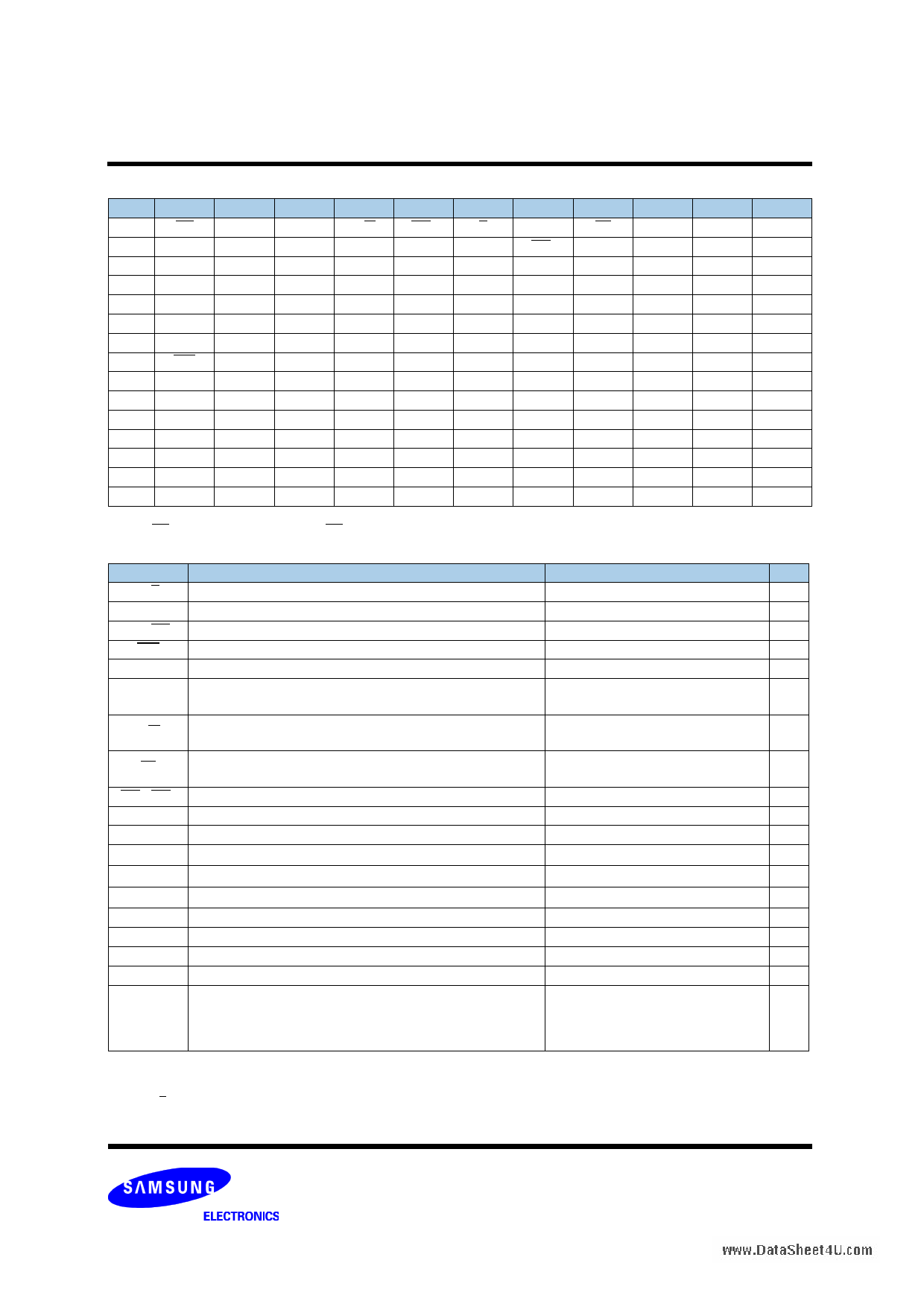

PIN CONFIGURATIONS(TOP VIEW) K7K3218T2C(2Mx18)

1 2 3 4 5 6 7 8 9 10 11

A

CQ NC/SA* SA

R/W

BW1

K

NC LD SA SA CQ

B NC DQ9 NC SA NC

K

BW0

SA

NC

NC DQ8

C NC NC NC VSS SA NC SA VSS NC DQ7 NC

D NC NC DQ10 VSS VSS VSS VSS VSS NC NC NC

E NC

NC

DQ11

VDDQ

VSS

VSS

VSS VDDQ NC

NC DQ6

F

NC DQ12 NC VDDQ VDD

VSS

VDD

VDDQ

NC

NC DQ5

G NC

NC

DQ13

VDDQ

VDD

VSS

VDD

VDDQ

NC

NC

NC

H

Doff

VREF

VDDQ

VDDQ

VDD

VSS

VDD

VDDQ

VDDQ

VREF

ZQ

J

NC

NC

NC VDDQ VDD

VSS

VDD

VDDQ

NC

DQ4

NC

K NC

NC

DQ14

VDDQ

VDD

VSS

VDD

VDDQ

NC

NC DQ3

L NC DQ15 NC VDDQ VSS VSS VSS VDDQ NC NC DQ2

M NC

NC

NC

VSS

VSS

VSS

VSS

VSS

NC DQ1 NC

N NC NC DQ16 VSS SA SA SA VSS NC NC NC

P NC NC DQ17 SA SA QVLD SA SA NC NC DQ0

R TDO TCK

SA

SA

SA

NC

SA

SA

SA TMS TDI

Notes: 1. * Checked No Connect(NC) pins are reserved for higher density address, i.e. 2A for 72Mb.

2. BW0 controls write to DQ0:DQ8 and BW1 controls write to DQ9:DQ17.

PIN NAME

SYMBOL

K, K

QVLD

CQ, CQ

Doff

SA

DQ0-17

R/W

LD

BW0, BW1

VREF

ZQ

VDD

VDDQ

VSS

TMS

TDI

TCK

TDO

NC

PIN NUMBERS

6B, 6A

6P

11A, 1A

1H

3A,9A,10A,4B,8B,5C,7C,5N-7N,4P,5P,7P,8P,3R-5R,7R-9R

2B,11B,10C,3D,3E,11E,2F,11F,3G,10J,3K,11K,2L,11L

10M,3N,3P,11P

4A

8A

7B, 5A

2H,10H

11H

5F,7F,5G,7G,5H,7H,5J,7J,5K,7K

4E,8E,4F,8F,4G,8G,3H,4H,8H,9H,4J,8J,4K,8K,4L,8L

4C,8C,4D-8D,5E-7E,6F,6G,6H,6J,6K,5L-7L,4M-8M,4N,8N

10R

11R

2R

1R

2A,7A,1B,3B,5B,9B,10B,1C,2C,3C,6C,9C,11C,1D,2D,9D,10D

11D,1E,2E,9E,10E,1F,3F,9F,10F,1G,2G,9G,10G,11G

1J,2J,3J,9J,11J,1K,2K,9K,10K,1L,3L,9L,10L

1M,2M,3M,9M,11M,1N,2N,9N,10N,11N,1P,2P,9P,10P,6R

DESCRIPTION

Input Clock

Q Valid output

Output Echo Clock

DLL Disable

Address Inputs

Data Inputs Outputs

NOTE

Read, Write Control Pin, Read active

when high

Synchronous Load Pin, bus Cycle

sequence is to be defined when low

Block Write Control Pin,active when low

Input Reference Voltage

Output Driver Impedance Control Input

Power Supply ( 1.8 V )

Output Power Supply ( 1.5V )

Ground

JTAG Test Mode Select

JTAG Test Data Input

JTAG Test Clock

JTAG Test Data Output

1

No Connect

2

Notes:

www.DataShe1e.tW4Uhe.ncoZmQ pin is directly connected to VDD output impedance is set to minimum value and it cannot be connected to ground or left unconnected.

2. Not connected to chip pad internally.

3. K, K can not be set to VREF voltage.

- 5 - Rev. 1.0 August 2008

5 Page

K7K3236U2C

K7K3218U2C

1Mx36 & 2Mx18 DDRII+ CIO b2 SRAM

DC ELECTRICAL CHARACTERISTICS (VDD=1.8V ±0.1V, TA=0°C to +70°C)

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

MAX

UNIT NOTES

Input Leakage Current

IIL VDD=Max ; VIN=VSS to VDDQ

-2 +2 µA

Output Leakage Current

IOL Output Disabled,

-2 +2 µA

Operating Current (x36): DDR

ICC

VDD=Max , IOUT=0mA

Cycle Time ≥ tKHKH Min

-45 -

-40 -

-33 -

950

900 mA 1,4

800

Operating Current (x18): DDR

ICC

VDD=Max , IOUT=0mA

Cycle Time ≥ tKHKH Min

-45 -

-40 -

-33 -

850

900 mA 1,4

700

Standby Current(NOP): DDR

-45

Device deselected, IOUT=0mA, f=Max,

ISB1 All Inputs≤0.2V or ≥ VDD-0.2V

-40

-33

-

-

-

400

350 mA 1,5

300

Output High Voltage

VOH1

VDDQ/2-0.12 VDDQ/2+0.12 V

2,6

Output Low Voltage

VOL1

VDDQ/2-0.12 VDDQ/2+0.12 V

2,6

Output High Voltage

VOH2 IOH=-1.0mA

VDDQ-0.2

VDDQ

V3

Output Low Voltage

VOL2 IOL=1.0mA

VSS 0.2 V 3

Notes: 1. Minimum cycle. IOUT=0mA.

2. |IOH|=(VDDQ/2)/(RQ/5)±15% for 175Ω ≤ RQ ≤ 350Ω. |IOL|=(VDDQ/2)/(RQ/5)±15% for 175Ω ≤ RQ ≤ 350Ω.

3. Minimum Impedance Mode when ZQ pin is connected to VDD.

4. Operating current is calculated with 100% read cycles or 100% write cycles.

5. Standby Current is only after all pending read and write burst opeactions are completed.

6. Programmable Impedance Mode.

www.DataSheet4U.com

- 11 - Rev. 1.0 August 2008

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet K7K3236U2C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K7K3236U2C | 1Mx36 & 2Mx18 DDRII CIO b2 SRAM | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |